SLUAA11B February 2020 – August 2021 BQ769142 , BQ76922 , BQ76942 , BQ76952

- Trademarks

- 1Direct Commands

- 2Subcommands

- 3Reading and Writing RAM Registers

- 4I2C With CRC

-

5SPI

With

CRC Examples

- 5.1 Direct Command Example: Alarm Enable - 0x66

- 5.2 Direct Command Example: Cell 1 Voltage - 0x14

- 5.3 Subcommand Example: Device Number - 0x0001

- 5.4 Subcommand Example: FET_ENABLE - 0x0022

- 5.5 Subcommand Example: RESET - 0x0012

- 5.6 RAM Register Read Example: Enabled Protections A

- 5.7 RAM Register Write Example: Enabled Protections A

- 6Simple Code Examples

- 7References

- 8Revision History

1.1 Alarm Enable - 0x66

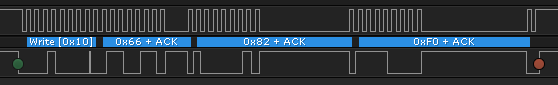

Table 1-1 shows the Alarm Enable command that uses command 0x66. By default, the register setting for Alarm Enable is set to 0xF800. In the example, the setting is changed to 0xF082. The data is in little endian format. The device address for the BQ769x2 is 0x10 (8-bits) where the LSB is the R/W bit. A direct command follows the format I2C_Write(I2C_ADDR, Command, DataBlock), so for this example the command would be I2C_Write(0x10, 0x66, [0x82, 0xF0]).

Table 1-1 Alarm Enable Command

Description

| Command | Name | Units | Type | Description |

|---|---|---|---|---|

| 0x66 | Alarm Enable | Hex | H2 | Mask for Alarm Status(). Can be written to change during operation to change which alarm sources are enabled. |

Figure 1-1 Captured I2C Waveform for

Setting Alarm Enable to 0xF082

Figure 1-1 Captured I2C Waveform for

Setting Alarm Enable to 0xF082