SLUUCF7 April 2021 BQ25960

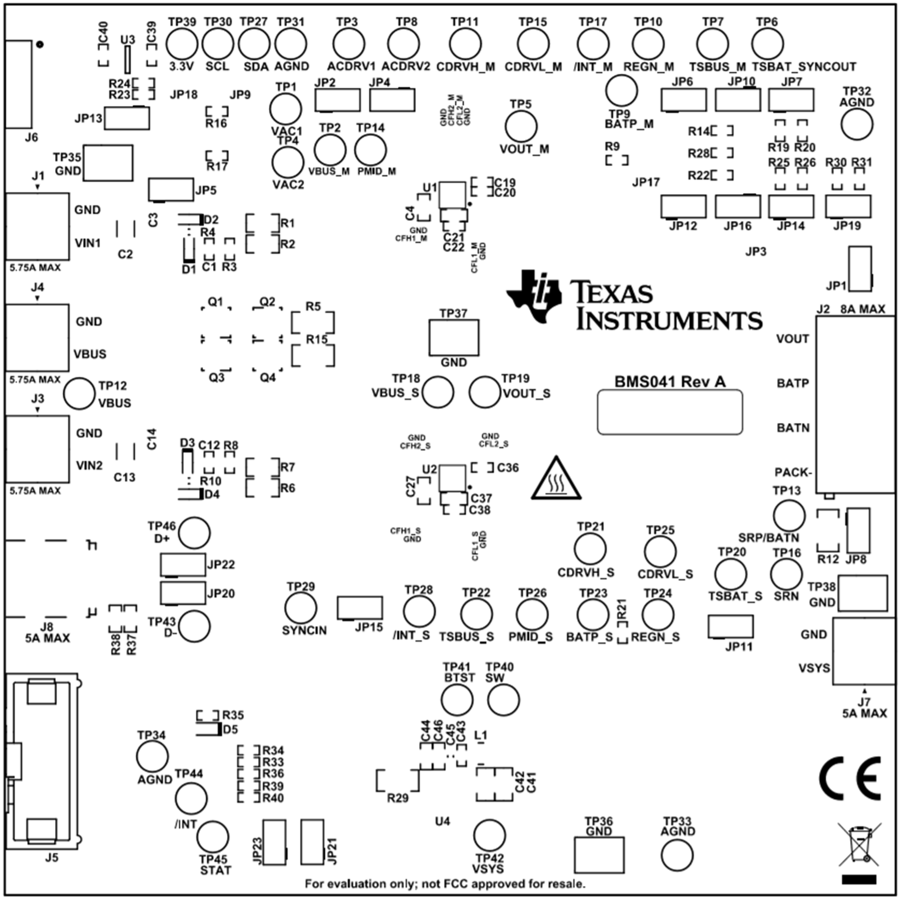

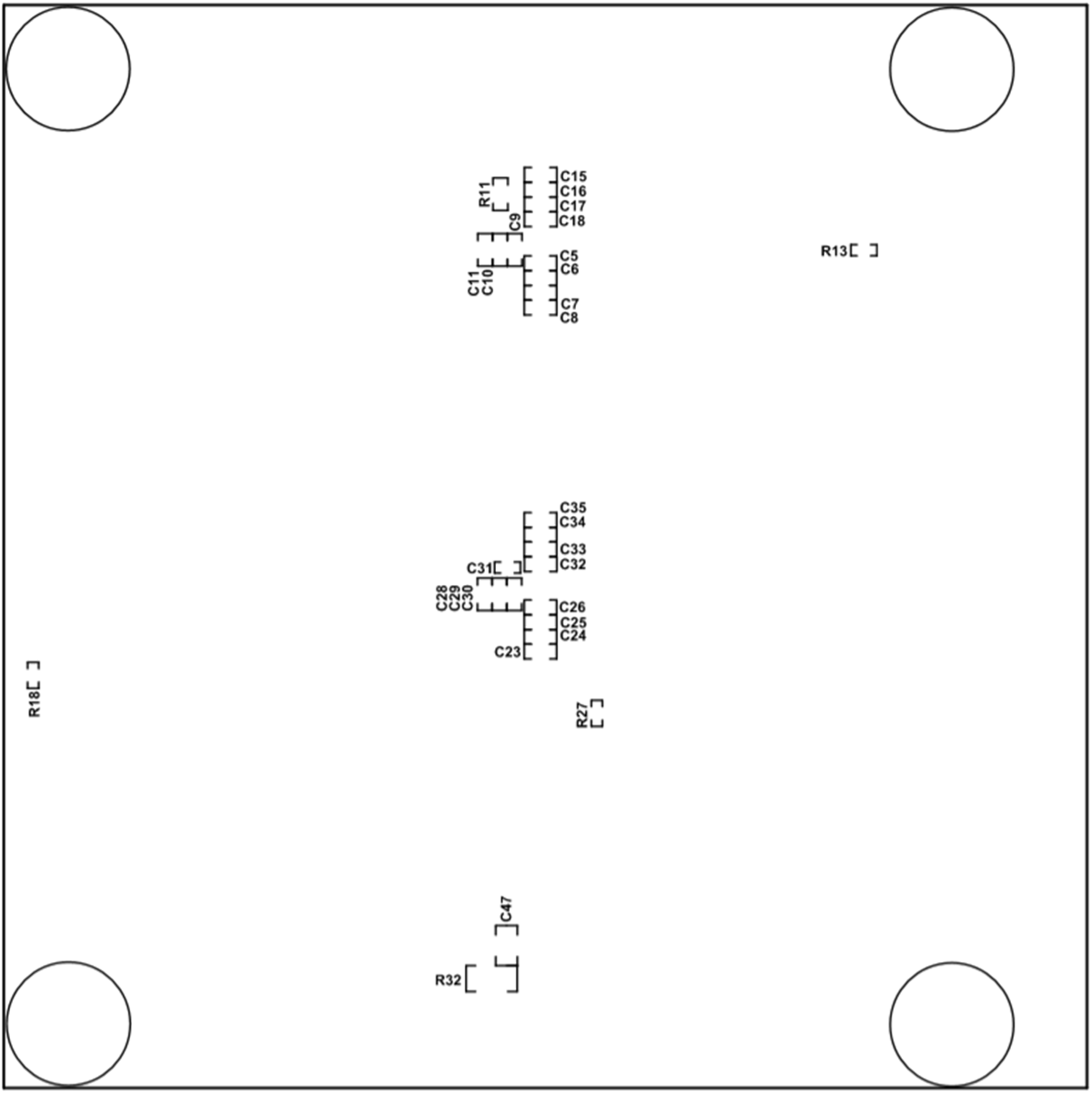

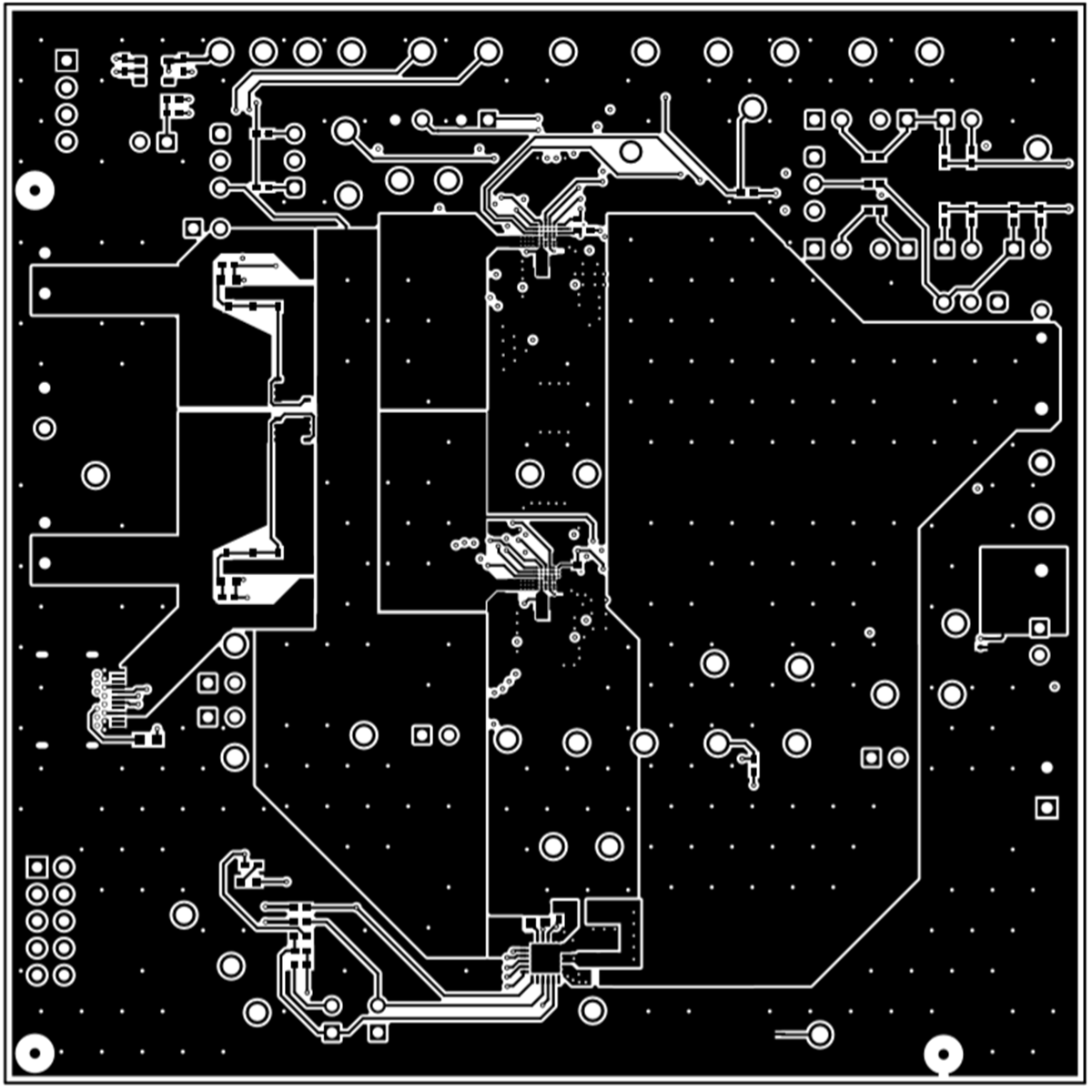

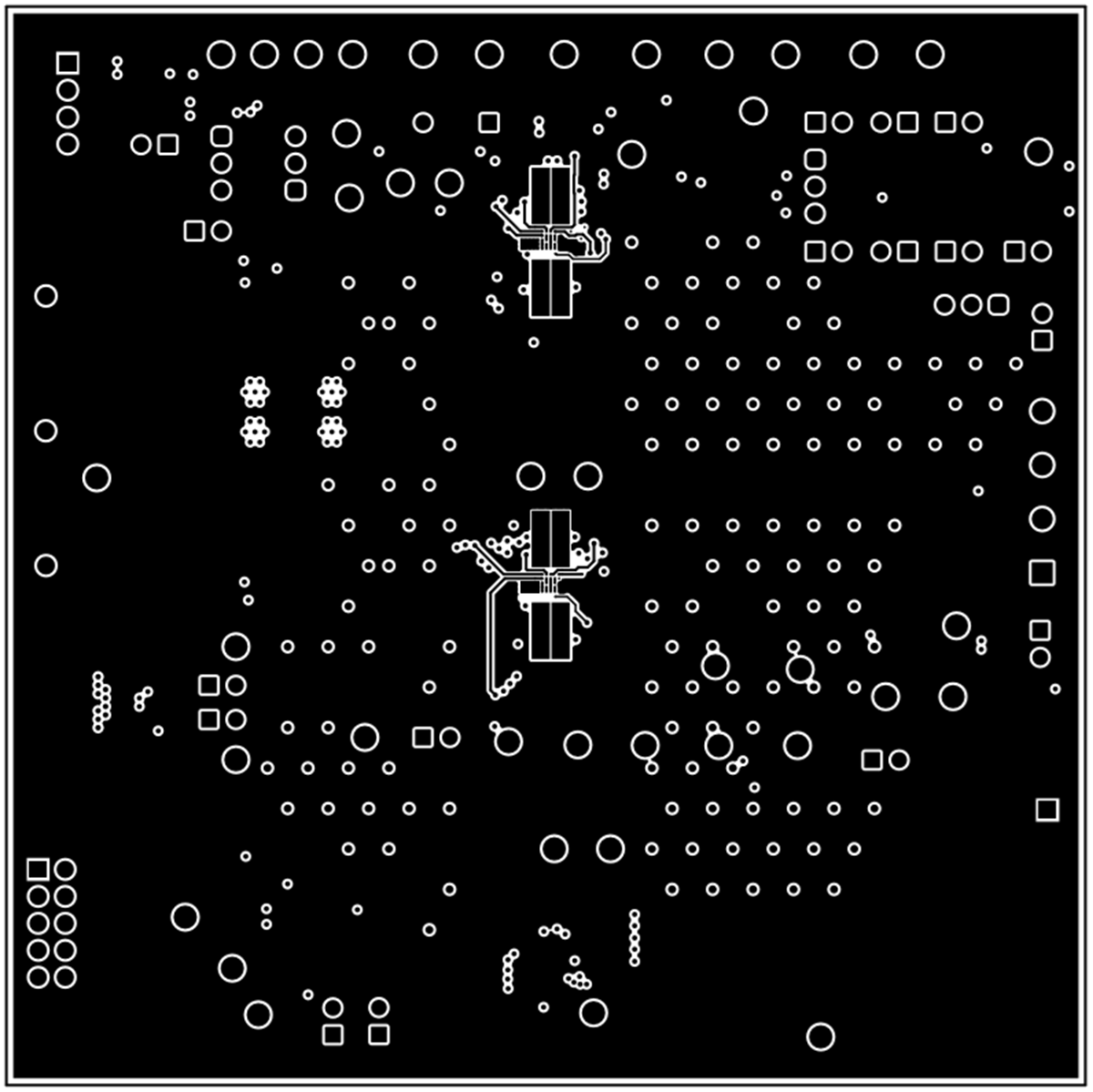

4.1 Board Layout

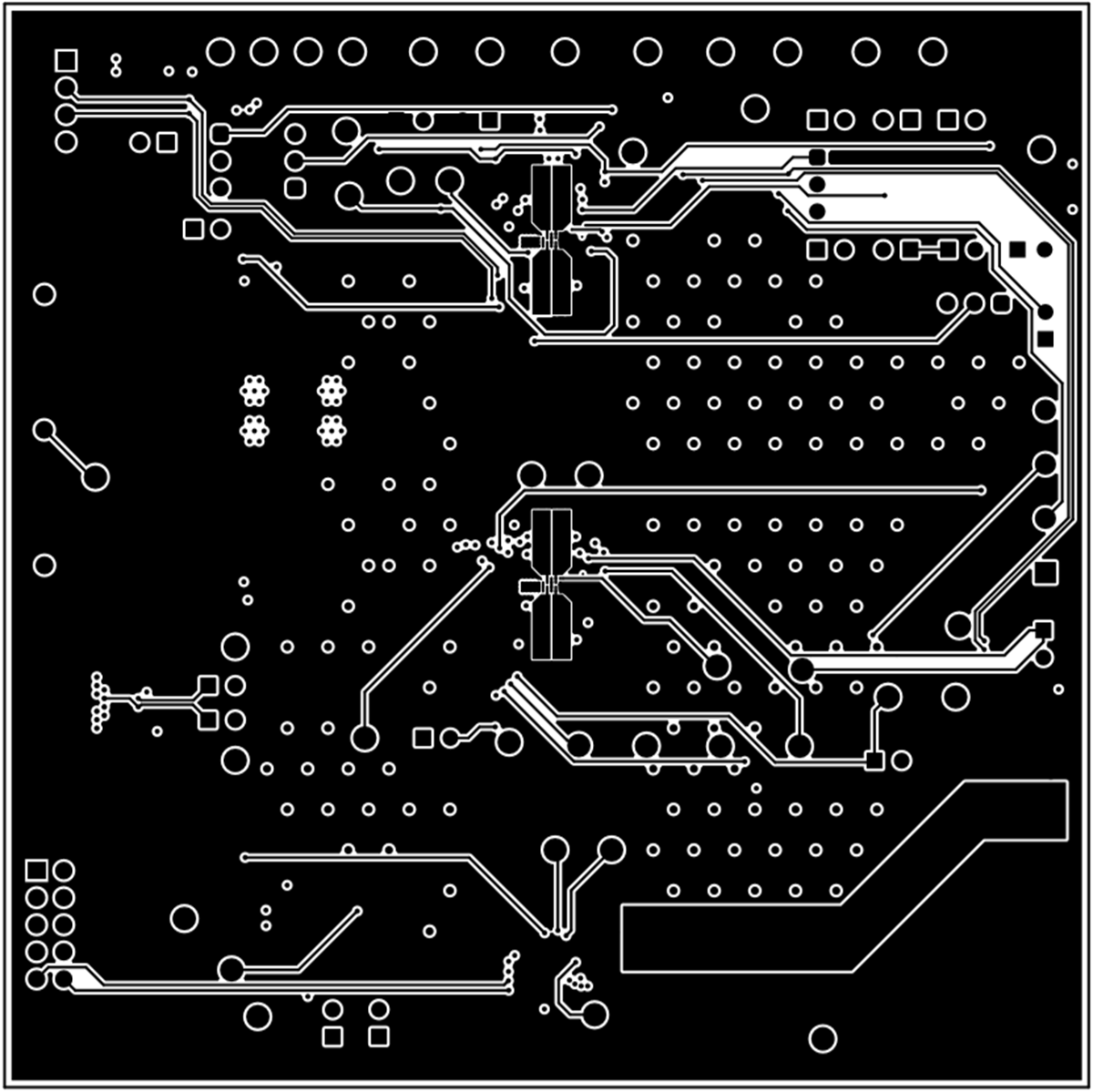

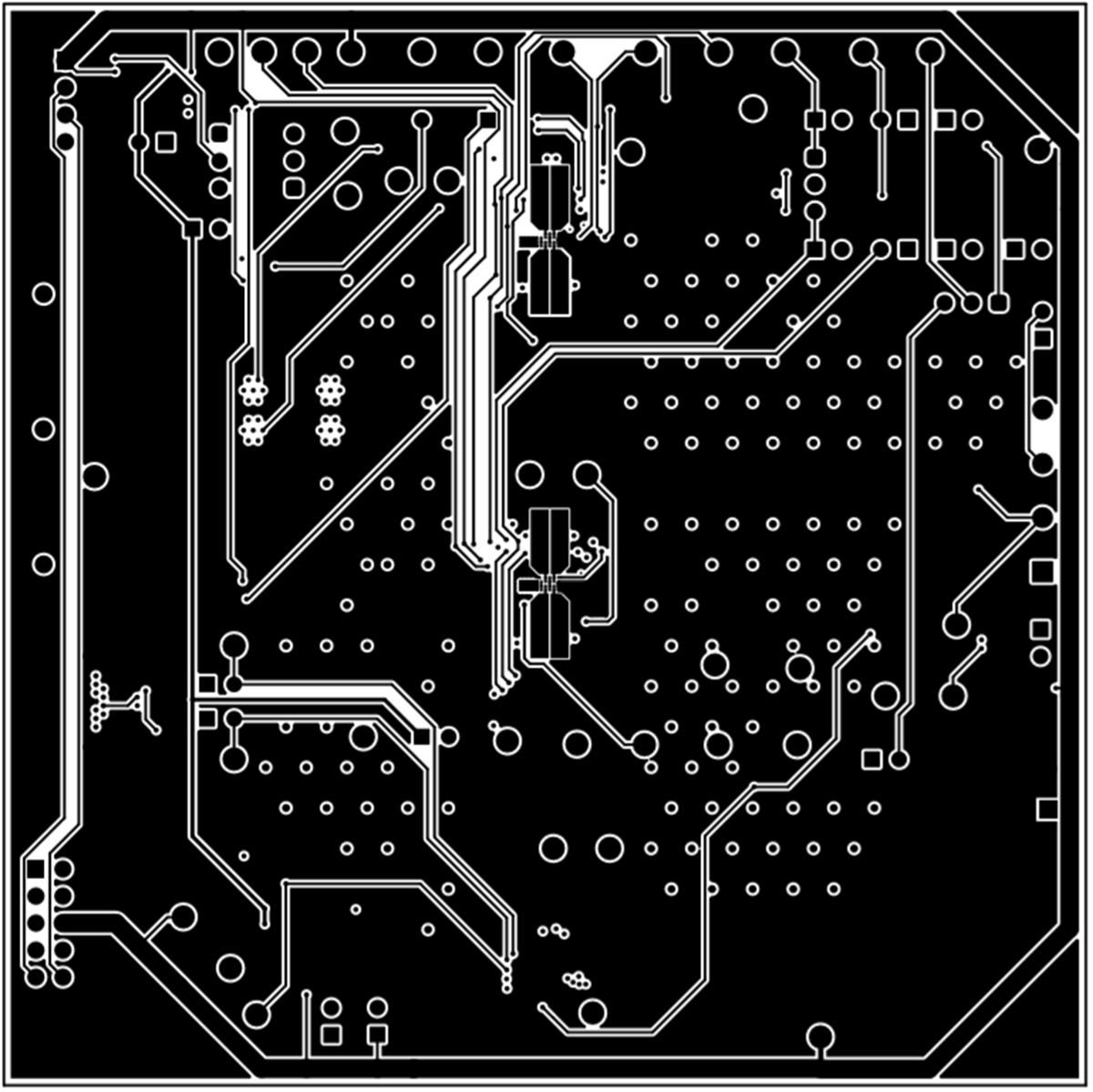

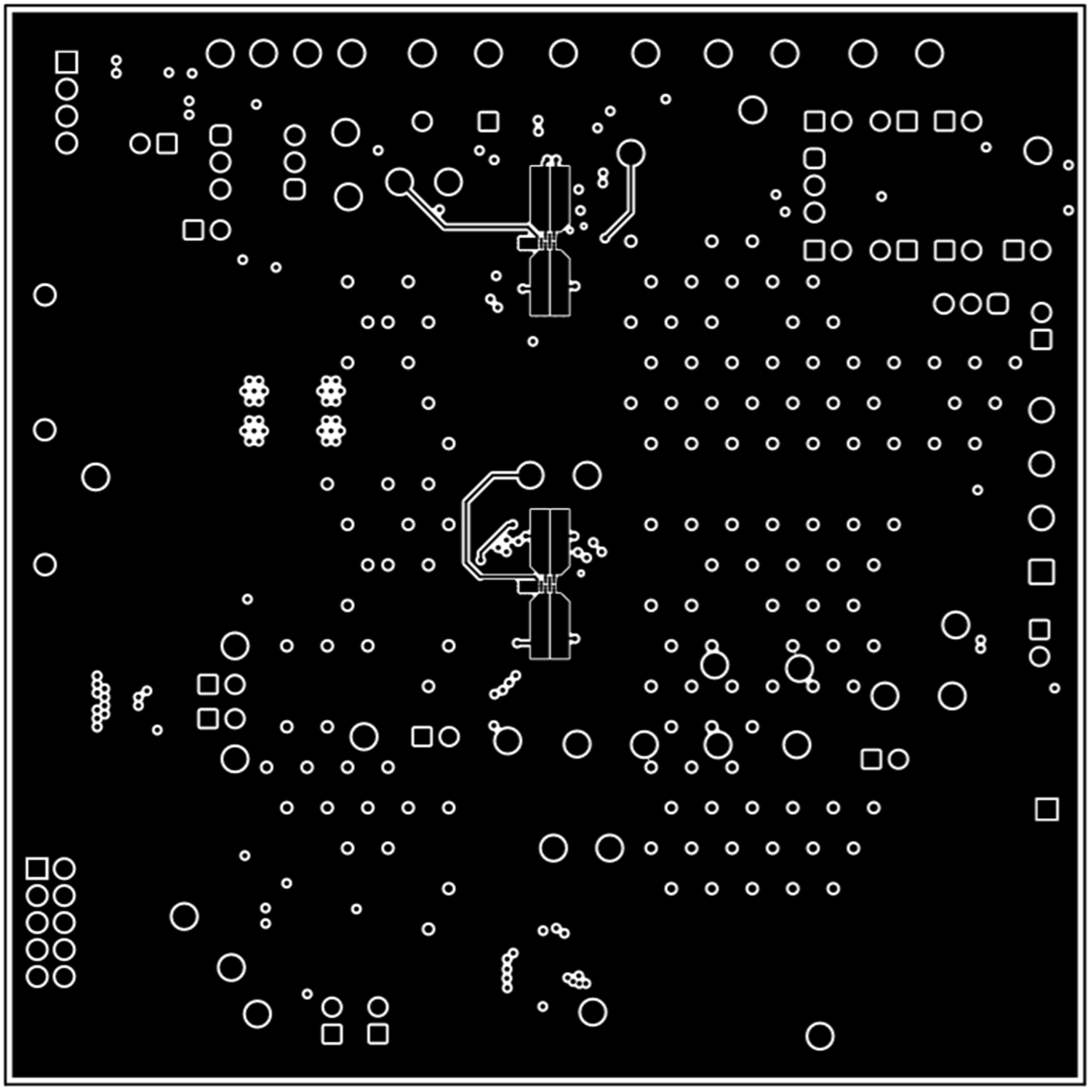

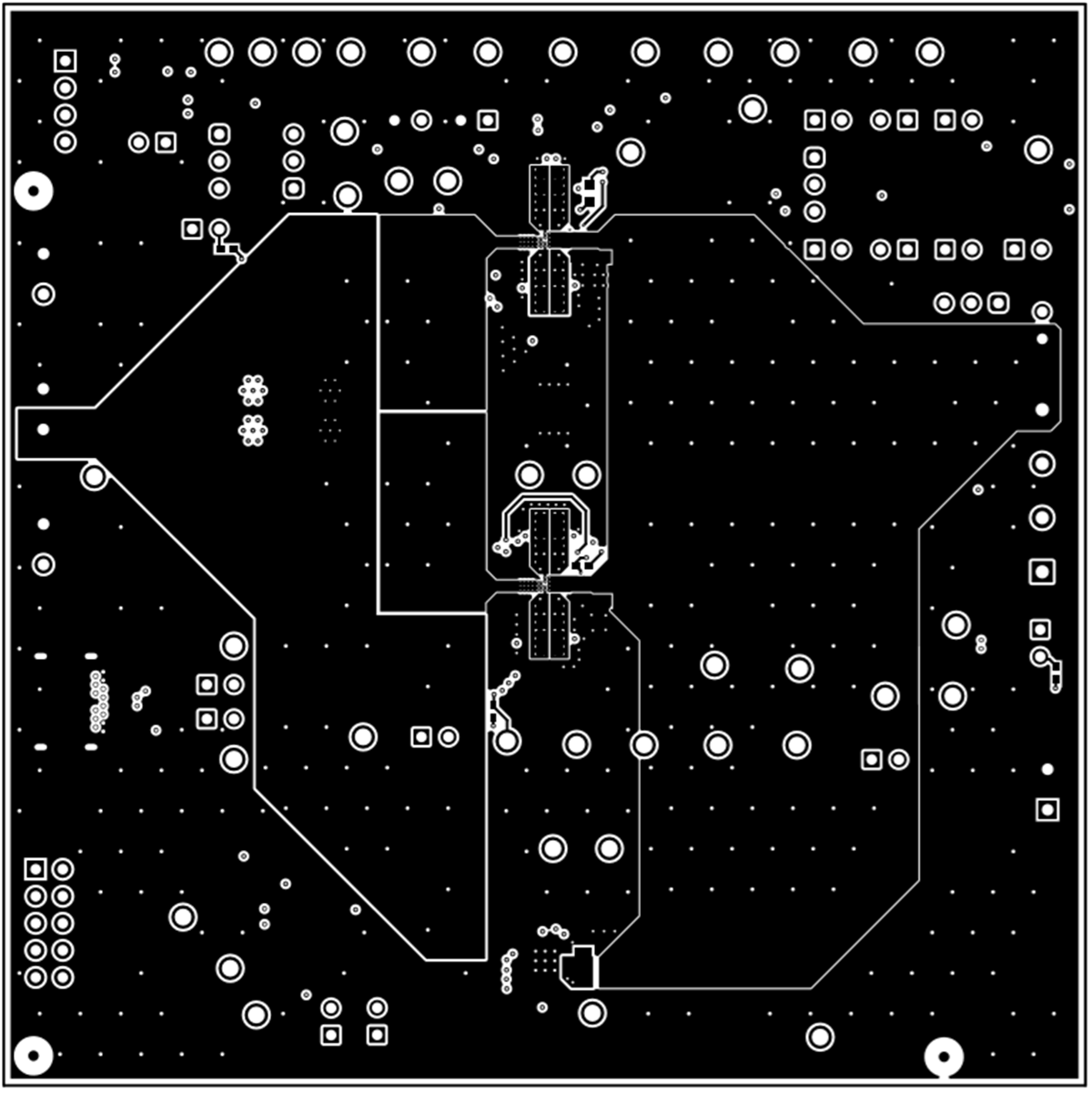

Figure 4-1 through Figure 4-8 illustrate the PCB layout.

Figure 4-1 BMS041 Top Overlay

Figure 4-2 BMS041 Bottom Overlay

Figure 4-3 BMS041 Top Layer

Figure 4-4 BMS041 Signal Layer 1

Figure 4-5 BMS041 Signal Layer 2

Figure 4-6 BMS041 Signal Layer 3

Figure 4-7 BMS041 Signal Layer 4

Figure 4-8 BMS041 Bottom Layer