SNVA484B October 2011 – March 2024 LM5113

3.1 Performance Characteristics

Figure 4-1 shows the efficiency of the LM5113 evaluation board at different input voltage and the load current. 30ns dead time between HI and LI input of the LM5113 is selected to eliminate the shoot through while achieving high efficiency.

Figure 3-1 Evaluation Board Efficiency

vs. Load Current

Figure 3-1 Evaluation Board Efficiency

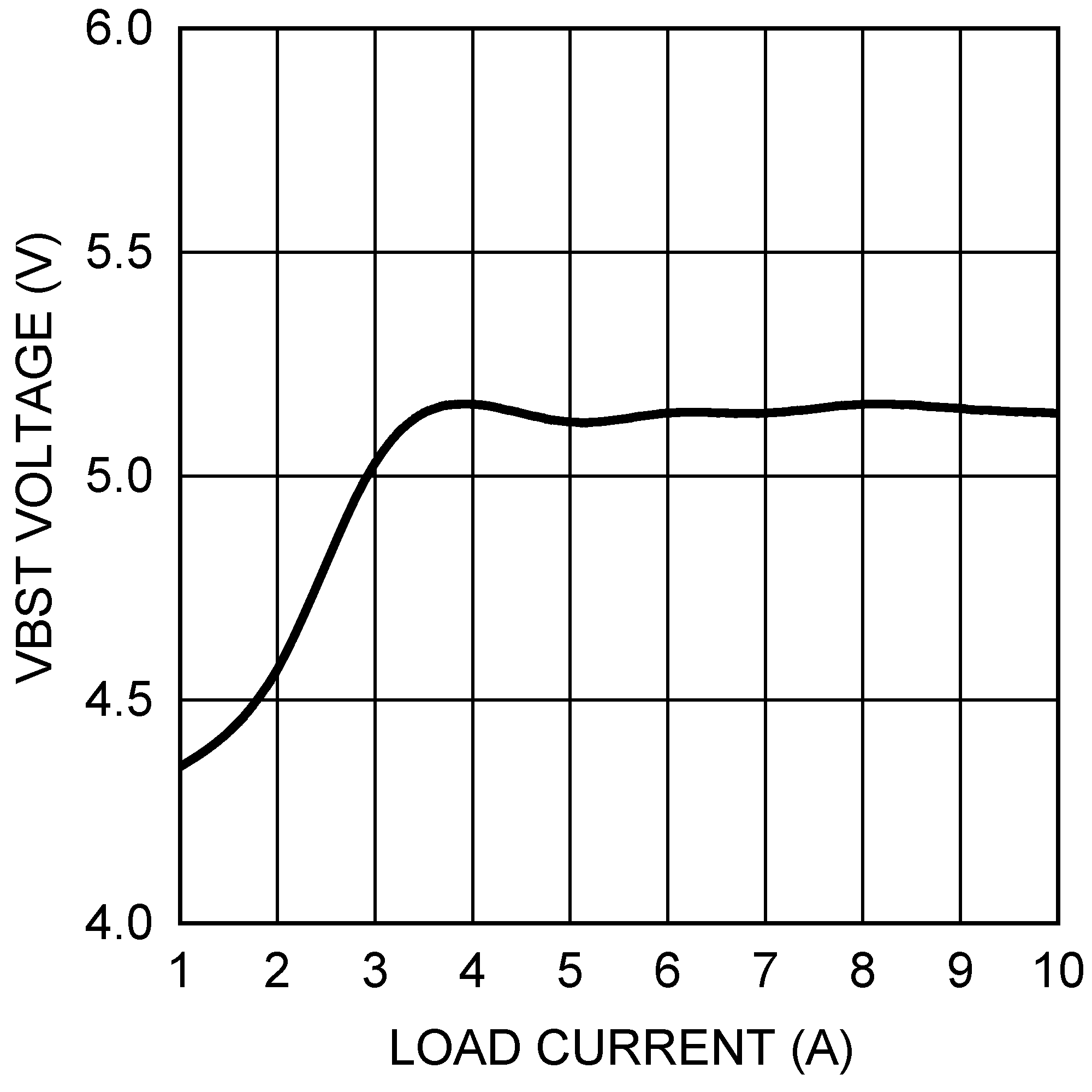

vs. Load CurrentDuring the dead time, the HS pin voltage can be pulled down below -0.7V and results in an excessive bootstrap voltage. The LM5113 has an internal clamping circuitry that prevents the bootstrap voltage from exceeding 5.25V typically. Figure 4-2 shows the average of the bootstrap voltage with the different load current. As can be seen, the bootstrap voltage is well regulated.

Figure 3-2 Bootstrap Voltage Regulation

vs. Load Current

Figure 3-2 Bootstrap Voltage Regulation

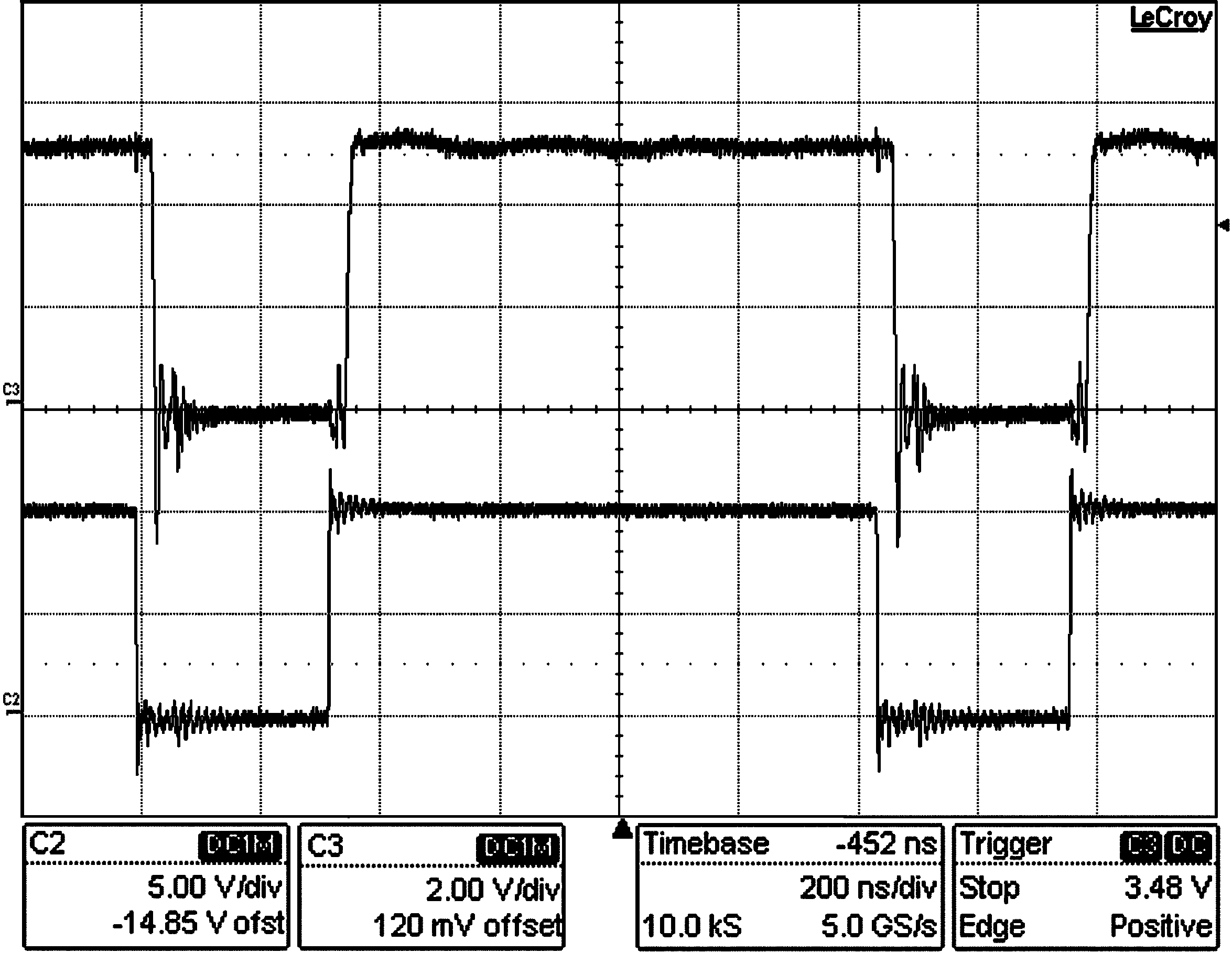

vs. Load CurrentFigure 4-3 compares the input and the output of the low-side driver.

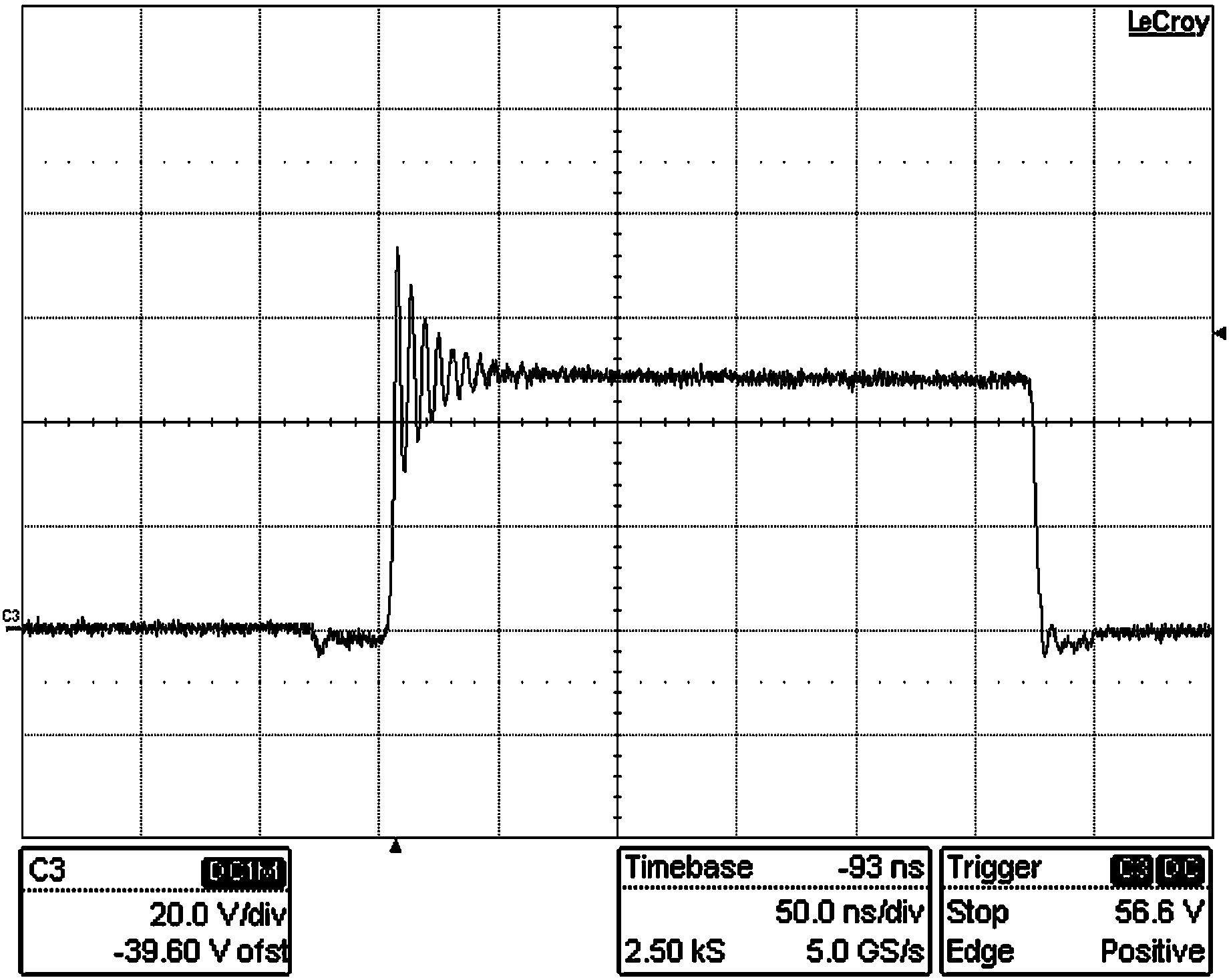

Figure 4-4 shows the switch node voltage that is also the drain voltage of the low-side FET. The ringing on the switch node voltage can be reduced by the HOH gate resistor. 2Ω HOH gate resistance is selected to achieve a drain-source voltage margin of 12V for a 60V input.

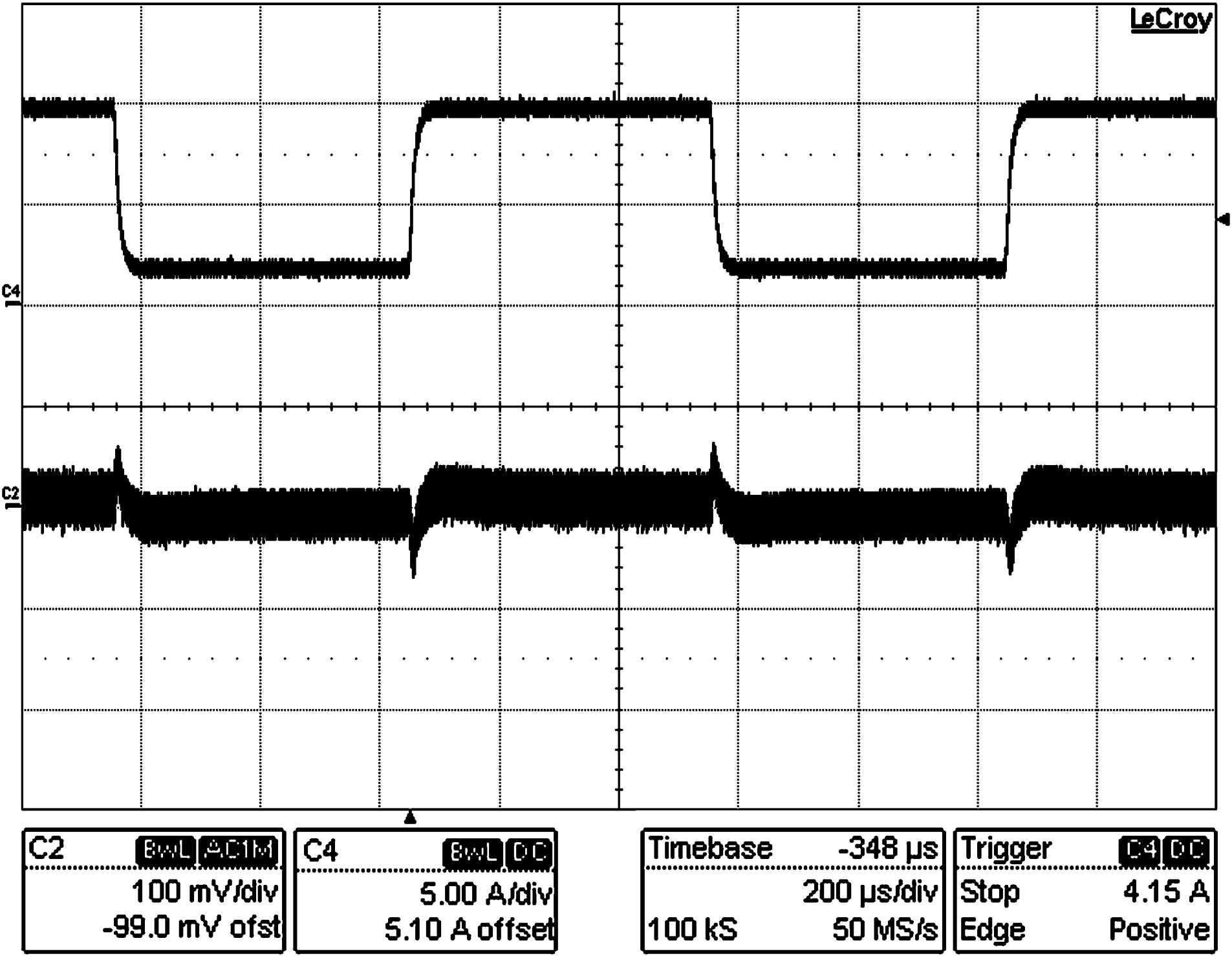

Figure 4-5 shows the load transient response. The load changes between 2A and 10A. 800kHz switching frequency allows the use of a small inductor of 2.7uH, which helps improve the large signal transient response.

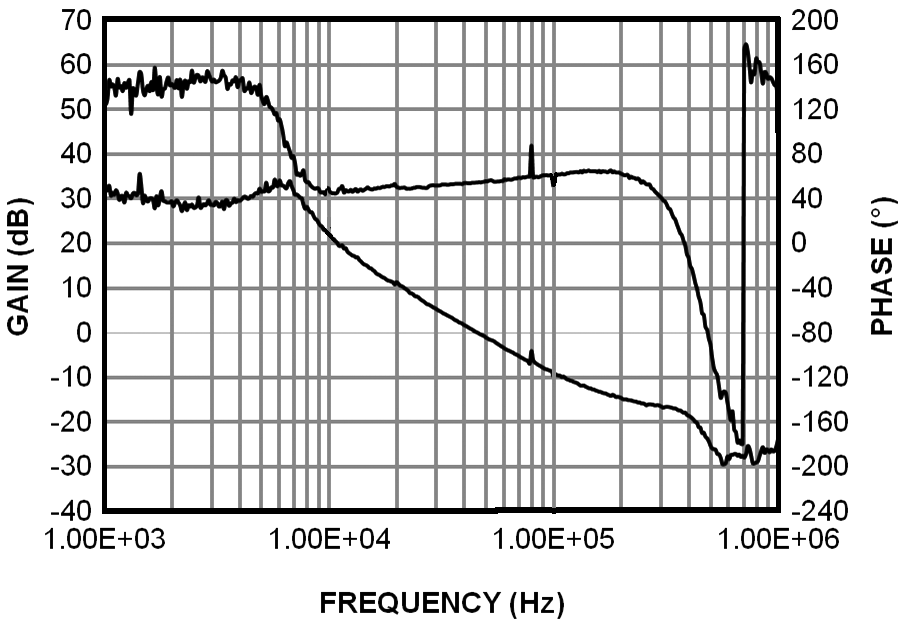

Figure 4-6 shows the measured overall loop response. The crossover frequency is 46kHz and the phase margin is around 55°.