SPRACV2 November 2020 AWR1843 , AWR2243

- Trademarks

- 1Introduction

- 2Cascade Incoherence Sources and Mitigation Strategies

-

3Enabling Cascade Coherence and Improved Phase

Performance

- 3.1 High-Level Summary

- 3.2 Saving RF INIT Calibration Results at Customer Factory

- 3.3 Corner Reflector-Based Offsets Measurement at Customer Factory

- 3.4 Restoring Customer Calibration Results In-Field

- 3.5

Host-Based Temperature Calibrations

In-Field

- 3.5.1 Disabling AWR Devices’ Autonomous Run Time Calibrations

- 3.5.2 Enabling Host-Based Temperature Calibrations of Inter-Channel Imbalances

- 3.5.3 Switching of DSP Imbalance Data

- 3.5.4

Enabling TX Phase Shifter’s Host-Based

Temperature Calibrations

- 3.5.4.1 Estimating TX Phase Shift Values at Any Temperature

- 3.5.4.2 Temperature Correction LUTs for AWR1843TX Phase Shifter

- 3.5.4.3 Temperature Correction LUTs for AWR2243 TX Phase Shifter

- 3.5.4.4 Restoring TX Phase Shift Values – Format Conversion

- 3.5.4.5 Restoring TX Phase Shift Values – Transition Timing and Constraints

- 3.5.4.6 Typical Post-Calibration TX Phase Shifter Accuracies

- 3.5.4.7 Correcting for Temperature Drift While Sweeping Across Phase Settings

- 3.5.4.8 Amplitude Stability Across Phase Shifter Settings

- 3.5.4.9 Impact of Customer PCB’s 20-GHz Sync Path Attenuation on TX Phase Shifters

- 3.5.5 Ambient and Device Temperatures

- 4Concept Illustrations

- 5Miscellaneous (Interference, Gain Variation, Sampling Jitter)

- 6Conclusion

- A Appendix

3.5.4.2 Temperature Correction LUTs for AWR1843TX Phase Shifter

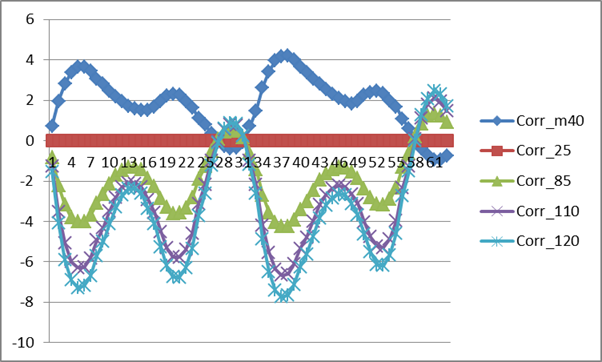

Assuming that Tfactory = 25C, Temperature Correction LUT (Tpresent) at Tpresent = -40C, 25C, 85C, 130C for AWR1843 is provided in Table 7 in the Appendix. The same is represented in the form of a graph in Figure 3-3. These are derived from evaluation of a few nominal process based devices in TI labs. The LUT for any temperature is indexed with 0 to 63, corresponding to the 6 bit phase shift index and the output is the correction in the phase angle that is needed. linear interpolation/extrapolation over these temperatures can be used for other temperatures if needed. The data shown below is measured with a single TX been ON at a time. If multiple TXs are ON at the same time the Tx-Tx antenna coupling could cause secondary impact on phase.

Figure 3-3 Temperature

Correction of TX Phase Shift Error for AWR1843 1

Figure 3-3 Temperature

Correction of TX Phase Shift Error for AWR1843 1- Assuming 25C customer factory calibration, y-axis is phase error in degrees, x-axis is phase shift.