SCEA143 December 2023 SN74AVC8T245 , SN74AVC8T245-Q1 , SN74AXC8T245 , SN74AXC8T245-Q1 , TXV0106 , TXV0106-Q1 , TXV0108 , TXV0108-Q1

3.3 Leveraging TXV for Buffering

| Parameter | TXV0108 (ns) | Competitor (ps) | TXV RGMII Margin | Comp RGMII Margin |

|---|---|---|---|---|

| 10 pF Skewrf / Skewfr | 164 / 61 | 39 / 257 | 67 % better than spec | 49 % better than spec |

| 10 pF Rise/Fall Time | 698/ 534 | 900 / 833 | 10 % better than spec | 20 % worst than spec |

| 15 pF Skewrf / Skewfr | 53 / 181 | 195 / 93 | 64 % better than spec | 61 % better than spec |

| 15 pF Rise/Fall Time | 752 / 652 | 1200 / 1300 | 0.3 % worst than spec | 73 % worst than spec |

- Table 3-5 shows rise-to-fall and fall-to-rise skew data collected using a pseudo-random binary sequence (PRBS) signal generator due to the difficulty / randomness to predict, further highlighting worst timing margins observed on bench, for high performance interfaces during random conditions with increased load.

As mentioned, skew between MAC and PHY can lead to data errors and performance issues. Today, complex systems tend to use connectors or longer traces in designing printed circuit boards (PCB), incorporating additional parasitic capacitance. Choosing the correct level-shifter for buffering, can increase the chances of overcoming such design challenges between the hosts or peripherals.

RGMII standard assumes 5 pF loading conditions for the interface's I/O, and can increase as design complexities increases with additional parasitic capacitance. Designers can use TXV for buffering more than the assumed standard load condition to support RGMII’s timing conditions for data and clock signals.

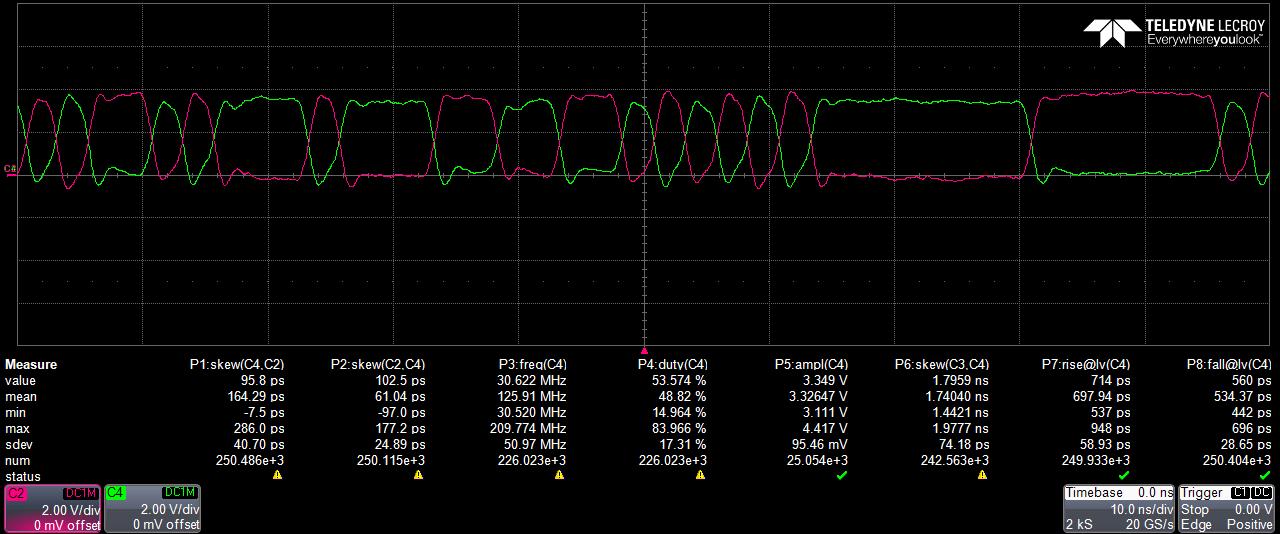

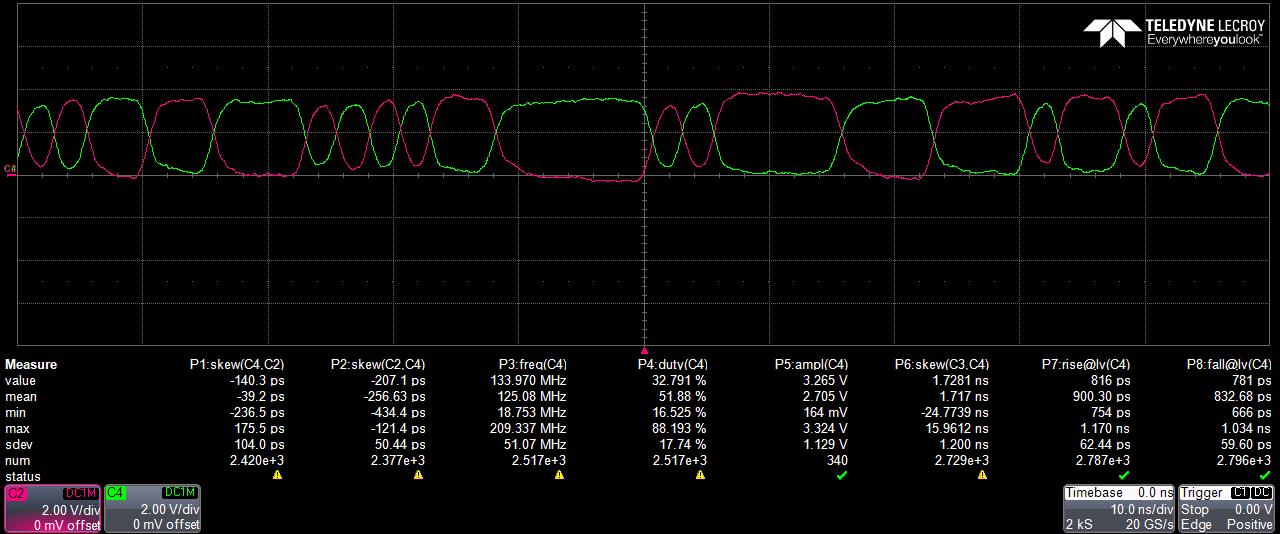

- For 10 pF, Figure 3-11 shows TXV outputs (measuring PRBS rise-to-fall skew of 164 ps and fall-to-rise skew of 61 ps) vs competitor (measuring 39 ps and 257 ps respectively). For fall or rise times, TXV (measured 698 or 534 ps) vs competitor (measuring approximately 2x slower rise or fall times >750 ps), violating RGMII requirement as shown in Figure 3-10.

Figure 3-5 TXV Outputs (10 pF 1.8 V to 3.3 V Up Translation at 125 MHz, 25°C)

Figure 3-5 TXV Outputs (10 pF 1.8 V to 3.3 V Up Translation at 125 MHz, 25°C) Figure 3-6 Competitor Outputs (10 pF 1.8 V to 3.3 V Up Translation at 125 MHz, 25°C)

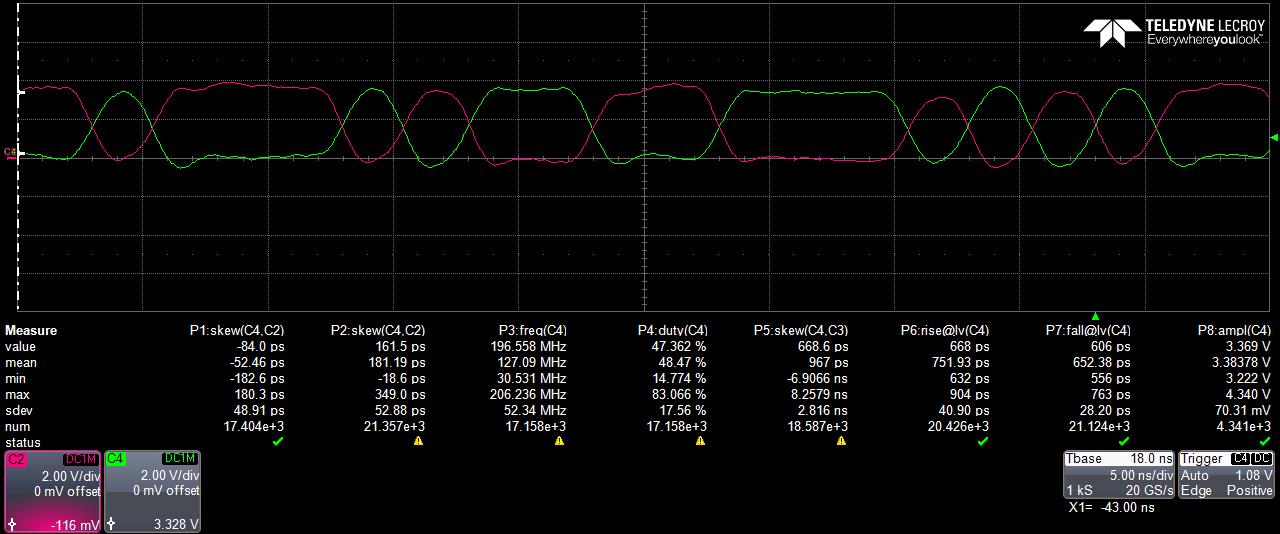

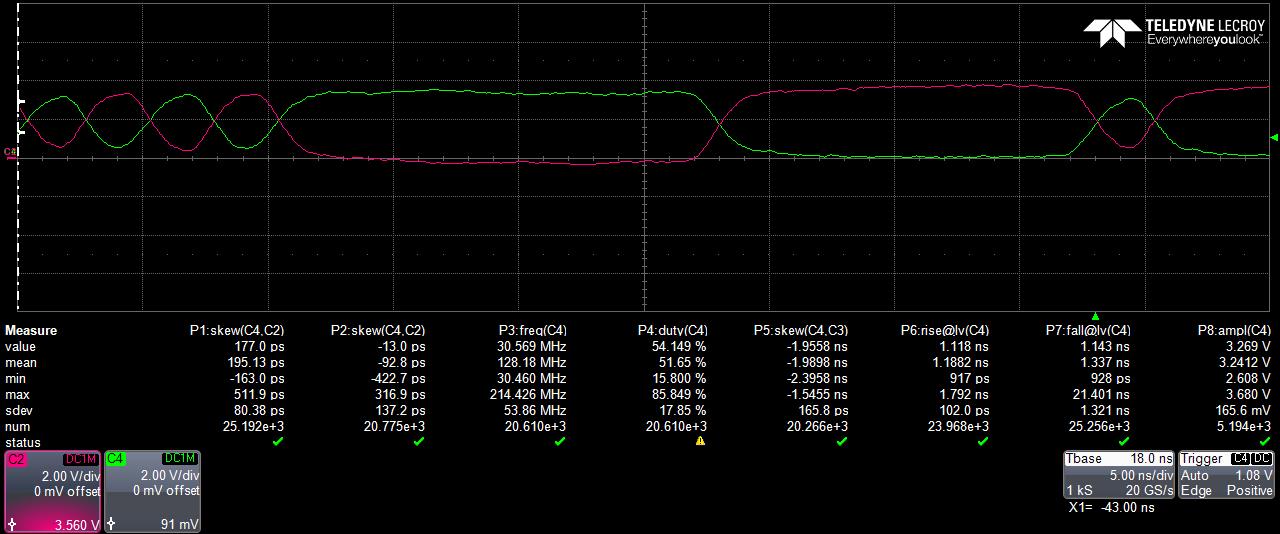

Figure 3-6 Competitor Outputs (10 pF 1.8 V to 3.3 V Up Translation at 125 MHz, 25°C)- For 15 pF, Figure 3-7 shows TXV outputs (measuring PRBS rise-to-fall skew of 53 ps and fall-to-rise skew of 181 ps) vs competitor (measuring 195 ps and 93 ps respectively). For fall or rise times, TXV (measured 752 / 652 ps) vs competitor (measuring approximately 2x slower rise or fall times >750 ps), violating RGMII requirement as shown in Figure 3-8.

Figure 3-7 TXV Outputs (15 pF 1.8 V to 3.3 V Up Translation at 125 MHz, 25°C)

Figure 3-7 TXV Outputs (15 pF 1.8 V to 3.3 V Up Translation at 125 MHz, 25°C) Figure 3-8 Competitor Outputs (15 pF 1.8 V to 3.3 V Up Translation at 125 MHz, 25°C)

Figure 3-8 Competitor Outputs (15 pF 1.8 V to 3.3 V Up Translation at 125 MHz, 25°C)