SLUAA81A October 2020 – February 2022 BQ769142 , BQ76922 , BQ76942 , BQ76952

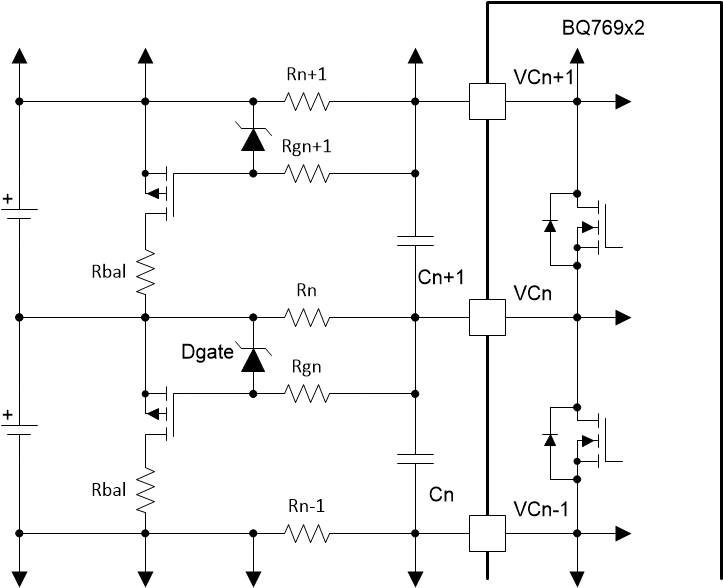

2.3 External Cell-Balancing Circuit Design Using P-Channel FETs

P-channel FETs can similarly be used for external balancing. When using P-channel FETs, VGS is generated on the top input resistor for each cell.

Figure 2-4 Balancing Circuit Using External

P-Channel FETs

Figure 2-4 Balancing Circuit Using External

P-Channel FETs