SNLA246C October 2015 – April 2024 DP83867CR , DP83867CS , DP83867E , DP83867IR , DP83867IS

- 1

- Trademarks

- 1Introduction

- 2Troubleshooting the Application

-

3Application Specific

Debugs

- 3.1 Improving Link-up Margins for Short Cables

- 3.2 Improving Link Margins across Different Channels

- 3.3 Link up in 100Mbps Full Duplex Force Mode

- 3.4 Unstable Link Up Debug in 1Gbps communication

- 3.5 DP83867PHY and DP83867PHY Cannot Link Up in 1Gbps

- 3.6 Compliance Debug

- 3.7 EMC Debug

- 3.8 Tools and References

- 4Conclusion

- 5References

- 6Revision History

3.5 DP83867PHY and DP83867PHY Cannot Link Up in 1Gbps

If two DP83867PHYs are able to link up at 10Mbps and 100Mbps but not able to link up at 1Gbps, please refer to the following debug process:

Note: This errata only occur in old revision of the

DP83867PHY (Register 0x0003 = A0F1)

- Try software reset by writing register 0x001F = 4000 on one of the DP83867PHY and see if that resolve the issue.

- Read register 0x0005[15] and If 0x0005 bit[15] = 0,

- Auto-MDIX is most likely not complete. Both of the PHY is sending Auto-MDIX FLP_Brust in the same channel at the same time and result in deadlock situation.

Solution:

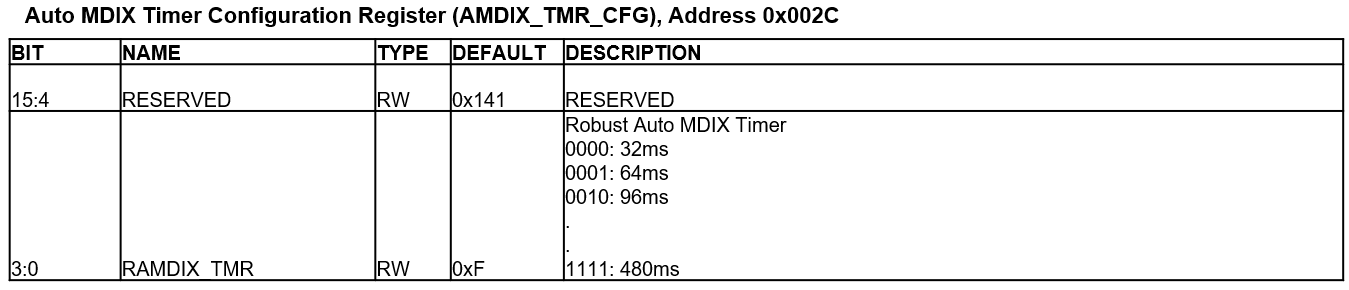

- Change Auto MDIX timer on one of the PHY can prevent the deadlock situation.

- Change register 0x002C bit[32] = 0 on one of the DP83867PHY

- write 0x001F to 4000 to software reset the PHY

- Read register 0x0005[15] and If

0x0005 bit[15] = 1

- Auto-MDIX is complete and Auto-negotiation pseudo random number (PRN) is most likely be the issue. Pseudo random number (PRN) sending random number to determine which PHY is Master PHY (clocked from a local source) and which one is the slave PHY (clocked from the recovered clock on the received data stream) when both PHY are communicate in 1000Base-T. This can be check through register 0x000A bit[14].

- However, the PRN is not exactly random and if both DP83867 start auto-negotiation at the same time, there is a possibility both DP83867 send out the exact same random seed (PRN) and result in dead lock.

Solution:

- Write 0x0009 bit[12:11] to 11 on one of the DP83867PHY and write 0x0009 bit[12 :11] to 10 on another DP83867PHY. This register can force one of the PHY to always be MASTER in 1000Base-T communication to prevent the Pseudo random number (PRN) process.

- Write 0x001F to 4000 to software reset the PHY or write 0x0000[9] =1 to restart the auto-negotiation