SPRADD4 October 2023 AM625SIP

10 Power Decoupling

The middle priority interfaces and the power distribution planes and pours would be routed next after the SerDes interfaces. It is strongly encouraged to complete all SerDes routing before continuing with other interfaces. The power distribution planes and pours and all of the decoupling must be placed before PCB simulations are executed for the SerDes routes, as these can influence the return currents for the high-speed interfaces. The highest speed source-synchronous interfaces, such as RGMII and QSPI, may also require simulation, so these may need to be completed at this time as well.

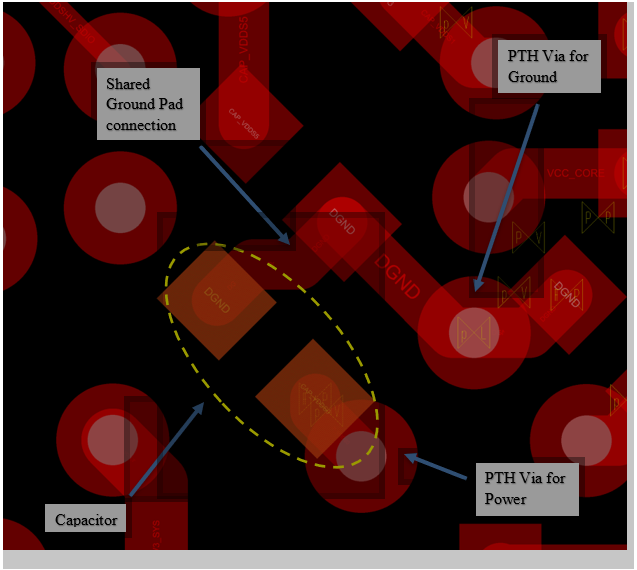

Special care is needed for the 1-uF output capacitors connected to the CAP_VDDS* BGA pins on the AM62XSiP device. These capacitors should be placed as close to the pin as possible, and a low inductance path should be present between the CAP_VDDS BGA pin and the supply pad on the capacitor. The layout used on the CAP_VDDS0 net on the AM62XSiP SK EVM is shown in Figure 10-1. Note the sharing of the GND pad of the capacitor with other capacitors in the vicinity, which allows saving routing resources. Also, it is important to keep the PTH vias for the capacitor power and GND pad connections as close to each other as possible to minimize the loop inductance.

Figure 10-1 AM62XSiP SK EVM Output Capacitor Placement for CAP_VDDS0

Figure 10-1 AM62XSiP SK EVM Output Capacitor Placement for CAP_VDDS0This placement can be improved if the capacitors can be placed directly under the SoC. The decoupling capacitors for the VDD_CORE supplies should also receive the same priority as those on the CAP_VDDS* pins and should be placed under the socket, with minimum inductance connections to the respective BGA pins on the AM62XSiP device.