SPRUJ10D May 2022 – September 2023

- 1

- Abstract

- Trademarks

- 1Preface: Read This First

- 2Kit Overview

- 3Board Setup

-

4Hardware Description

- 5.1 Functional Block Diagram

- 5.2 GPIO Mapping

- 5.3 Reset

- 5.4 Clock

- 5.5 Memory Interface

- 5.6 Ethernet Interface

- 5.7 I2C

- 5.8 Industrial Application LEDs

- 5.9 SPI

- 5.10 UART

- 5.11 MCAN

- 5.12 FSI

- 5.13 JTAG

- 5.14 Test Automation Header

- 5.15 LIN

- 5.16 MMC

- 5.17 ADC and DAC

- 5.18 EQEP and SDFM

- 5.19 EPWM

- 5.20 BoosterPack Headers

- 5.21 Pinmux Mapping

- 5References

- 6Revision History

4.3 Reset

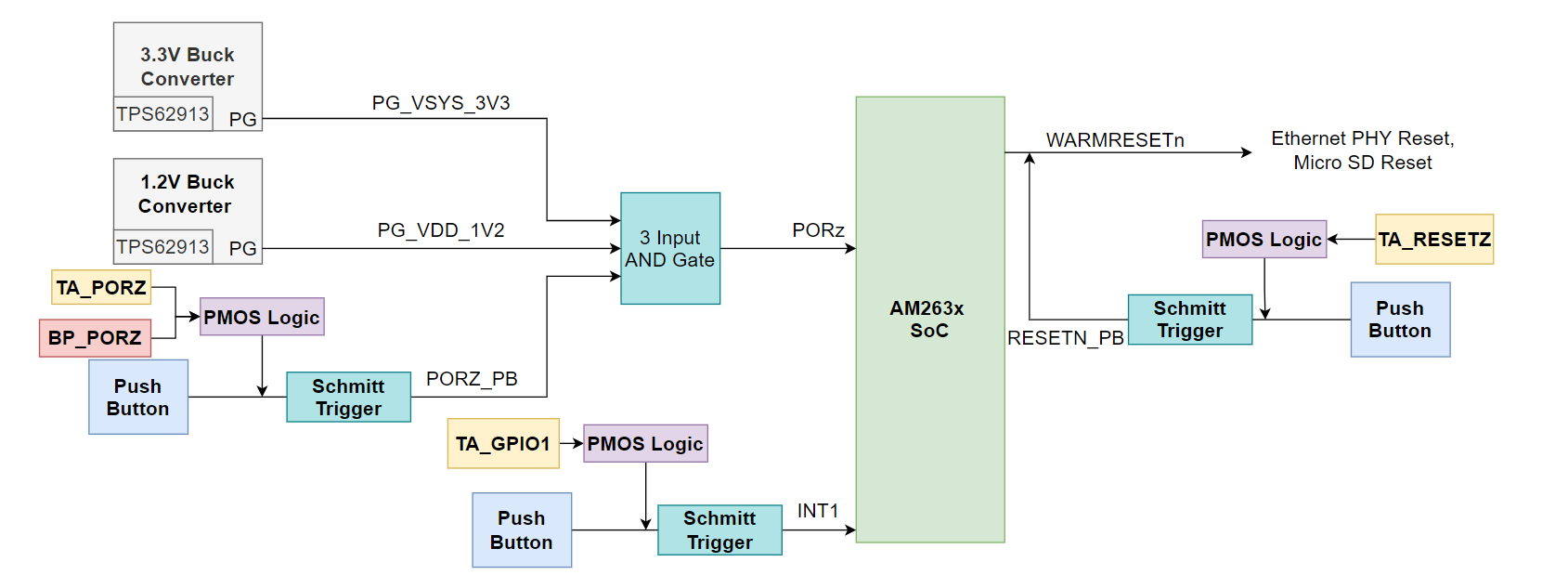

Figure 4-2 shows the reset architecture of the AM263x LaunchPad

Figure 4-2 Reset Architecture

Figure 4-2 Reset ArchitectureThe AM263x LaunchPad has the following resets:

- PORz is the Power On Reset

- WARMRESETn is the warm reset

Figure 4-3 PORz Reset Signal Tree

Figure 4-3 PORz Reset Signal TreeThe PORz signal is driven by a 3-input AND gate that generates a power on reset for the MAIN domain when:

- The 3.3V buck converter (TPS62913) power good output is driven low by having an output voltage that is below the power-good threshold.

- The 1.2V buck converter (TPS62912) power good output is driven low by having an output voltage that is below the power-good threshold.

- The user push button (SW2) is pressed.

- A P-Channel MOSFET gate's

signal is logic LOW which causes V_GS of the PMOS to be less than zero and

so the PORz signal connects to the PMOS drain which is tied directly to

ground. The signals that can create the logic LOW input to the PMOS gate

are:

- TA_PORZ output from the Test Automation header

- BP_PORZ output from either of the BoosterPack sites.

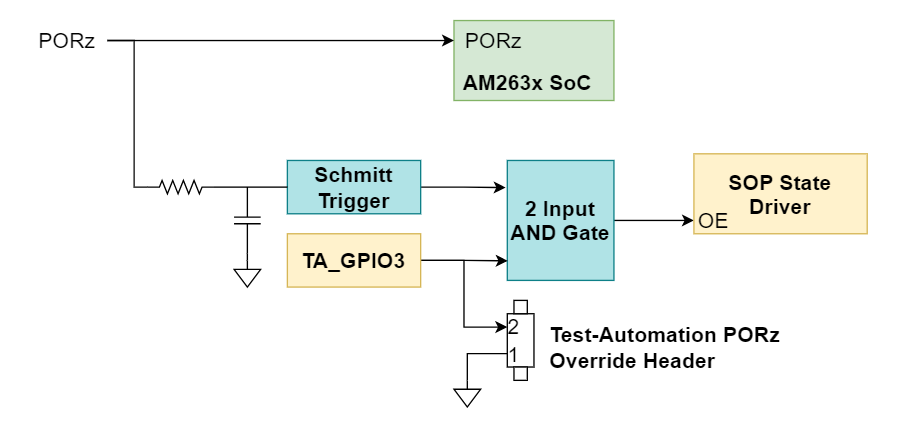

The PORz signal is tied to:

- AM263x SoC PORz input

- BOOTMODE State Driver's

output enable input

- There is an RC filter to create a 1ms delay from GND to 3.0V such that the SOP State Driver's output enable input is low longer than the required SOP hold time following a PORz de-assertion.

There is a Test-Automation PORz Override header that enables the ability to hold TA_GPIO3 low when a jumper is installed. This enables the BOOTMODE Control from the Test Automation Header.

Figure 4-4 WARMRESETn Reset Signal

Tree

Figure 4-4 WARMRESETn Reset Signal

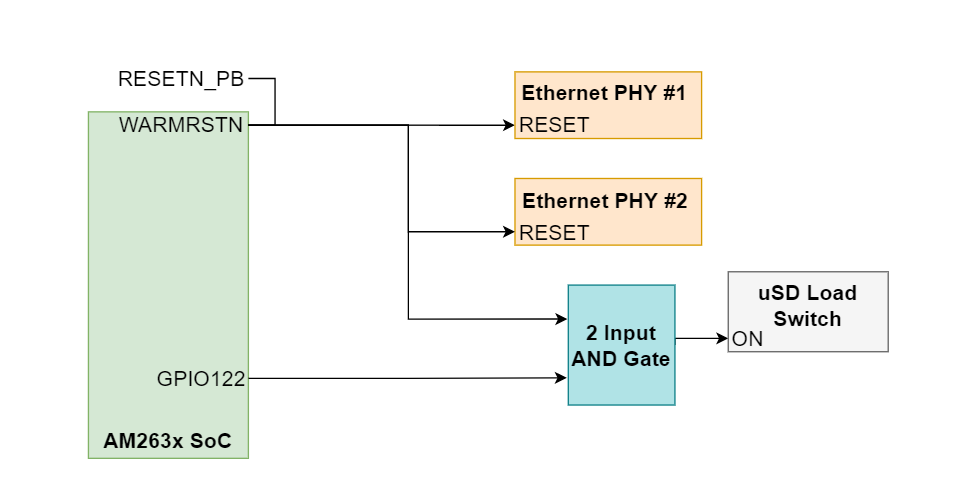

TreeThe WARMRESETn signal creates a warm reset to the MAIN domain when:

- The user push button (SW3) is presed.

- The Test Automation Header outputs a logic LOW signal (TA_RESETz) to a P-Channel MOSFET gate which causes V_GS of the PMOS to be less than zero and so the RESETz signal connects to the PMOS drain which is tied directly to ground.

The WARMRESETn signal is tied to:

- AM263x SoC WARMRESETN output

- RESETN_PB signal that is created from push button + PMOS logic

- Micro SD Load Switch control input via a 2 input AND Gate with an AM263x SoC driven GPIO signal (GPIO122)

- Both Ethernet PHY's reset input

The AM263x LaunchPad also has an external interrupt to the SoC , INT1, that occurs when:

- The user push button (SW4) is pressed.

- The Test Automation Header outputs a logic LOW signal (TA_GPIO1) to a P-Channel MOSFET gate which causes V_GS of the PMOS to be less than zero and so the INTn signal connects to the PMOS drain which is tied directly to ground.