DLPS029F April 2013 – May 2019 DLPC350

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 I/O Electrical Characteristics

- 6.6 I2C0 and I2C1 Interface Timing Requirements

- 6.7 Port 1 Input Pixel Interface Timing Requirements

- 6.8 Port 2 Input Pixel Interface (FPD-Link Compatible LVDS Input) Timing Requirements

- 6.9 System Oscillator Timing Requirements

- 6.10 Reset Timing Requirements

- 6.11 Video Timing Input Blanking Specification

- 6.12 Programmable Output Clocks Switching Characteristics

- 6.13 DMD Interface Switching Characteristics

- 6.14 JTAG Interface: I/O Boundary Scan Application Switching Characteristics

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

-

11Layout

- 11.1 Layout Guidelines

- 11.2 Layout Example

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- ZFF|419

Thermal pad, mechanical data (Package|Pins)

10.1.7 System Reset Operation

Immediately following any type of system reset (power-up reset, PWRGOOD reset, and so forth), the DLPC350 controller automatically returns to NORMAL power mode and returns to the following state:

- All GPIO 3-state and as a result all GPIO-controlled voltage switches default to enabling power to all the DLPC350 supply lines (assuming that these outputs are externally pulled-high).

- The master PLL remains active (it is only reset on a power-up reset) and most of the derived clocks are active. However, only those resets associated with the internal processor and its peripherals are released.

- The internal processor associated clocks default to their full clock rates, as boot-up occurs at full speed.

- The PLL feeding the DDR DMD interface (PLLD) defaults to its power-down mode, and all derived clocks are inactive with the corresponding resets asserted.

- The DMD interface (except DMD_DRC_OE) default outputs to a logic low state. DMD_DRC_OE defaults to 3-state, but should be pulled high via an external 30- to 51-kΩ pullup resistor on the PCB.

- All resets output by the DLPC350 controller remain asserted until released by the internal processor (after boot-up).

- The DLPC350 controller boots-up from external flash. After the DLPC350 controller boots, it:

- Configures the programmable DDR clock generator (DCG) clock rates (that is, the DMD LPDDR interface rate).

- Enables the DCG PLL (PLLD) while holding the divider logic in reset.

- After the DCG PLL locks, the firmware sets the DMD clock rates.

- The DLPC350 firmware then releases the DCG divider logic resets, which in turn, enables all derived DCG clocks.

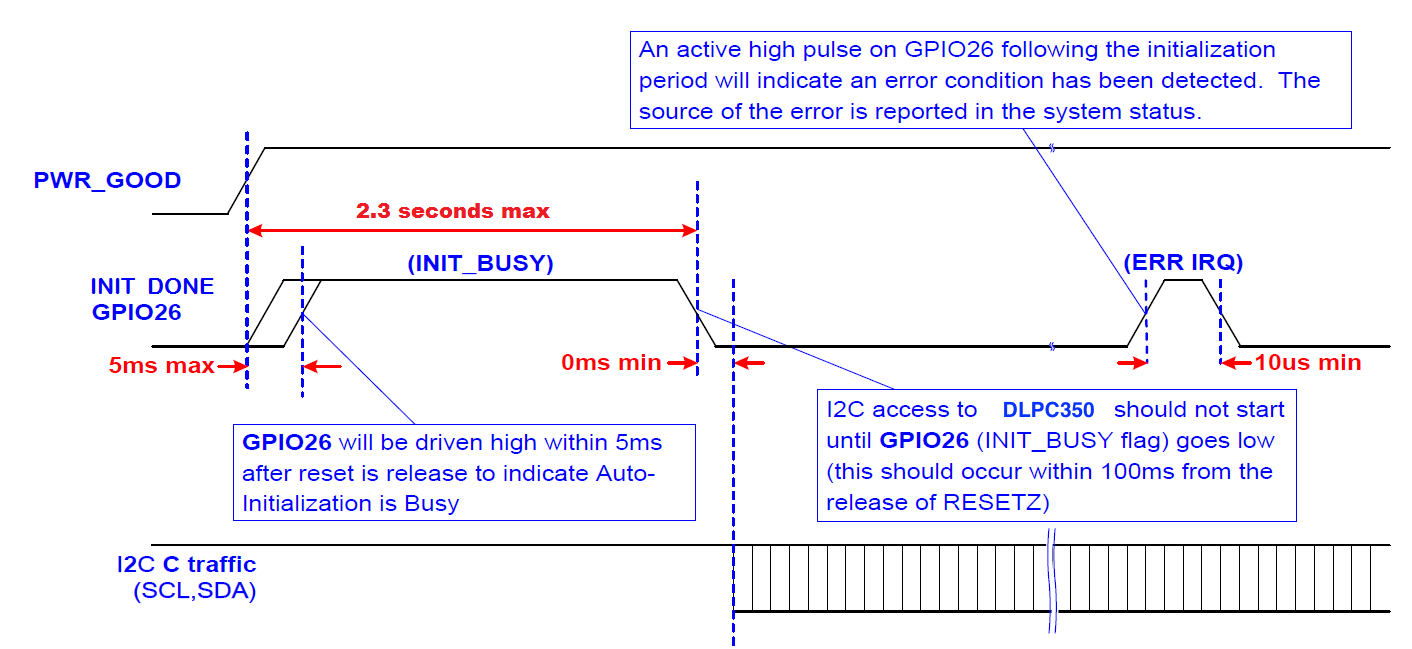

- After the clocks are configured, an internal memory test is performed. See Figure 23 and note that GPIO26 is the INIT_DONE signal.

Application software should wait for a wake-up command from the user. After the controller is requested to wake-up, the software should place the controller back in NORMAL mode and re-initialize clocks and resets as required. See reset timing requirements in Reset Timing Requirements.

Figure 23. Internal Memory Test Diagram

Figure 23. Internal Memory Test Diagram