SBAS627 July 2015 ADS8674 , ADS8678

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Analog Inputs

- 8.3.2 Analog Input Impedance

- 8.3.3 Input Overvoltage Protection Circuit

- 8.3.4 Programmable Gain Amplifier (PGA)

- 8.3.5 Second-Order, Low-Pass Filter (LPF)

- 8.3.6 ADC Driver

- 8.3.7 Multiplexer (MUX)

- 8.3.8 Reference

- 8.3.9 Auxiliary Channel

- 8.3.10 ADC Transfer Function

- 8.3.11 Alarm Feature

- 8.4

Device Functional Modes

- 8.4.1 Device Interface

- 8.4.2

Device Modes

- 8.4.2.1 Continued Operation in the Selected Mode (NO_OP)

- 8.4.2.2 Frame Abort Condition (FRAME_ABORT)

- 8.4.2.3 STANDBY Mode (STDBY)

- 8.4.2.4 Power-Down Mode (PWR_DN)

- 8.4.2.5 Auto Channel Enable with Reset (AUTO_RST)

- 8.4.2.6 Manual Channel n Select (MAN_Ch_n)

- 8.4.2.7 Channel Sequencing Modes

- 8.4.2.8 Reset Program Registers (RST)

- 8.5

Register Maps

- 8.5.1 Command Register Description

- 8.5.2

Program Register Description

- 8.5.2.1 Program Register Read/Write Operation

- 8.5.2.2 Program Register Map

- 8.5.2.3

Program Register Descriptions

- 8.5.2.3.1 Auto-Scan Sequencing Control Registers

- 8.5.2.3.2 Device Features Selection Control Register (address = 03h)

- 8.5.2.3.3 Range Select Registers (addresses 05h-0Ch)

- 8.5.2.3.4 Alarm Flag Registers (Read-Only)

- 8.5.2.3.5 Alarm Threshold Setting Registers

- 8.5.2.3.6 Command Read-Back Register (address = 3Fh)

- 9 Application and Implementation

- 10Power-Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DBT|38

Thermal pad, mechanical data (Package|Pins)

Orderable Information

10 Power-Supply Recommendations

The device uses two separate power supplies: AVDD and DVDD. The internal circuits of the device operate on AVDD; DVDD is used for the digital interface. AVDD and DVDD can be independently set to any value within the permissible range.

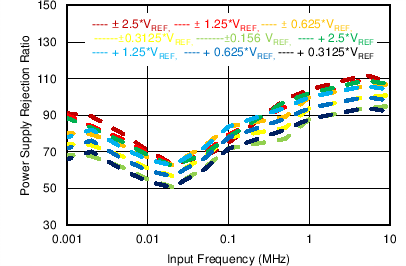

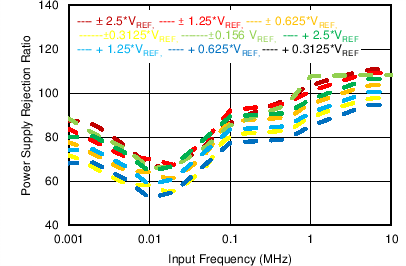

The AVDD supply pins must be decoupled with AGND by using a minimum 10-µF and 1-µF capacitor on each supply. Place the 1-µF capacitor as close to the supply pins as possible. Place a minimum 10-µF decoupling capacitor very close to the DVDD supply to provide the high-frequency digital switching current. The effect of using the decoupling capacitor is illustrated in the difference between the power-supply rejection ratio (PSRR) performance of the device. Figure 126 shows the PSRR of the device without using a decoupling capacitor. The PSRR improves when the decoupling capacitors are used, as shown in Figure 127.

| Code output near 8192 |

| Code output near 8192 |