SLOS729D October 2011 – November 2015 AFE5808A

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (continued)

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4 Device Functional Modes

- 8.5 Programming

- 8.6

Register Maps

- 8.6.1 ADC Register Map

- 8.6.2

ADC Register/Digital Processing Description

- 8.6.2.1 AVERAGING_ENABLE: Address: 2[11]

- 8.6.2.2 ADC_OUTPUT_FORMAT: Address: 4[3]

- 8.6.2.3 DIGITAL_GAIN_ENABLE: Address: 3[12]

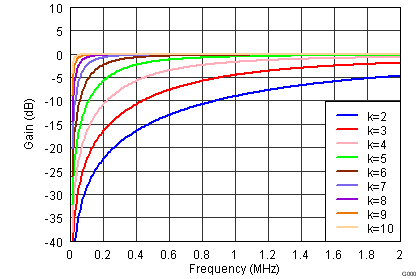

- 8.6.2.4 DIGITAL_HPF_ENABLE

- 8.6.2.5 DIGITAL_HPF_FILTER_K_CHX

- 8.6.2.6 LOW_FREQUENCY_NOISE_SUPPRESSION: Address: 1[11]

- 8.6.2.7 LVDS_OUTPUT_RATE_2X: Address: 1[14]

- 8.6.2.8 CHANNEL_OFFSET_SUBSTRACTION_ENABLE: Address: 3[8]

- 8.6.2.9 SERIALIZED_DATA_RATE: Address: 3[14:13]

- 8.6.2.10 TEST_PATTERN_MODES: Address: 2[15:13]

- 8.6.2.11 SYNC_PATTERN: Address: 10[8]

- 8.6.3 VCA Register Map

- 8.6.4 AFE5808A VCA Register Description

-

9 Application and Implementation

- 9.1 Application Information

- 9.2 Typical Application

- 9.3

Do's and Don'ts

- 9.3.1 Driving the Inputs (Analog or Digital) Beyond the Power-Supply Rails

- 9.3.2 Driving the Device Signal Input With an Excessively High Level Signal

- 9.3.3 Driving the VCNTL Signal With an Excessive Noise Source

- 9.3.4 Using a Clock Source With Excessive Jitter, an Excessively Long Input Clock Signal Trace, or Having Other Signals Coupled to the ADC or CW Clock Signal Trace

- 9.3.5 LVDS Routing Length Mismatch

- 9.3.6 Failure to Provide Adequate Heat Removal

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- ZCF|135

Thermal pad, mechanical data (Package|Pins)

Orderable Information

7 Specifications

7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)(1)| MIN | MAX | UNIT | ||

|---|---|---|---|---|

| Supply voltage | AVDD | –0.3 | 3.9 | V |

| AVDD_ADC | –0.3 | 2.2 | V | |

| AVDD_5V | –0.3 | 6 | V | |

| DVDD | –0.3 | 2.2 | V | |

| Voltage between AVSS and LVSS | –0.3 | 0.3 | V | |

| Voltage at analog inputs and digital inputs | –0.3 | min [3.6, AVDD + 0.3] | V | |

| Peak solder temperature(2) | 260 | °C | ||

| Maximum junction temperature (TJ), any condition | 105 | °C | ||

| Operating temperature | 0 | 85 | °C | |

| Storage temperature, Tstg | –55 | 150 | °C | |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) Device complies with JSTD-020D.

7.2 ESD Ratings

| VALUE | UNIT | |||

|---|---|---|---|---|

| V(ESD) | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001(1) | ±1000 | V |

| Charged-device model (CDM), per JEDEC specification JESD22-C101(2) | ±250 | |||

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

7.3 Recommended Operating Conditions

| MIN | MAX | UNIT | |

|---|---|---|---|

| AVDD | 3.15 | 3.6 | V |

| AVDD_ADC | 1.7 | 1.9 | V |

| DVDD | 1.7 | 1.9 | V |

| AVDD_5V | 4.75 | 5.5 | V |

| Ambient temperature, TA | 0 | 85 | °C |

7.4 Thermal Information

| THERMAL METRIC(1) | AFE5808A | UNIT | |

|---|---|---|---|

| ZCF (NFBGA) | |||

| 135 PINS | |||

| RθJA | Junction-to-ambient thermal resistance | 34.1 | °C/W |

| RθJC(top) | Junction-to-case (top) thermal resistance | 5 | °C/W |

| RθJB | Junction-to-board thermal resistance | 11.5 | °C/W |

| ψJT | Junction-to-top characterization parameter | 0.2 | °C/W |

| ψJB | Junction-to-board characterization parameter | 10.8 | °C/W |

| RθJC(bot) | Junction-to-case (bottom) thermal resistance | N/A | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

7.5 Electrical Characteristics

At AVDD_5 V = 5 V, AVDD = 3.3 V, AVDD_ADC = 1.8 V, DVDD = 1.8 V, ac-coupled with 0.1 µF at INP and bypassed to ground with 15 nF at INM, no active termination, VCNTL = 0 V, fIN = 5 MHz, LNA = 18 dB, PGA = 24 dB, 14 bit, samplerate = 65 MSPS, LPF filter = 15 MHz, low-noise mode, VOUT = –1 dBFS, internal 500-Ω CW feedback resistor, CMOS CW clocks, ADC configured in internal reference mode, single-ended VCNTL mode, VCNTLM = GND, at ambient temperature

TA = 25°C (unless otherwise noted). Min and max values are specified across full-temperature range with AVDD_5 V = 5 V,

AVDD = 3.3 V, AVDD_ADC = 1.8 V, DVDD = 1.8 V

| PARAMETER | TEST CONDITION | MIN | TYP | MAX | UNIT | |

|---|---|---|---|---|---|---|

| TGC FULL SIGNAL CHANNEL (LNA+VCAT+LPF+ADC) | ||||||

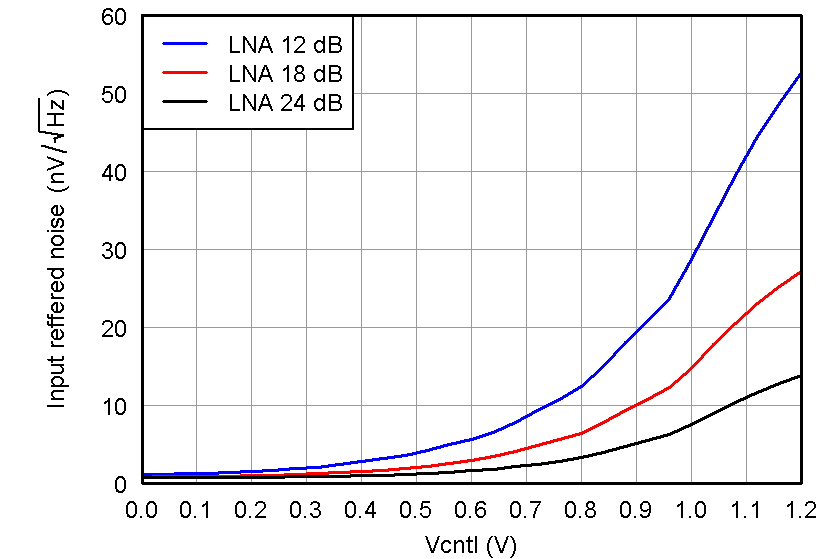

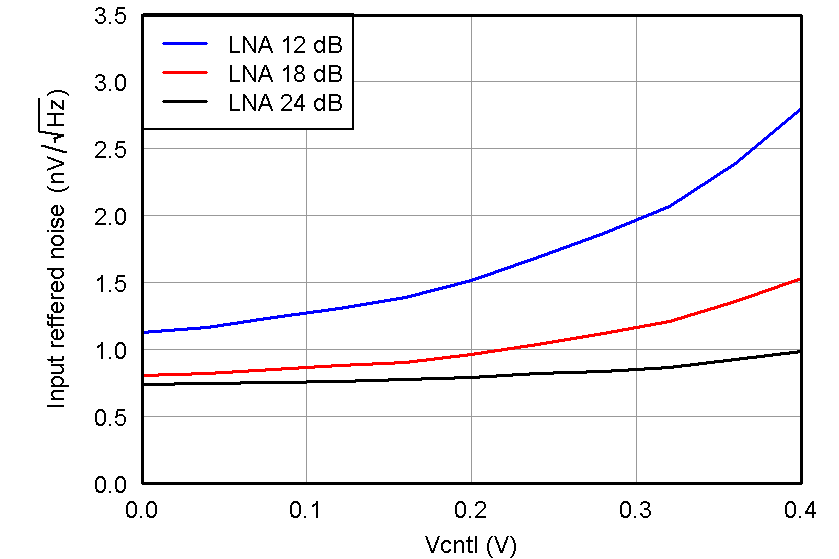

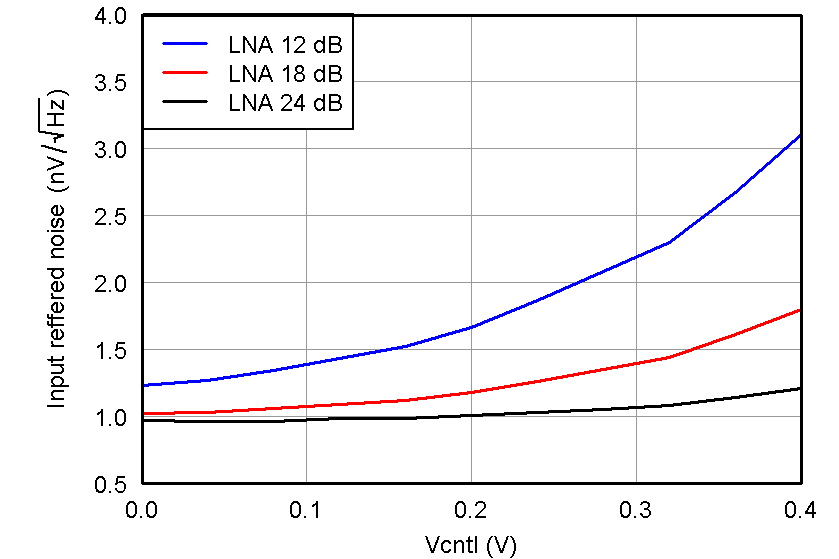

| en (RTI) | Input voltage noise over LNA Gain (low noise mode) | Rs = 0 Ω, f = 2 MHz, LNA = 24 dB, 18 dB, and 12 dB, PGA = 24 dB | 0.76/0.83/1.16 | nV/√Hz | ||

| Rs = 0 Ω, f = 2 MHz, LNA = 24 dB, 18 dB, and 12 dB, PGA = 30 dB | 0.75/0.86/1.12 | |||||

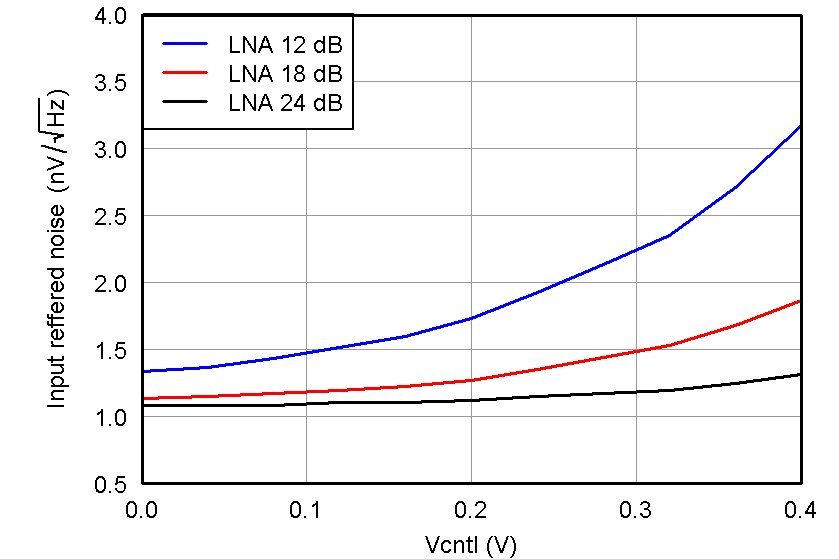

| Input voltage noise over LNA Gain (low power mode) | Rs = 0 Ω, f = 2 MHz, LNA = 24 dB, 18 dB, and 12 dB, PGA = 24 dB | 1.1/1.2/1.45 | nV/√Hz | |||

| Rs = 0 Ω, f = 2 MHz, LNA = 24 dB, 18 dB, and 12 dB, PGA = 30 dB | 1.1/1.2/1.45 | |||||

| Input Voltage Noise over LNA Gain (Medium Power Mode) | Rs = 0 Ω, f = 2 MHz, LNA = 24 dB, 18 dB, and 12 dB, PGA = 24 dB | 1/1.05/1.25 | nV/√Hz | |||

| Rs = 0 Ω, f = 2 MHz, LNA = 24 dB, 18 dB, and 12 dB, PGA = 30 dB | 0.95/1.0/1.2 | |||||

| Input referred current noise | Low Noise Mode/Medium Power Mode/Low Power Mode | 2.7/2.1/2 | pA/√Hz | |||

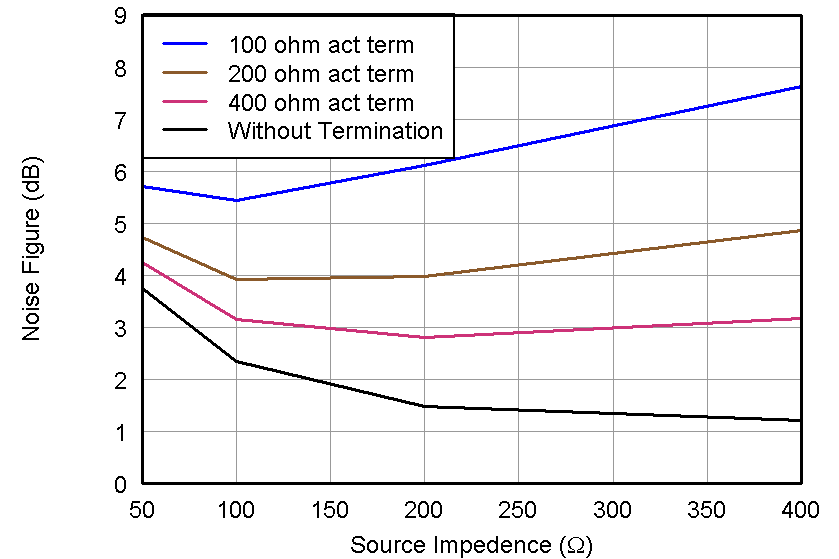

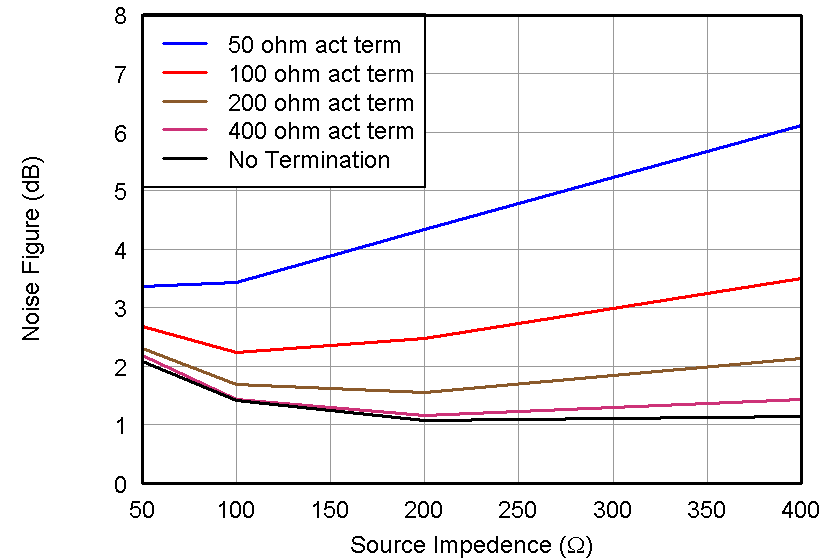

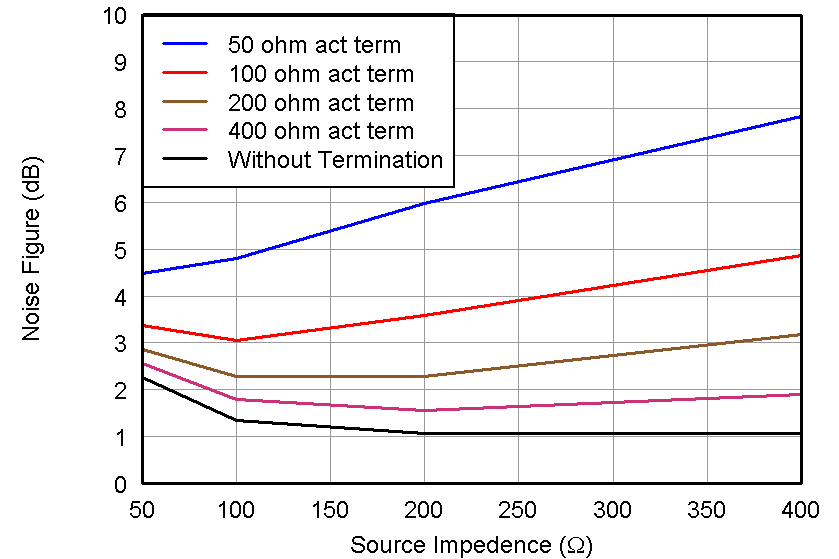

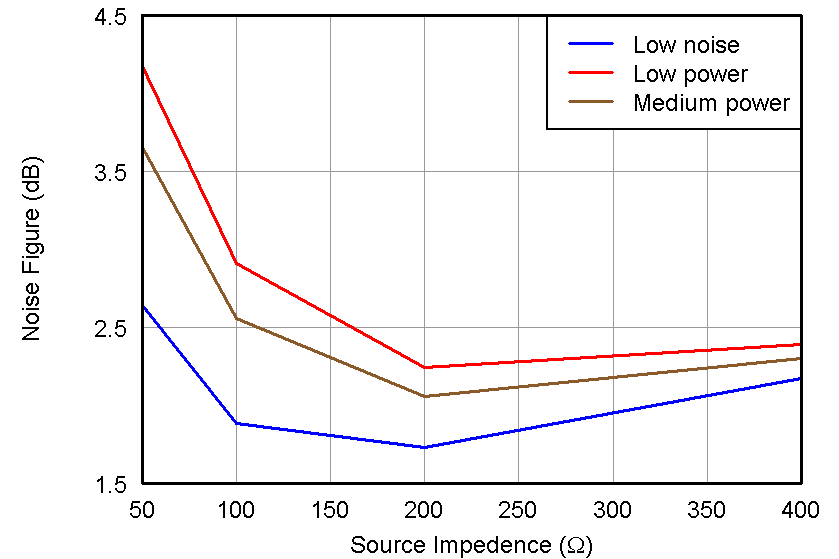

| NF | Noise figure | Rs = 200 Ω, 200-Ω active termination, PGA = 24 dB, LNA = 12 dB, 18 dB, and 24 dB | 3.85/2.4/1.8 | dB | ||

| Rs = 100 Ω, 100-Ω active termination, PGA = 24 dB, LNA = 12 dB, 18 dB, and 24 dB | 5.3/3.1/2.3 | dB | ||||

| VMAX | Maximum Linear Input Voltage | LNA gain = 24 dB, 18 dB, and 12 dB | 250/500/1000 | mVPP | ||

| VCLAMP | Clamp Voltage | Reg52[10:9] = 0, LNA = 24 dB, 18 dB, and 12 dB | 350/600/1150 | |||

| PGA Gain | Low noise mode | 24/30 | dB | |||

| Medium and low power mode | 24/28.5 | |||||

| Total gain | LNA = 24 dB, PGA = 30 dB, Low noise mode | 54 | dB | |||

| LNA = 2 4dB, PGA = 30 dB, Med power mode | 52.5 | |||||

| LNA = 24 dB, PGA = 30 dB, Low power mode | 52.5 | |||||

| Ch-CH Noise Correlation Factor without Signal (2) | Summing of 8 channels | 0 | ||||

| Ch-CH Noise Correlation Factor with Signal (2) | Full band (VCNTL = 0/0.8) | 0.15/0.17 | ||||

| 1MHz band over carrier (VCNTL= 0/0.8) | 0.18/0.75 | |||||

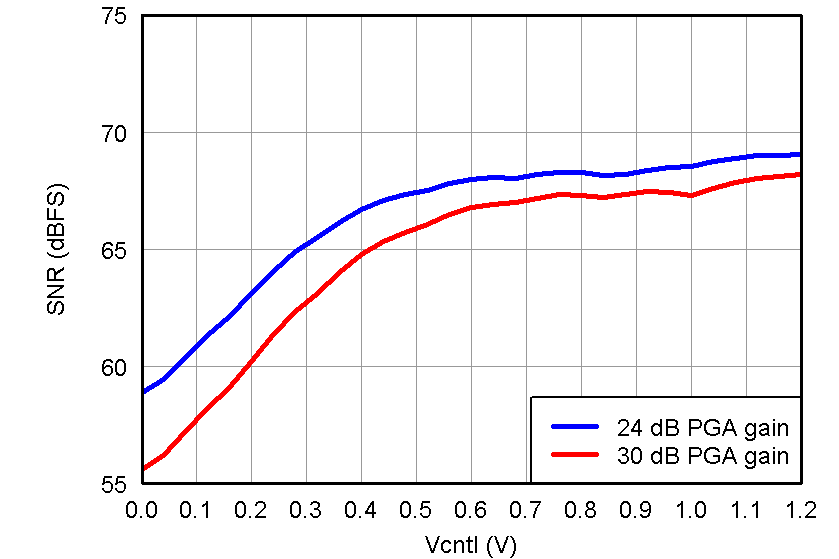

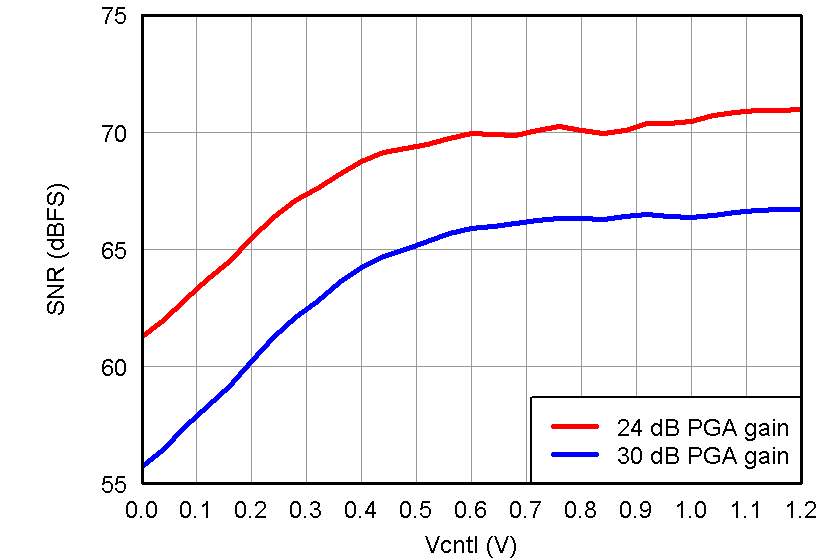

| Signal to Noise Ratio (SNR) | VCNTL = 0.6 V (22-dB total channel gain) | 68 | 70 | dBFS | ||

| VCNTL = 0, LNA = 18 dB, PGA = 24 dB | 59.3 | 63 | ||||

| VCNTL = 0, LNA = 24 dB, PGA = 24 dB | 58 | |||||

| Narrow Band SNR | SNR over 2-MHz band around carrier at VCNTL = 0.6 V ( 22 dB total gain) | 75 | 77 | dBFS | ||

| Input Common-mode Voltage | At INP and INM pins | 2.4 | V | |||

| Input resistance | 8 | kΩ | ||||

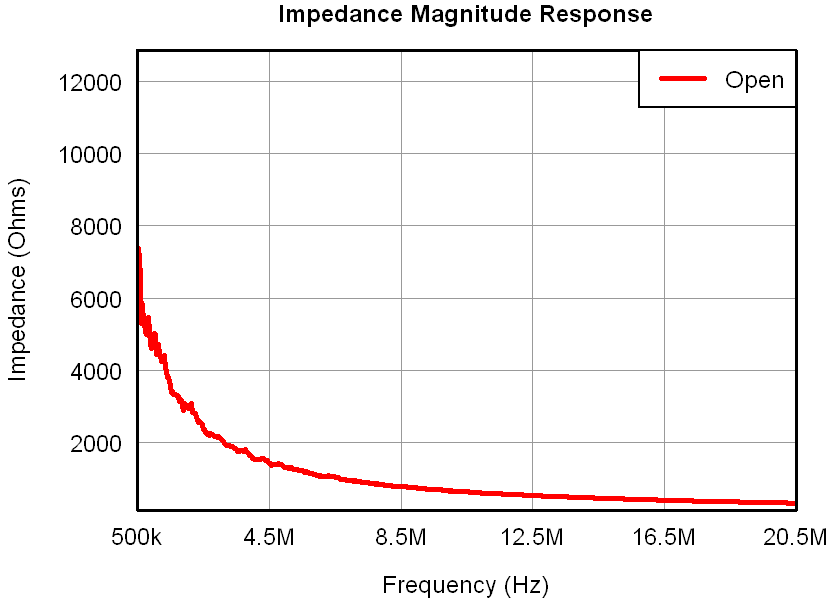

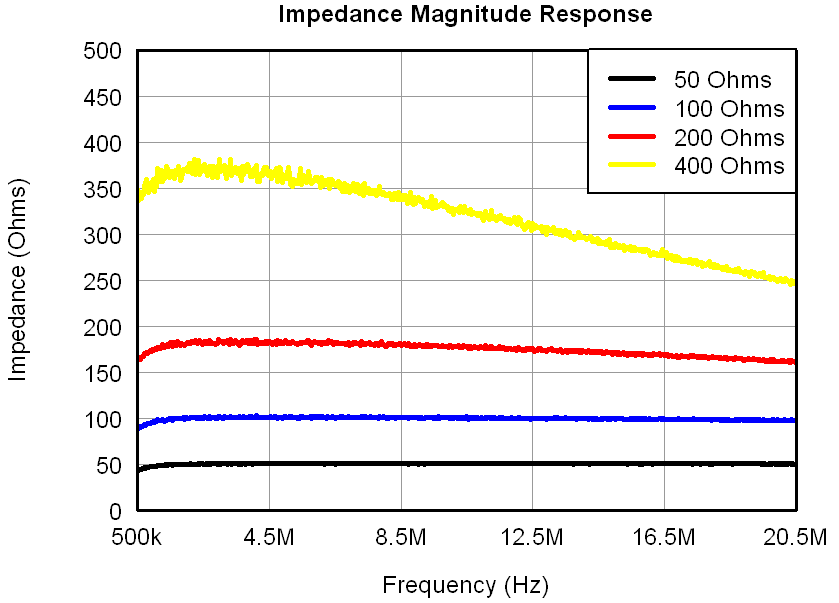

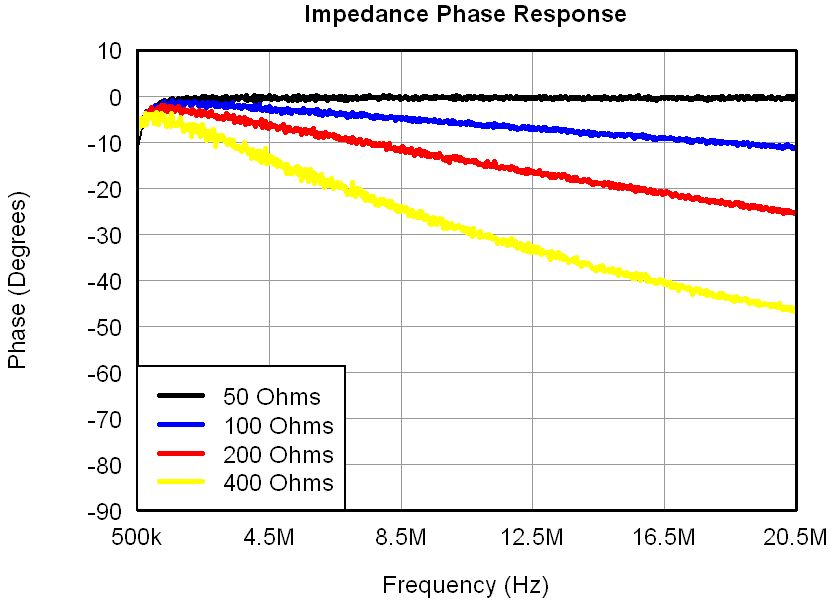

| Preset active termination enabled | 50/100/200/400 | Ω | ||||

| Input capacitance | 20 | pF | ||||

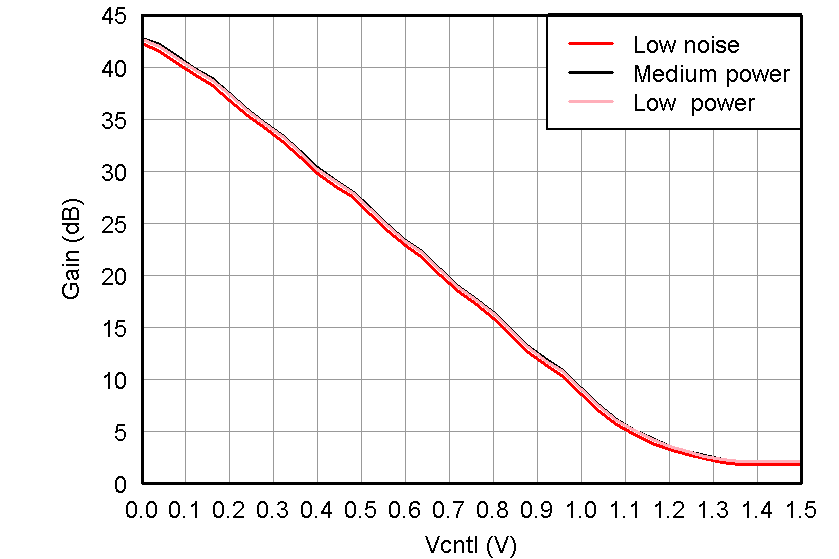

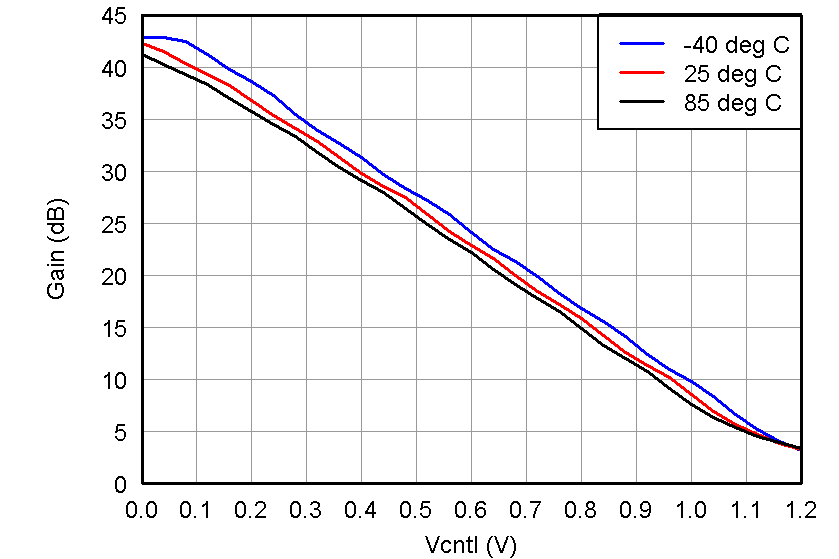

| Input Control Voltage | VCNTLP – VCNTLM | 0 | 1.5 | V | ||

| Common-mode voltage | VCNTLP and VCNTLM | 0.75 | V | |||

| Gain Range | -40 | dB | ||||

| Gain Slope | VCNTL= 0.1 to 1.1 V | 35 | dB/V | |||

| Input Resistance | Between VCNTLP and VCNTLM | 200 | KΩ | |||

| Input Capacitance | Between VCNTLP and VCNTLM | 1 | pF | |||

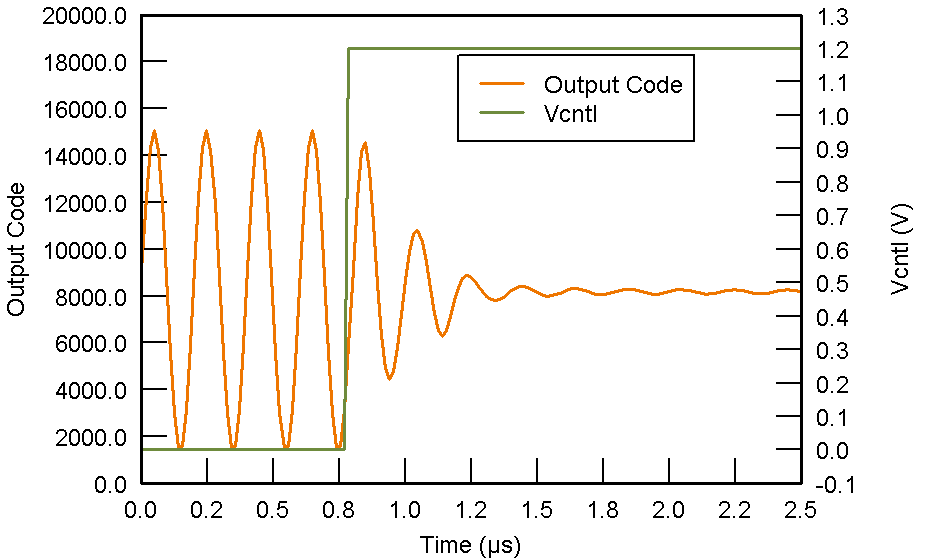

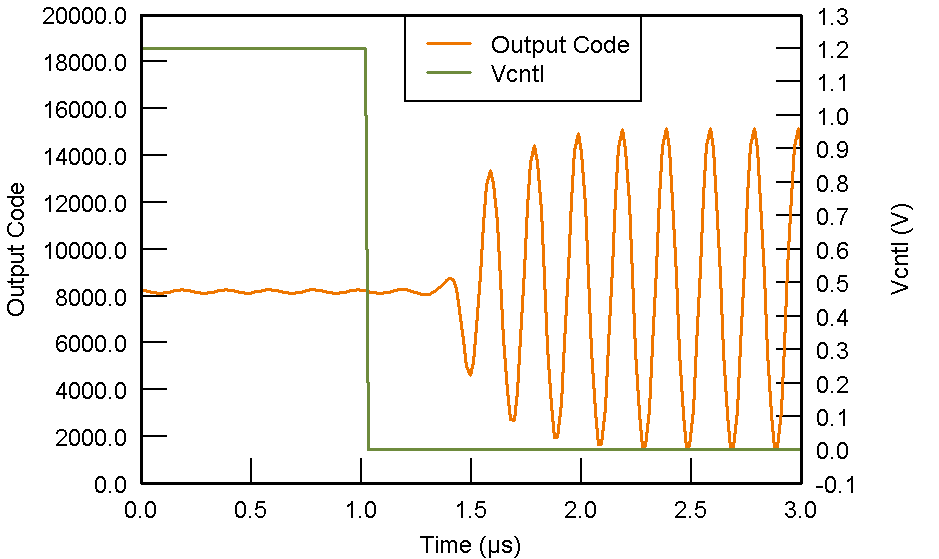

| TGC Response Time | VCNT L= 0 to 1.5-V step function | 1.5 | µs | |||

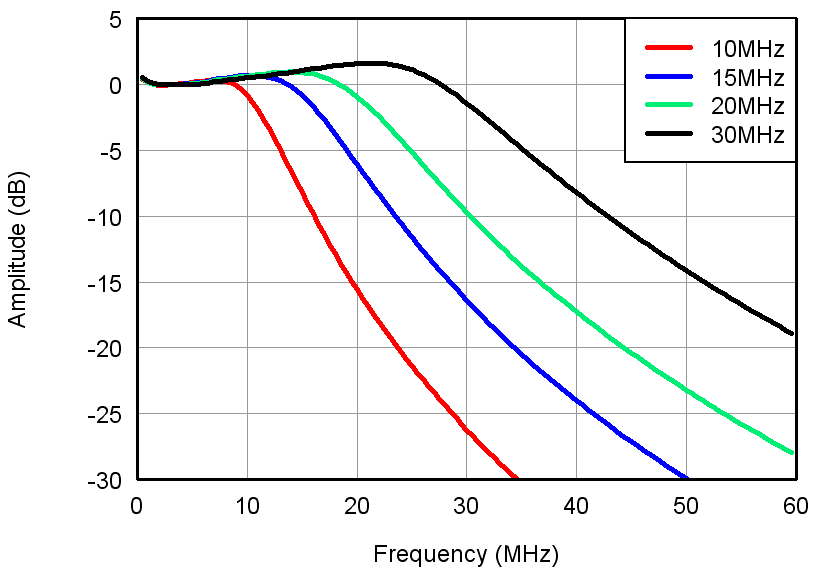

| 3rd order-Low-pass Filter | 10, 15, 20, 30 | MHz | ||||

| Settling time for change in LNA gain | 14 | µs | ||||

| Settling time for change in active termination setting | 1 | µs | ||||

| AC ACCURACY | ||||||

| LPF Bandwidth tolerance | ±5% | |||||

| CH-CH group delay variation | 2 MHz to 15 MHz | 2 | ns | |||

| CH-CH Phase variation | 15-MHz signal | 11 | Degree | |||

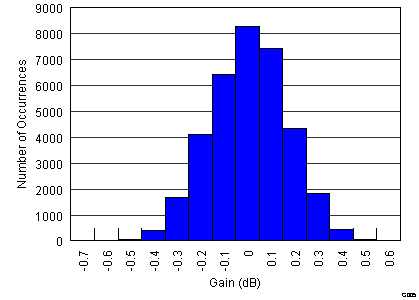

| Gain matching | 0 V < VCNTL < 0.1 V (Dev-to-Dev) | ±0.5 | dB | |||

| 0.1 V < VCNTL < 1.1 V(Dev-to-Dev) | –0.9 | ±0.5 | 0.9 | |||

| 0.1 V < VCNTL < 1.1 V(Dev-to-Dev) Temp = 0°C and 85°C | –1.1 | ±0.5 | 1.1 | |||

| 1.1 V < VCNTL < 1.5 V(Dev-to-Dev) | ±0.5 | |||||

| Gain matching | Channel-to-channel | ±0.25 | dB | |||

| Output offset | Vcntl= 0, PGA = 30 dB, LNA = 24 dB | –75 | 75 | LSB | ||

| AC PERFORMANCE | ||||||

| HD2 | Second-Harmonic Distortion | fIN = 2 MHz; VOUT = –1 dBFS | –60 | dBc | ||

| fIN = 5 MHz; VOUT = –1 dBFS | –60 | |||||

| fIN = 5 MHz; VIN= 500 mVPP, VOUT = –1 dBFS, LNA = 18 dB, VCNTL= 0.88 V |

–55 | |||||

| fIN = 5 MHz; Vin = 250 mVPP, VOUT =–1 dBFS, LNA = 24 dB, VCNTL= 0.88 V |

–55 | |||||

| HD3 | Third-Harmonic Distortion | fIN = 2 MHz; VOUT = –1 dBFS | –55 | dBc | ||

| fIN = 5 MHz; VOUT = –1 dBFS | –55 | |||||

| fIN = 5 MHz; VIN = 500 mVPP, VOUT = –1 dBFS, LNA = 18 dB, VCNTL= 0.88 V |

–55 | |||||

| fIN = 5 MHz; VIN = 2 50 mVPP, VOUT = –1 dBFS, LNA = 24 dB, VCNTL= 0.88 V |

–55 | |||||

| THD | Total Harmonic Distortion | fIN = 2 MHz; VOUT= –1 dBFS | –55 | dBc | ||

| fIN = 5 MHz; VOUT= –1 dBFS | –55 | |||||

| IMD3 | Intermodulation distortion | f1 = 5 MHz at –1 dBFS, f2 = 5.01 MHz at –27 dBFS |

–60 | dBc | ||

| XTALK | Cross-talk | fIN = 5 MHz; VOUT= –1 dBFS | –65 | dB | ||

| Phase Noise | 1 kHz off 5 MHz (VCNTL= 0 V) | –132 | dBc/Hz | |||

| LNA | ||||||

| Input Referred Voltage Noise | Rs = 0 Ω, f = 2MHz, Rin = High Z, Gain = 24/18/12 dB | 0.63/0.70/0.9 | nV/√Hz | |||

| High-Pass Filter | –3 dB Cut-off Frequency | 50/100/150/200 | KHz | |||

| LNA linear output | 4 | VPP | ||||

| VCAT+ PGA | ||||||

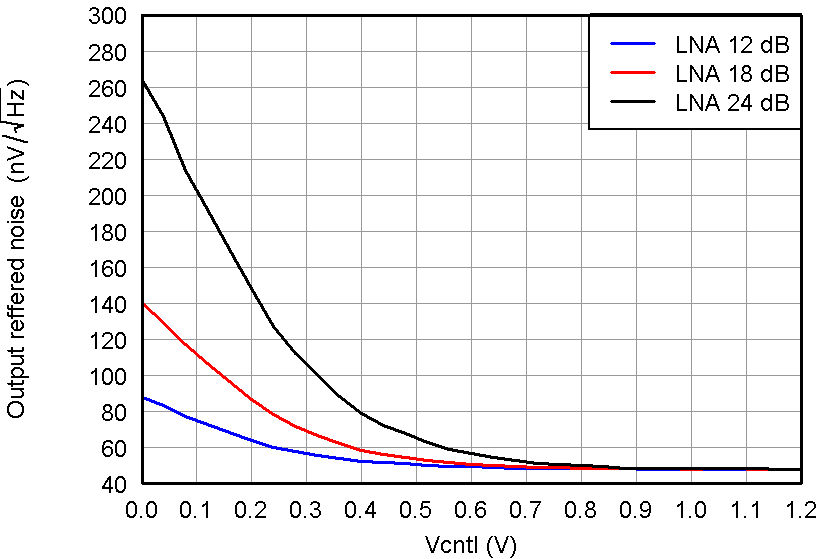

| VCAT Input Noise | 0-dB/–40-dB attenuation | 2/10.5 | nV/√Hz | |||

| PGA Input Noise | 24 dB/30 dB | 1.75 | nV/√Hz | |||

| -3dB HPF cut-off Frequency | 80 | kHz | ||||

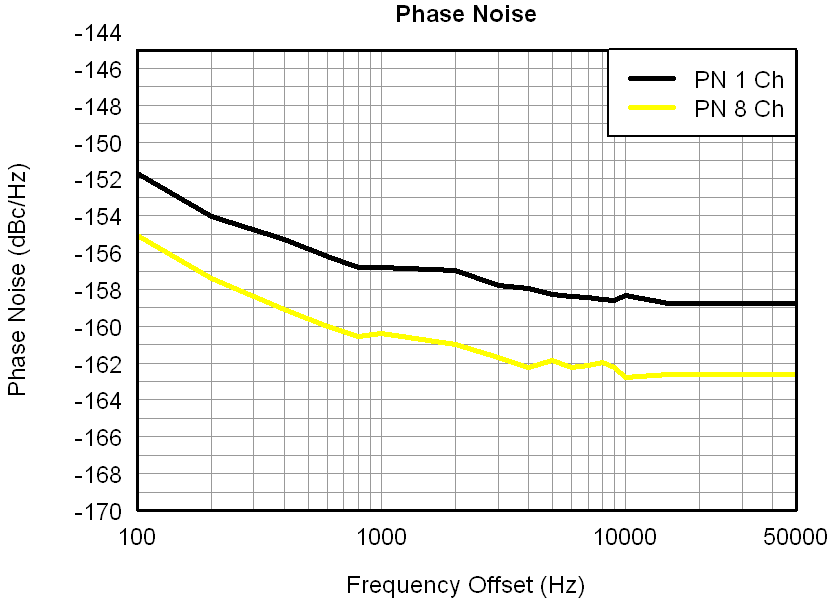

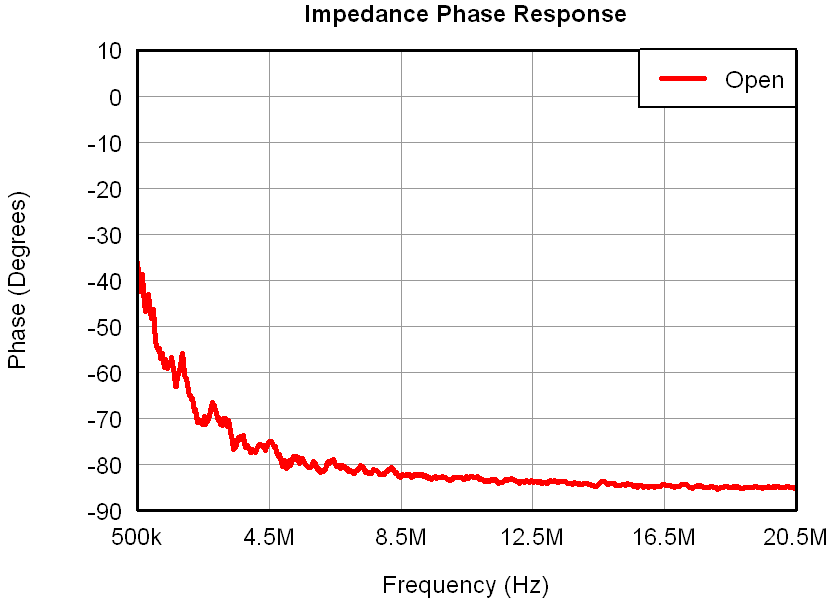

| CW DOPPLER | ||||||

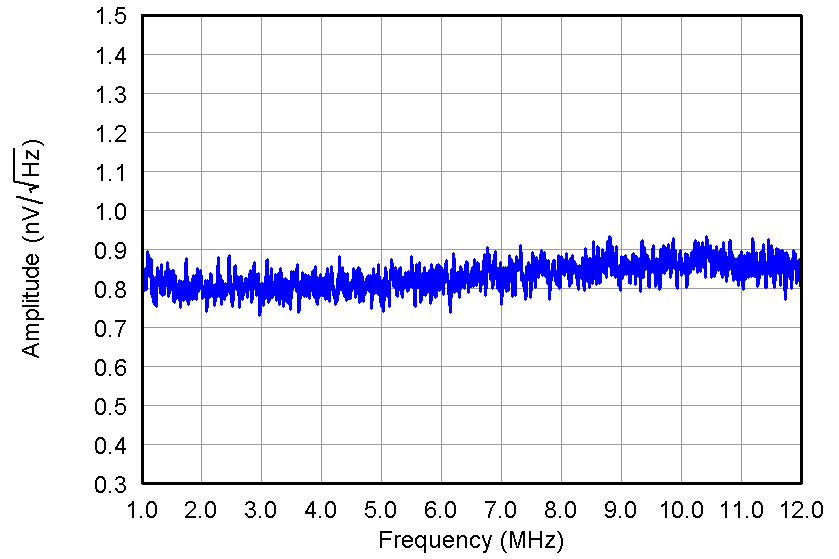

| en (RTI) | Input voltage noise (CW) | 1-channel mixer, LNA = 24 dB, 500-Ω feedback resistor | 0.8 | nV/√Hz | ||

| 8-channel mixer, LNA = 24 dB, 62.5-Ω feedback resistor | 0.33 | |||||

| en (RTO) | Output voltage noise (CW) | 1-channel mixer, LNA = 24 dB, 500-Ω feedback resistor | 12 | nV/√Hz | ||

| 8-channel mixer, LNA = 24 dB, 62.5-Ω feedback resistor | 5 | |||||

| en (RTI) | Input voltage noise (CW) | 1-channel mixer, LNA = 18 dB, 500-Ω feedback resistor | 1.1 | nV/√Hz | ||

| 8-channel mixer, LNA = 18 dB, 62.5-Ω feedback resistor | 0.5 | |||||

| en (RTO) | Output voltage noise (CW) | 1-channel mixer, LNA = 18 dB, 500-Ω feedback resistor | 8.1 | nV/√Hz | ||

| 8-channel mixer, LNA = 18 dB, 62.5-Ω feedback resistor | 4.0 | |||||

| NF | Noise figure | Rs = 100 Ω, RIN = High Z, fIN = 2 MHz (LNA, I/Q mixer and summing amplifier and filter) | 1.8 | dB | ||

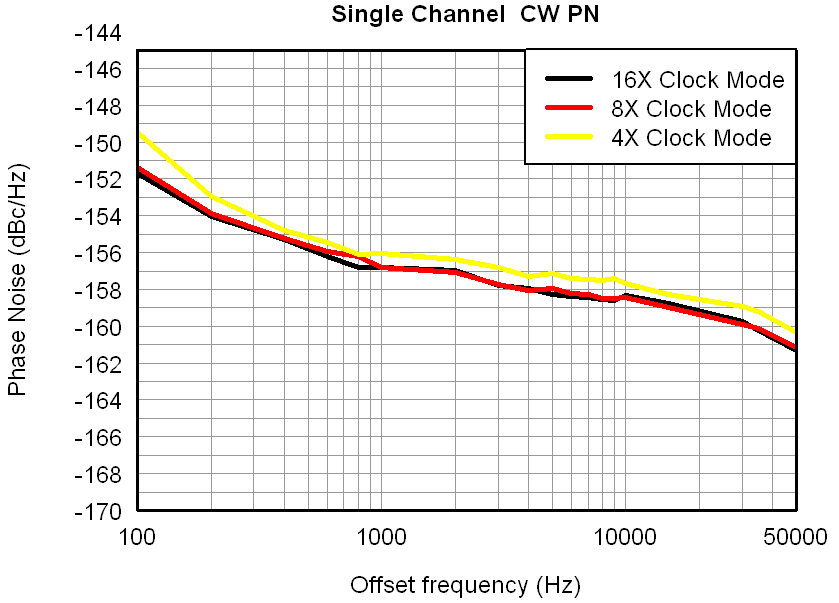

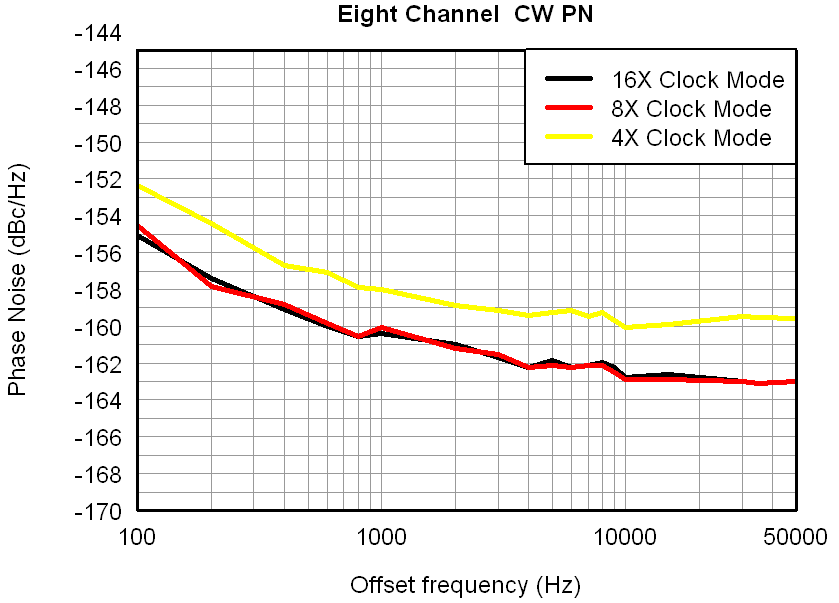

| fCW | CW Operation Range (3) | CW signal carrier frequency | 8 | MHz | ||

| CW Clock frequency | 1X CLK (16X mode) | 8 | MHz | |||

| 16X CLK(16X mode) | 128(4) | |||||

| 4X CLK (4X mode) | 32 | |||||

| AC coupled LVDS clock amplitude | CLKM_16X-CLKP_16X; CLKM_1X-CLKP_1X | 0.7 | VPP | |||

| AC coupled LVPECL clock amplitude | 1.6 | |||||

| CLK duty cycle | 1X and 16X CLKs | 33% | 66% | |||

| Common-mode voltage | Internal provided | 2.5 | V | |||

| VCMOS | CMOS Input clock amplitude | 4 | 5 | V | ||

| CW Mixer conversion loss | 4 | dB | ||||

| CW Mixer phase noise | 1 kHz off 2-MHz carrier | 156 | dBc/Hz | |||

| DR | Input dynamic range | fIN = 2 MHz, LNA = 24/18/12 dB | 160/164/165 | dBFS/Hz | ||

| IMD3 | Intermodulation distortion | f1 = 5 MHz, f2 = 5.01 MHz, both tones at –8.5 dBm amplitude, 8 channels summed up in-phase, CW feedback resistor = 87 Ω | –50 | dBc | ||

| f1 = 5 MHz, F2 = 5.01 MHz, both tones at –8.5 dBm amplitude, Single channel case, CW feed back resistor = 500 Ω | –60 | dBc | ||||

| I/Q Channel gain matching | 16X mode | ±0.04 | dB | |||

| I/Q Channel phase matching | 16X mode | ±0.1 | Degree | |||

| I/Q Channel gain matching | 4X mode | ±0.04 | dB | |||

| I/Q Channel phase matching | 4X mode | ±0.1 | Degree | |||

| Image rejection ratio | fIN = 2.01 MHz, 300-mV input amplitude, CW clock frequency = 2 MHz | –50 | dBc | |||

| CW SUMMING AMPLIFIER | ||||||

| VCMO | Common-mode voltage | Summing amplifier inputs/outputs | 1.5 | V | ||

| Summing amplifier output | 4 | VPP | ||||

| Input referred voltage noise | 100 Hz | 2 | nV/√Hz | |||

| 1 kHz | 1.2 | nV/√Hz | ||||

| 2 kHz to 100 MHz | 1 | nV/√Hz | ||||

| Input referred current noise | 2.5 | pA/√Hz | ||||

| Unit gain bandwidth | 200 | MHz | ||||

| Max output current | Linear operation range | 20 | mApp | |||

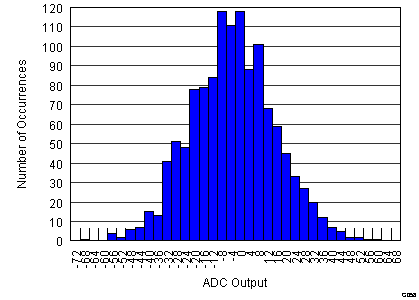

| ADC SPECIFICATIONS | ||||||

| Sample rate | 10 | 65 | MSPS | |||

| SNR | Signal-to-noise ratio | Idle channel SNR of ADC 14b | 77 | dBFS | ||

| Internal reference mode | REFP | 1.5 | V | |||

| REFM | 0.5 | V | ||||

| External reference mode | VREF_IN voltage | 1.4 | V | |||

| VREF_IN current | 50 | µA | ||||

| ADC input full-scale range | 2 | VPP | ||||

| LVDS Rate | 65 MSPS at 14 bit | 910 | Mbps | |||

| POWER DISSIPATION | ||||||

| AVDD Voltage | 3.15 | 3.3 | 3.6 | V | ||

| AVDD_ADC Voltage | 1.7 | 1.8 | 1.9 | V | ||

| AVDD_5V Voltage | 4.75 | 5 | 5.5 | V | ||

| DVDD Voltage | 1.7 | 1.8 | 1.9 | V | ||

| Total power dissipation per channel | TGC low-noise mode, 65 MSPS | 158 | 190 | mW/CH | ||

| TGC low-noise mode, 40 MSPS | 145 | |||||

| TGC medium-power mode, 40 MSPS | 114 | |||||

| TGC low-power mode, 40 MSPS | 101.5 | |||||

| AVDD (3.3V) Current | TGC low-noise mode, no signal | 202 | 240 | mA | ||

| TGC medium-power mode, no signal | 126 | |||||

| TGC low-power mode, no signal | 99 | |||||

| CW-mode, no signal | 147 | 170 | ||||

| TGC low-noise mode, 500-mVPP input,1% duty cycle | 210 | |||||

| TGC medium-power mode, 500-mVPP input, 1% duty cycle | 133 | |||||

| TGC low-power mode, 500-mVPP input, 1% duty cycle | 105 | |||||

| CW-mode, 500-mVPP input | 375 | |||||

| AVDD_5V Current | TGC mode, no signal | 25.5 | 35 | mA | ||

| CW mode, no signal, 16X clock = 32 MHz | 32 | |||||

| TGC mode, 500 mVPP input,1% duty cycle | 26 | |||||

| CW-mode, 500 mVPP input | 42.5 | |||||

| VCA Power dissipation | TGC low-noise mode, no signal | 99 | 121 | mW/CH | ||

| TGC medium-power mode, no signal | 68 | |||||

| TGC low-power mode, no signal | 55.5 | |||||

| TGC low-noise mode, 500 mVPP input,1% duty cycle | 102.5 | |||||

| TGC medium-power mode, 500 mVPP Input, 1% duty cycle | 71 | |||||

| TGC low-power mode, 500 mVPP input,1% duty cycle | 59.5 | |||||

| CW Power dissipation | No signal, ADC shutdown, CW mode, no signal, 16X clock = 32 MHz | 80 | mW/CH | |||

| 500 mVPP input, ADC shutdown , 16X clock = 32 MHz | 173 | |||||

| AVDD_ADC(1.8V) Current | 65 MSPS | 187 | 205 | mA | ||

| DVDD(1.8V) Current | 65 MSPS | 77 | 110 | mA | ||

| ADC Power dissipation/CH | 65 MSPS | 59 | 69 | mW/CH | ||

| 50 MSPS | 51 | |||||

| 40 MSPS | 46 | |||||

| 20 MSPS | 35 | |||||

| Power dissipation in power down mode | PDN_VCA = high, PDN_ADC = high | 25 | mW/CH | |||

| Complete power-down, PDN_Global = high | 0.6 | |||||

| Power-down response time | Time taken to enter power down | 1 | µs | |||

| Power-up response time | VCA power down | 2µs+1% of PDN time | µs | |||

| ADC power down | 1 | |||||

| Complete power down | 2.5 | ms | ||||

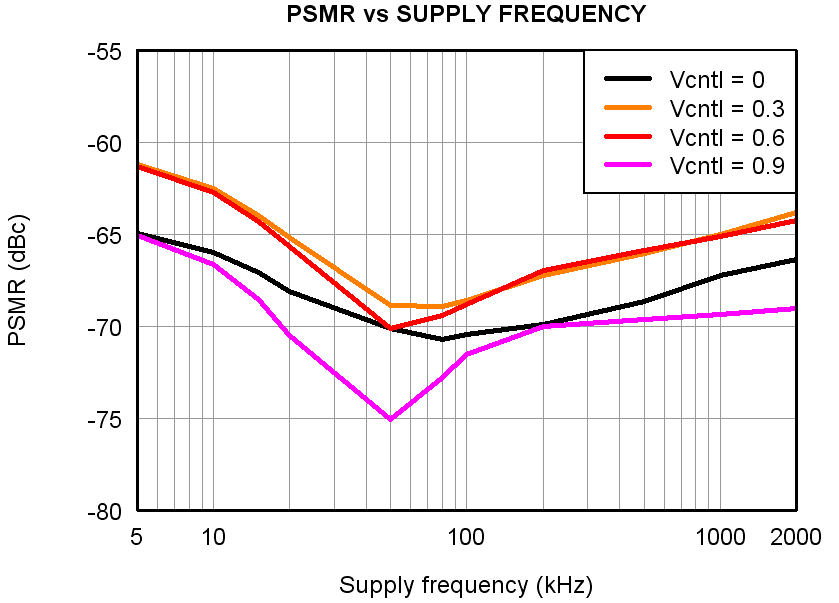

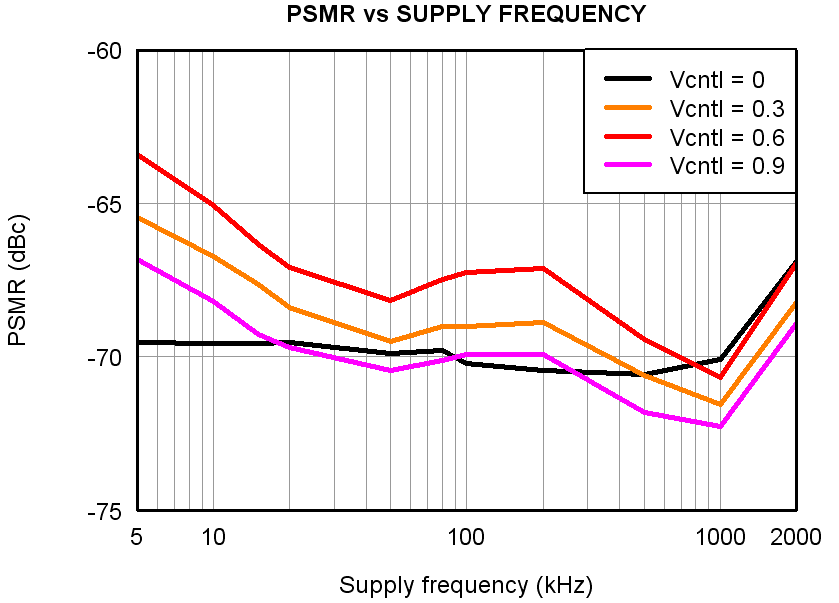

| Power supply modulation ratio, AVDD and AVDD_5V | fIN = 5 MHz, at 50-mVPP noise at 1 kHz on supply(1) | –65 | dBc | |||

| fIN = 5 MHz, at 50-mVPP noise at 50 kHz on supply(1) | –65 | dBc | ||||

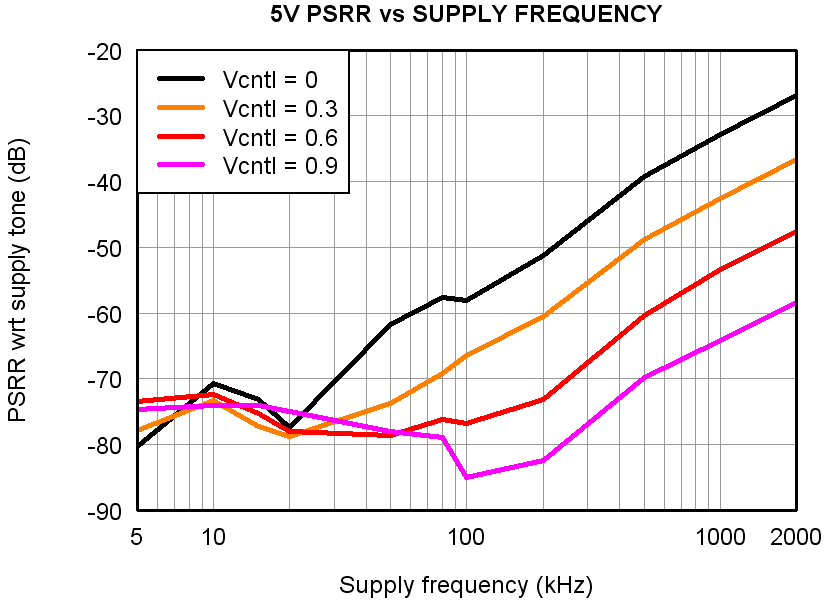

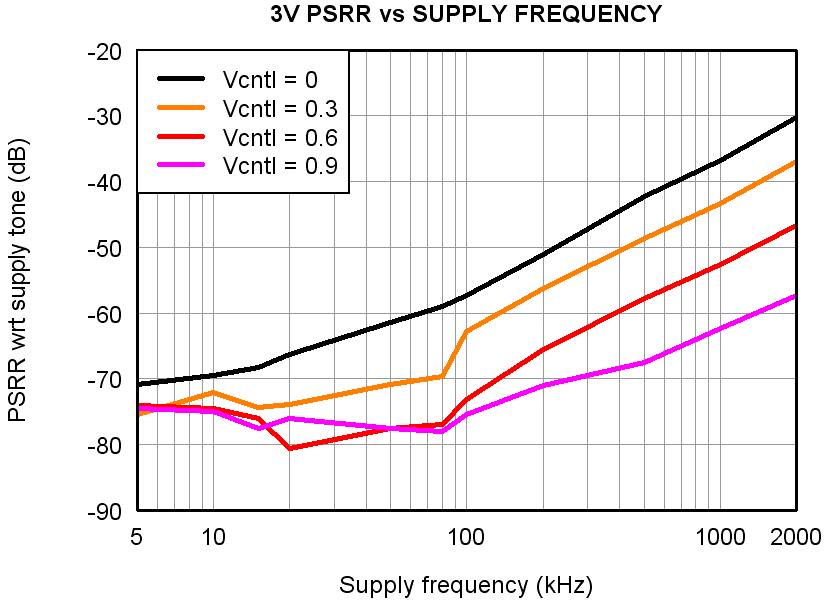

| Power supply rejection ratio | f = 10 kHz,VCNTL = 0 V (high gain), AVDD | –40 | dBc | |||

| f = 10 kHz,VCNTL = 0 V (high gain), AVDD_5V | –55 | dBc | ||||

| f = 10 kHz,VCNTL = 1 V (low gain), AVDD | –50 | dBc | ||||

(1) PSMR specification is with respect to input signal amplitude.

(2) Noise correlation factor is defined as Nc/(Nu+Nc), where Nc is the correlated noise power in single channel; and Nu is the uncorrelated noise power in single channel. Its measurement follows the below equation, in which the SNR of single channel signal and the SNR of summed eight channel signal are measured.

(3) In the 8X, 4X, and 1X modes, higher CW signal frequencies up to 15 MHz can be supported with small degradation in performance, see application information: CW clock selection.

7.6 Digital Characteristics

Typical values are at +25°C, AVDD = 3.3 V, AVDD_5 = 5 V and AVDD_ADC = 1.8 V, DVDD = 1.8 V, 14 bit sample rate = 65 MSPS (unless otherwise noted). Minimum and maximum values are across the full temperature range: TMIN = 0°C to TMAX = 85°C.| PARAMETER | TEST CONDITIONS | MIN | TYP | MAX | UNIT(1) | |

|---|---|---|---|---|---|---|

| DIGITAL INPUTS AND OUTPUTS | ||||||

| VIH | Logic high input voltage | 2 | 3.3 | V | ||

| VIL | Logic low input voltage | 0 | 0.3 | V | ||

| Logic high input current | 200 | µA | ||||

| Logic low input current | 200 | µA | ||||

| Input capacitance | 5 | pF | ||||

| VOH | Logic high output voltage | SDOUT pin | DVDD | V | ||

| VOL | Logic low output voltage | SDOUT pin | 0 | V | ||

| LVDS OUTPUTS | ||||||

| Output differential voltage | With 100-Ω external differential termination | 400 | mV | |||

| Output offset voltage | Common-mode voltage | 1100 | mV | |||

| FCLKP and FCLKM | 1X clock rate | 10 | 65 | MHz | ||

| DCLKP and DCLKM | 7X clock rate | 70 | 455 | MHz | ||

| 6X clock rate | 60 | 390 | MHz | |||

| tsu | Data setup time(2) | 350 | ps | |||

| th | Data hold time(2) | 350 | ps | |||

| ADC INPUT CLOCK | ||||||

| CLOCK frequency | 10 | 65 | MSPS | |||

| Clock duty cycle | 45% | 50% | 55% | |||

| Clock input amplitude, differential(VCLKP_ADC–VCLKM_ADC) | Sine-wave, ac-coupled | 0.5 | VPP | |||

| LVPECL, ac-coupled | 1.6 | VPP | ||||

| LVDS, ac-coupled | 0.7 | VPP | ||||

| Common-mode voltage | biased internally | 1 | V | |||

| Clock input amplitude VCLKP_ADC (single-ended) | CMOS clock | 1.8 | VPP | |||

(1) The DC specifications refer to the condition where the LVDS outputs are not switching, but are permanently at a valid logic level 0 or 1 with 100-Ω external termination.

(2) Setup and hold time specifications take into account the effect of jitter on the output data and clock. These specifications also assume that the data and clock paths are perfectly matched within the receiver. Any mismatch in these paths within the receiver would appear as reduced timing margins

7.7 Switching Characteristics

Typical values are at 25°C, AVDD_5V = 5 V, AVDD = 3.3 V, AVDD_ADC = 1.8 V, DVDD = 1.8 V, differential clock, CLOAD = 5 pF, RLOAD = 100 Ω, 14 bit, sample rate = 65MSPS (unless otherwise noted). Minimum and maximum values are across the full temperature range TMIN = 0°C to TMAX = 85°C with AVDD_5V = 5 V, AVDD = 3.3 V, AVDD_ADC = 1.8 V, DVDD = 1.8 V(1)(1) Timing parameters are ensured by design and characterization; not production tested.

7.8 Timing Requirements

Minimum values across full temperature range TMIN = 0°C to TMAX = 85°C, AVDD_5V =5 V, AVDD = 3.3 V, AVDD_ADC = 1.8 V, DVDD = 1.8 V| PARAMETER | DESCRIPTION | MIN | TYP | MAX | UNIT |

|---|---|---|---|---|---|

| t1 | SCLK period | 50 | ns | ||

| t2 | SCLK high time | 20 | ns | ||

| t3 | SCLK low time | 20 | ns | ||

| t4 | Data setup time | 5 | ns | ||

| t5 | Data hold time | 5 | ns | ||

| t6 | SEN fall to SCLK rise | 8 | ns | ||

| t7 | Time between last SCLK rising edge to SEN rising edge | 8 | ns | ||

| t8 | SDOUT delay | 12 | 20 | 28 | ns |

7.9 Output Interface Timing(1)(2)(3)

(1) FCLK timing is the same as for the output data lines. It has the same relation to DCLK as the data pins. Setup and hold are the same for the data and the frame clock.

(2) Data valid is logic HIGH = +100 mV and logic LOW = –100 mV

(3) Timing parameters are ensured by design and characterization; not production tested.

spacer

NOTE

The previous timing data can be applied to 12-bit or 16-bit LVDS rates as well. For example, the maximum LVDS output rate at 65 MHz and 14-bit is equal to 910 MSPS, which is approximately equivalent to the rate at 56 MHz and 16-bit.

Figure 1. LVDS Timing Diagrams

Figure 1. LVDS Timing Diagrams

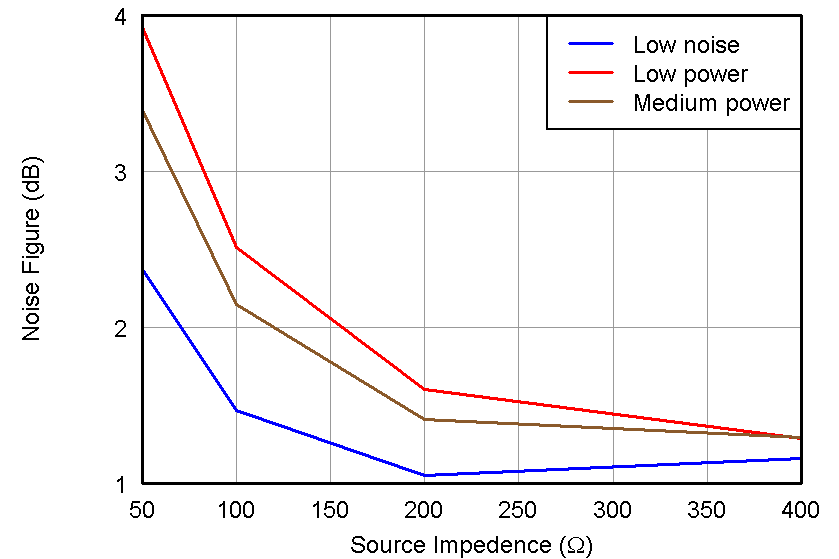

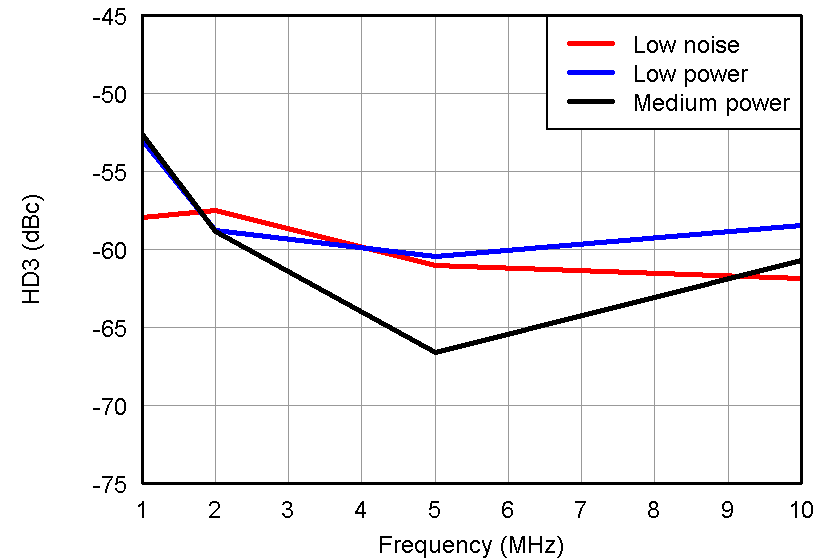

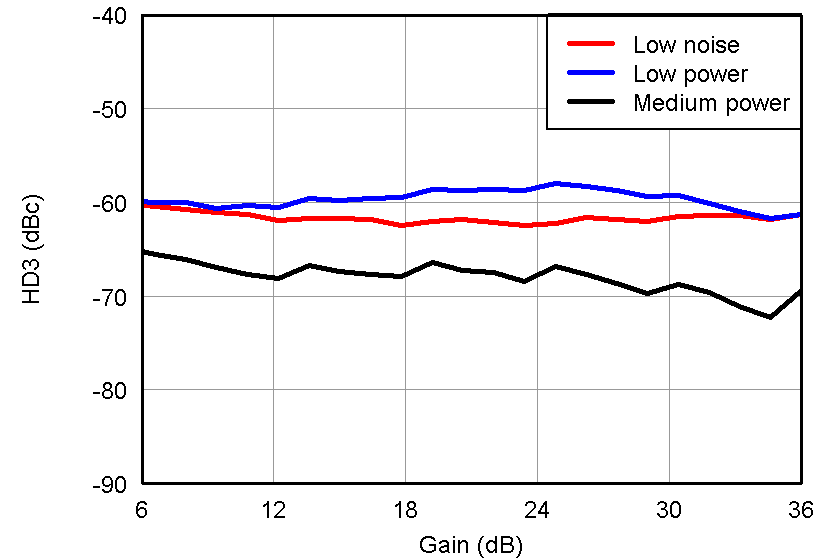

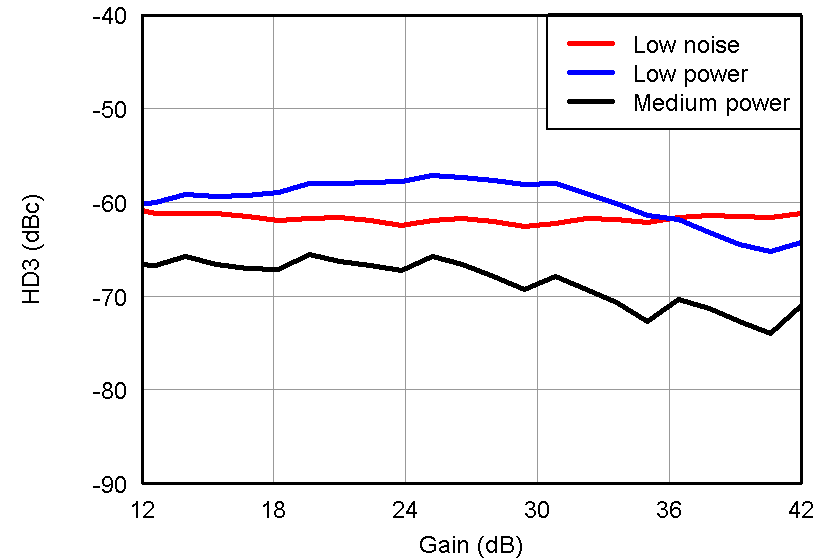

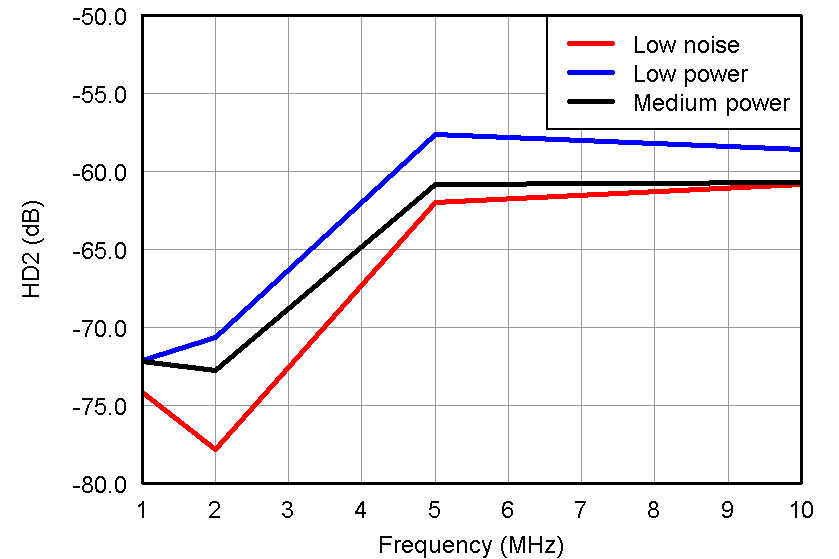

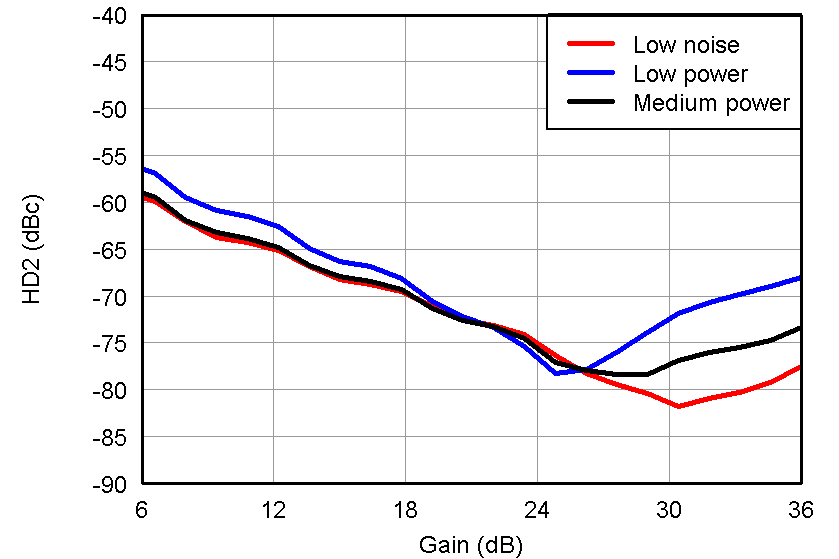

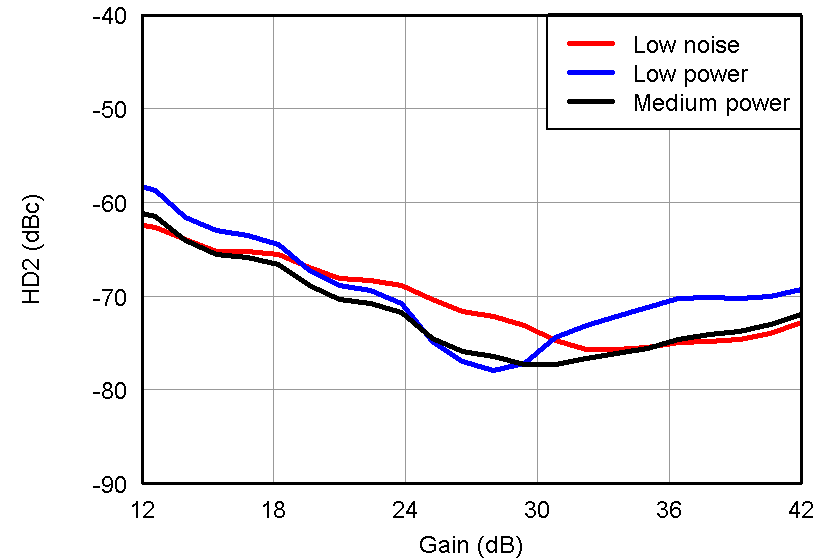

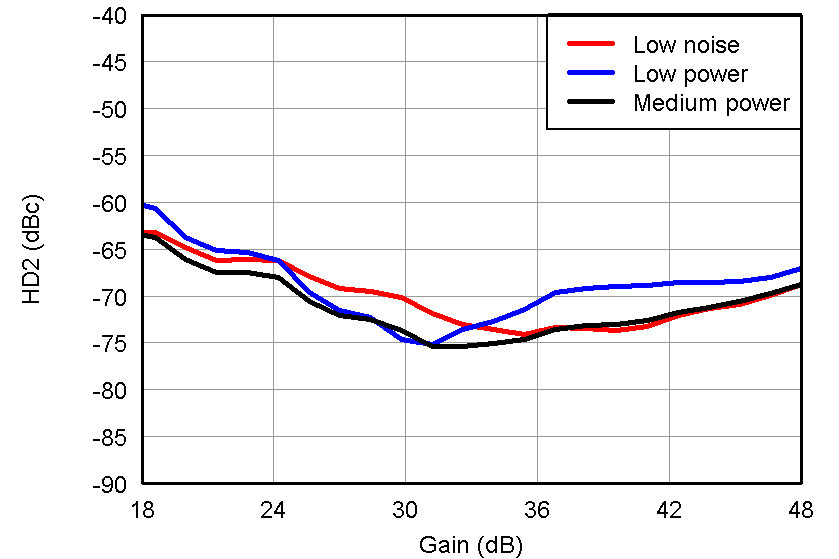

7.10 Typical Characteristics

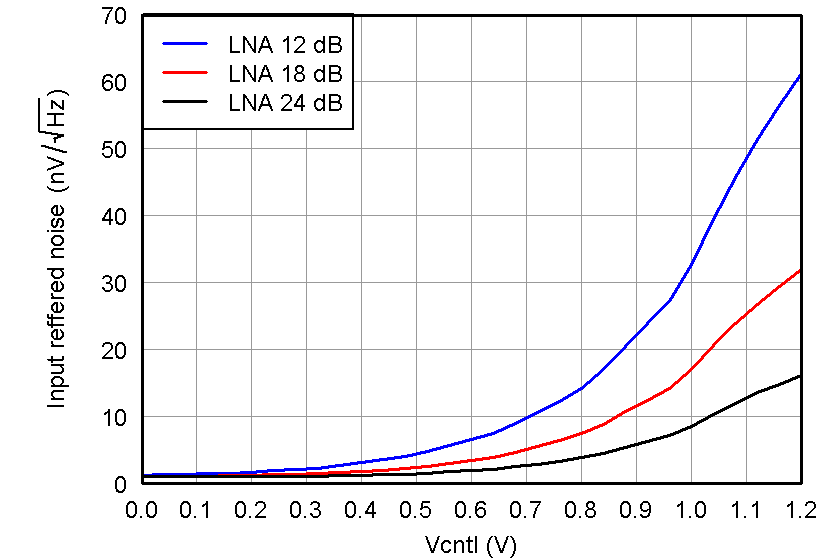

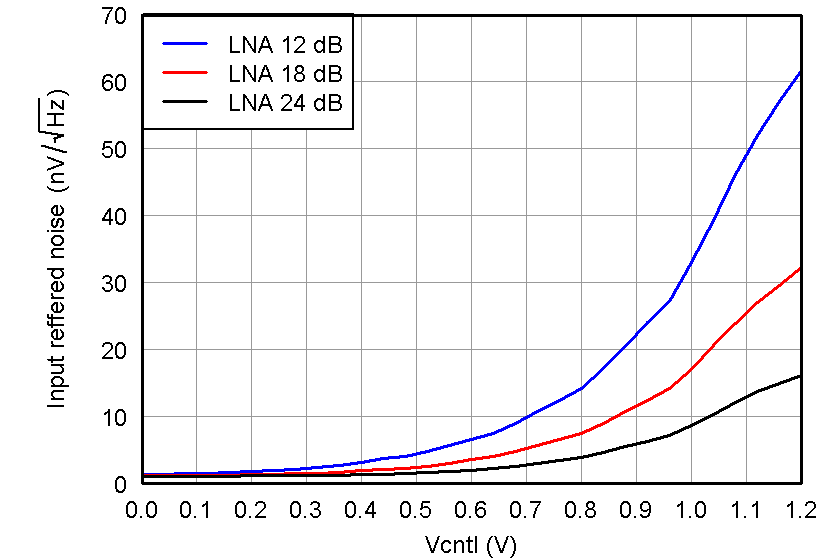

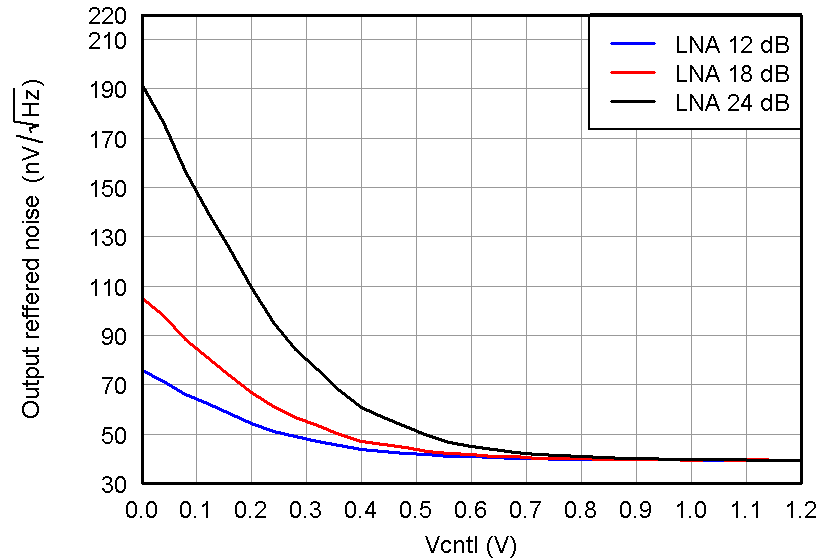

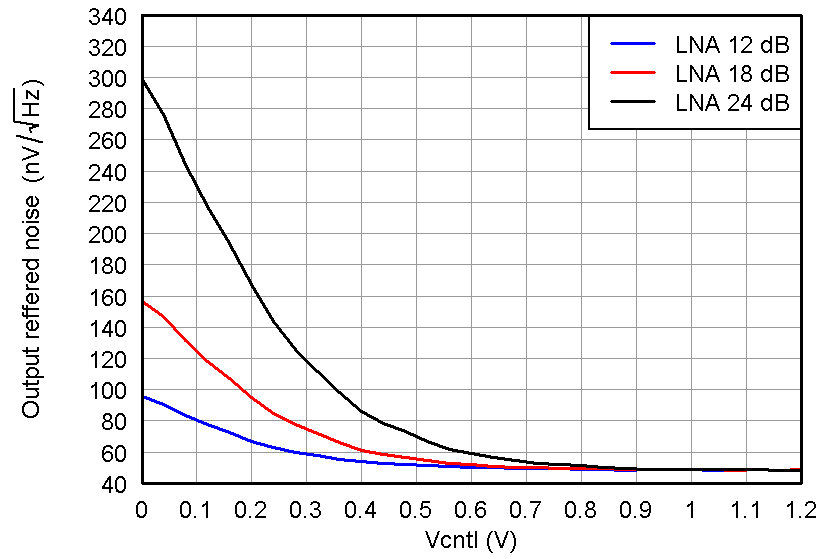

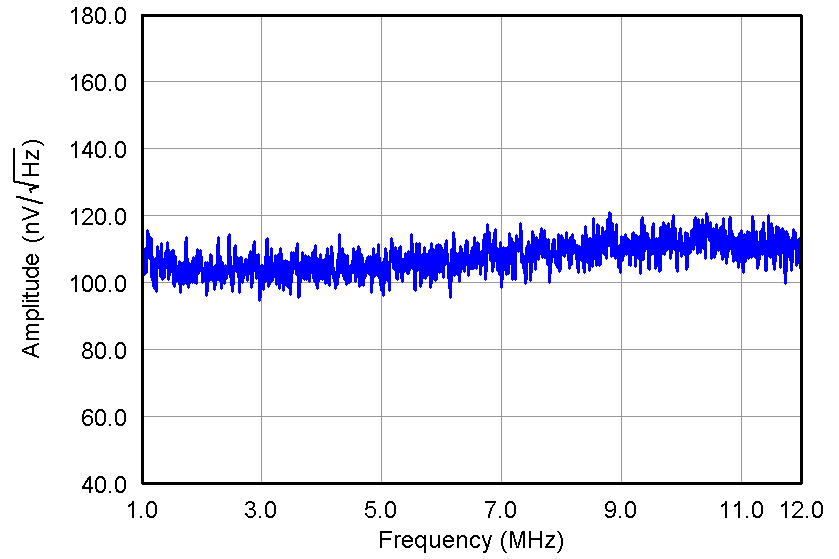

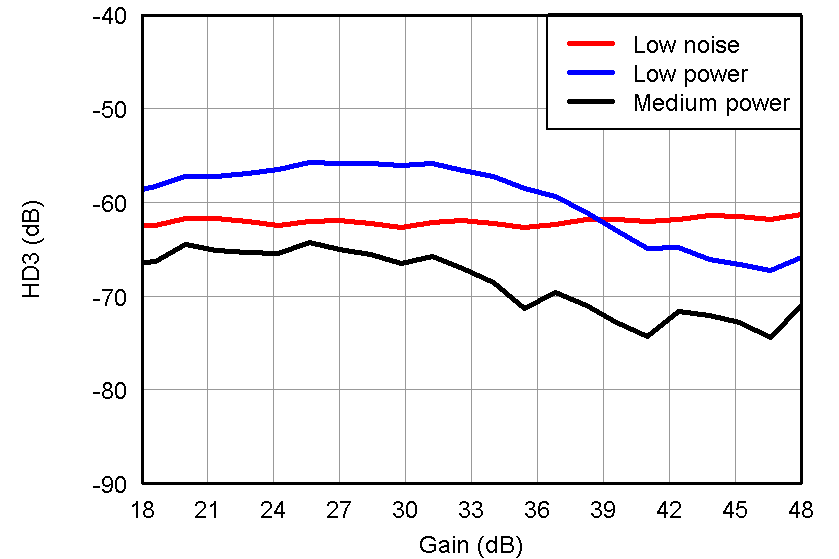

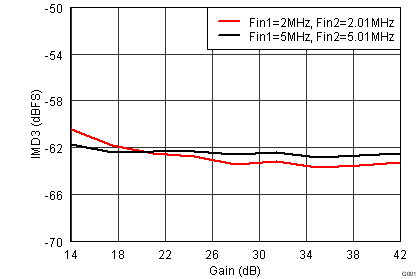

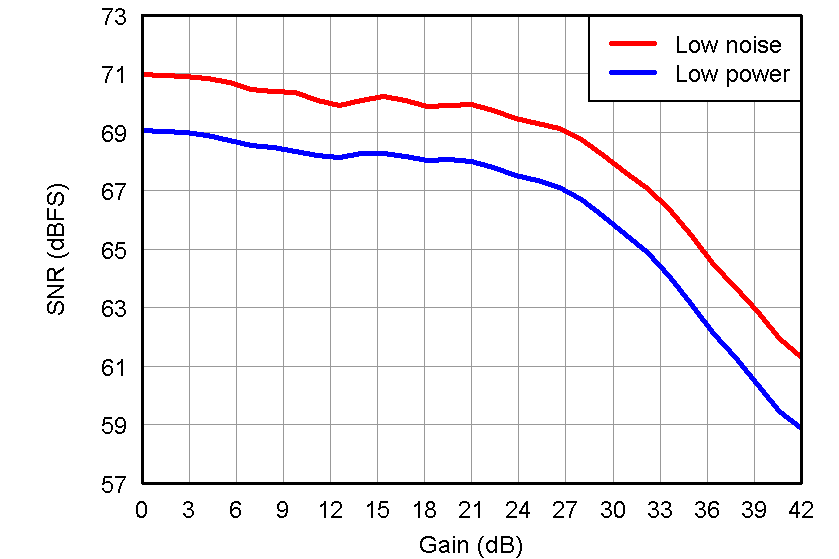

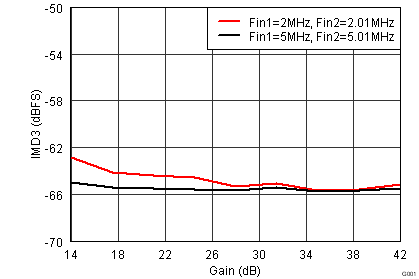

at AVDD_5 V = 5 V, AVDD = 3.3 V, AVDD_ADC = 1.8 V, DVDD = 1.8 V, ac-coupled with 0.1-µF caps at INP and 15-nF caps at INM, No active termination, VCNTL = 0 V, fIN = 5 MHz, LNA = 18 dB, PGA = 24 dB, 14 bit, sample rate = 65 MSPS, LPF filter = 15 MHz, low-noise mode, VOUT = –1 dBFS, 500-Ω CW feedback resistor, CMOS 16X clock, ADC configured in internal-reference mode, single-ended VCNTL mode, VCNTLM = GND, and ambient temperature TA = 25°C (unless otherwise noted)

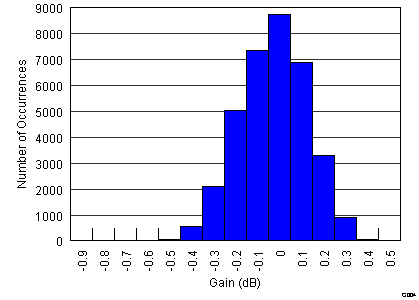

| VCNTL = 0.3 V (34951 channels) |

| VCNTL = 0.9 V (34951 channels) |

| fIN = 2 MHz |

| Vin = 500 mVPP and VOUT = –1 dBFS |

| LNA = 12 dB and PGA = 24 dB and VOUT = –1 dBFS |

| LNA = 18 dB and PGA = 24 dB and VOUT = –1 dBFS |

| LNA = 24 dB and PGA = 24 dB and VOUT = –1 dBFS |

| Fout1 = –7dBFS and Fout2 = –7dBFS |

| 100 mVPP Supply Noise With Different Frequencies |

| 100 mVPP Supply Noise With Different Frequencies |

| LNA = 18 dB and PGA = 24 dB |

| VIN = 50 mVPP/100 µVPP, Max Gain |

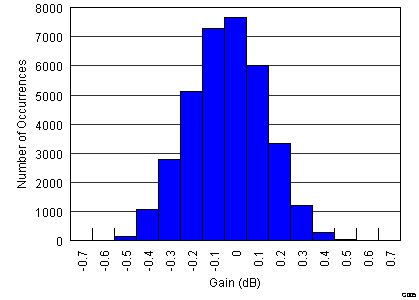

| VCNTL = 0.6 V (34951 channels) |

| VCNTL = 0 V (1247 channels) |

![AFE5808A LNA High-Pass Filter

Response vs Reg59 [3:2] AFE5808A Figure_13_hpf_vcaoff.gif](/ods/images/SLOS729D/Figure_13_hpf_vcaoff.gif)

| fIN = 2 MHz |

| fIN = 2 MHz |

| Vin = 500 mVPP and VOUT = –1 dBFS |

| LNA = 12 dB and PGA = 24 dB and VOUT = –1 dBFS |

| LNA = 18 dB and PGA = 24 dB and VOUT = –1 dBFS |

| LNA = 24 dB and PGA = 24 dB and VOUT = –1 dBFS |

| Fout1 = –1 dBFS and Fout2 = –21 dBFS |

| 100 mVPP Supply Noise With Different Frequencies |

| 100 mVPP Supply Noise With Different Frequencies |

| LNA = 18 dB and PGA = 24 dB |

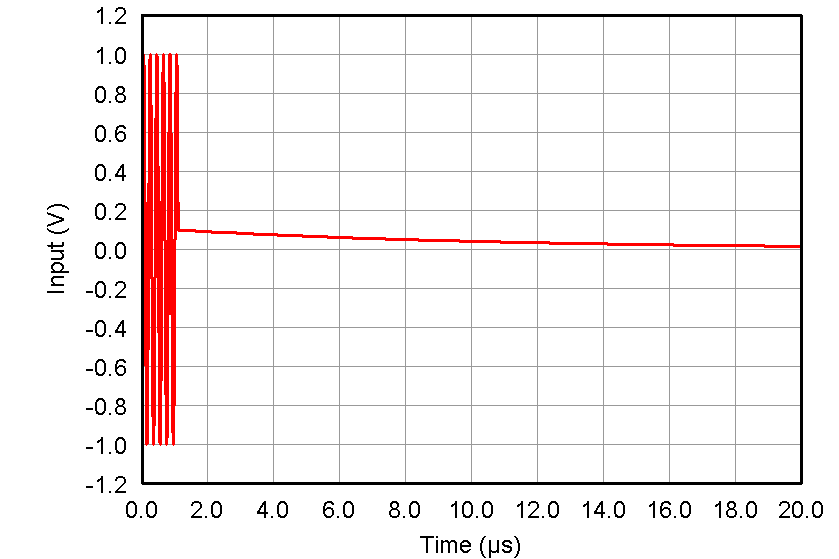

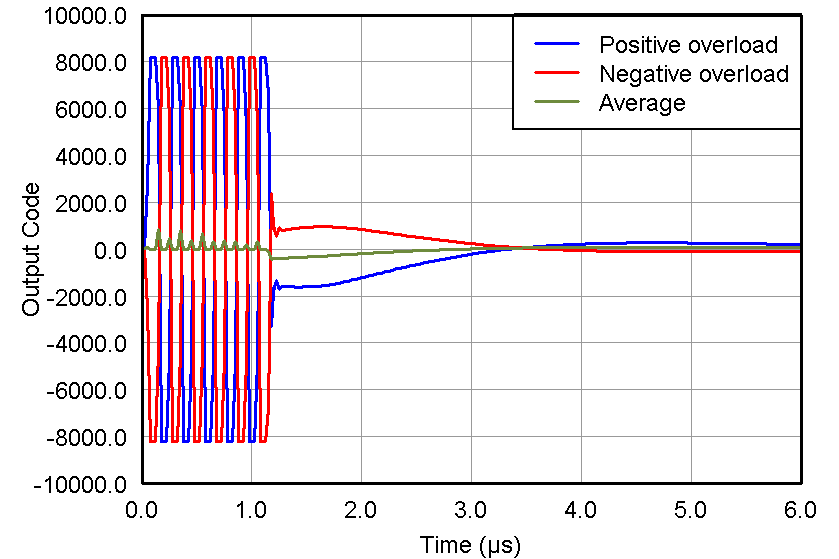

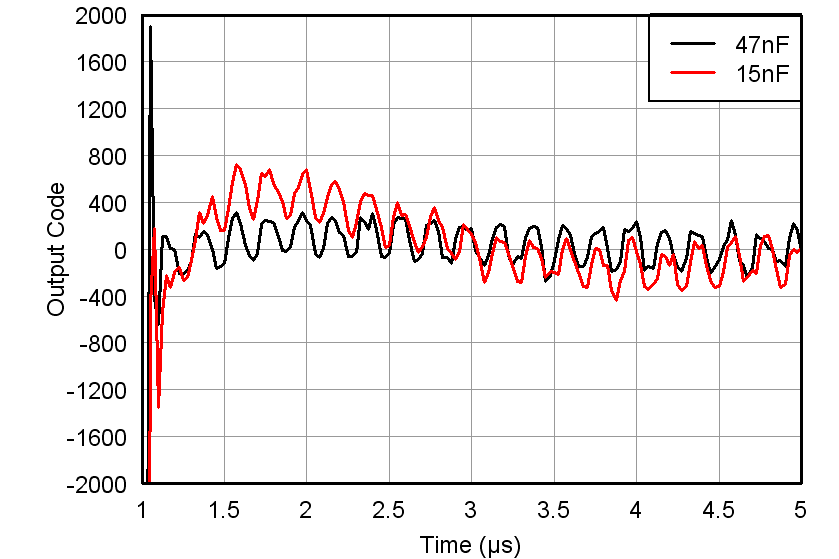

| VIN = 2 VPP, PRF = 1 kHz, Gain = 21 dB |

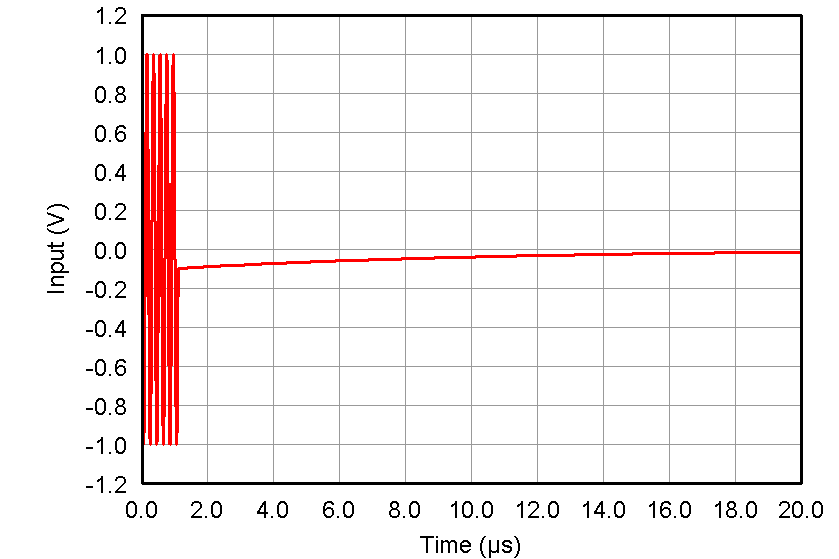

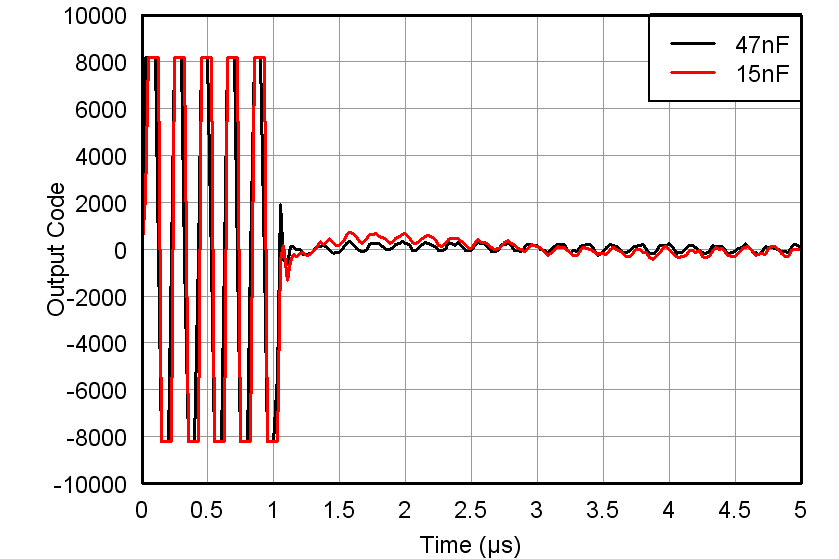

| VIN = 50 mVPP/100 µVPP, Max Gain |