SLUSFC9 December 2023 BQ76972

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Device Comparison Table

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information BQ76952

- 6.5 Supply Current

- 6.6 Digital I/O

- 6.7 LD Pin

- 6.8 Precharge (PCHG) and Predischarge (PDSG) FET Drive

- 6.9 FUSE Pin Functionality

- 6.10 REG18 LDO

- 6.11 REG0 Pre-regulator

- 6.12 REG1 LDO

- 6.13 REG2 LDO

- 6.14 Voltage References

- 6.15 Coulomb Counter

- 6.16 Coulomb Counter Digital Filter (CC1)

- 6.17 Current Measurement Digital Filter (CC2)

- 6.18 Current Wake Detector

- 6.19 Analog-to-Digital Converter

- 6.20 Cell Voltage Measurement Accuracy

- 6.21 Cell Balancing

- 6.22 Cell Open Wire Detector

- 6.23 Internal Temperature Sensor

- 6.24 Thermistor Measurement

- 6.25 Internal Oscillators

- 6.26 High-side NFET Drivers

- 6.27 Comparator-Based Protection Subsystem

- 6.28 Timing Requirements - I2C Interface, 100kHz Mode

- 6.29 Timing Requirements - I2C Interface, 400kHz Mode

- 6.30 Timing Requirements - HDQ Interface

- 6.31 Timing Requirements - SPI Interface

- 6.32 Interface Timing Diagrams

- 6.33 Typical Characteristics

-

7 Detailed

Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 BQ76972 Device Versions

- 7.4 Diagnostics

- 7.5 Device Configuration

- 7.6

Measurement Subsystem

- 7.6.1 Voltage Measurement

- 7.6.2 General Purpose ADCIN Functionality

- 7.6.3 Coulomb Counter and Digital Filters

- 7.6.4 Synchronized Voltage and Current Measurement

- 7.6.5 Internal Temperature Measurement

- 7.6.6 Thermistor Temperature Measurement

- 7.6.7 Factory Trim of Voltage ADC

- 7.6.8 Cell Voltage Measurement Accuracy

- 7.6.9 Voltage Calibration (ADC Measurements)

- 7.6.10 Voltage Calibration (COV and CUV Protections)

- 7.6.11 Current Calibration

- 7.6.12 Temperature Calibration

- 7.7 Primary and Secondary Protection Subsystems

- 7.8

Device

Hardware Features

- 7.8.1 Voltage References

- 7.8.2 ADC Multiplexer

- 7.8.3 LDOs

- 7.8.4 Standalone Versus Host Interface

- 7.8.5 Multifunction Pin Controls

- 7.8.6 RST_SHUT Pin Operation

- 7.8.7 CFETOFF, DFETOFF, and BOTHOFF Pin Functionality

- 7.8.8 ALERT Pin Operation

- 7.8.9 DDSG and DCHG Pin Operation

- 7.8.10 Fuse Drive

- 7.8.11 Cell Open Wire

- 7.8.12 Low Frequency Oscillator

- 7.8.13 High Frequency Oscillator

- 7.9 Device Functional Modes

- 7.10 Serial Communications Interface

- 7.11 Cell Balancing

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Revision History

- 11Mechanical, Packaging, Orderable Information

Package Options

Mechanical Data (Package|Pins)

- PFB|48

Thermal pad, mechanical data (Package|Pins)

- PFB|48

Orderable Information

8.5 FET Driver Turn-Off

The high-side CHG and DSG FET drivers operate differently when they are triggered to turn off their respective FET. The CHG driver includes an internal switch which discharges the CHG pin toward the BAT pin level. The DSG FET driver will discharge the DSG pin toward the LD pin level, but it includes a more complex structure than just a switch, to support a faster turn off.

When the DSG driver is triggered to turn off, the device will initially begin discharging the DSG pin toward VSS. However, since the PACK+ terminal may not fall to a voltage near VSS quickly, the DSG FET gate should not be driven significantly below PACK+, otherwise the DSG FET may be damaged due to excessive negative gate-source voltage. Thus, the device monitors the voltage on the LD pin (which is connected to PACK+ through an external series resistor) and will stop the discharge when the DSG pin voltage drops below the LD pin voltage. When the discharge has stopped, the DSG pin voltage may relax back above the LD pin voltage, at which point the device will again discharge the DSG pin toward VSS, until the DSG gate voltage again falls below the LD pin voltage. This repeats in a series of pulses which over time discharge the DSG gate to the voltage of the LD pin. This pulsing continues for approximately 100 μs to 200 μs, after which the driver remains in a high impedance state if within approximately 500 mV of the voltage of the LD pin. The external resistor between the DSG gate and source then discharges the remaining FET VGS voltage so the FET remains off.

The external series gate resistor between the DSG pin and the DSG FET gate is used to adjust the speed of the turn-off transient. A low resistance (such as 100 Ω) provides a fast turn-off during a short circuit event, but this may result in an overly large inductive spike at the top of stack when the FET is disabled. A larger resistor value (such as 1 kΩ or 4.7 kΩ) will reduce this speed and the corresponding inductive spike level.

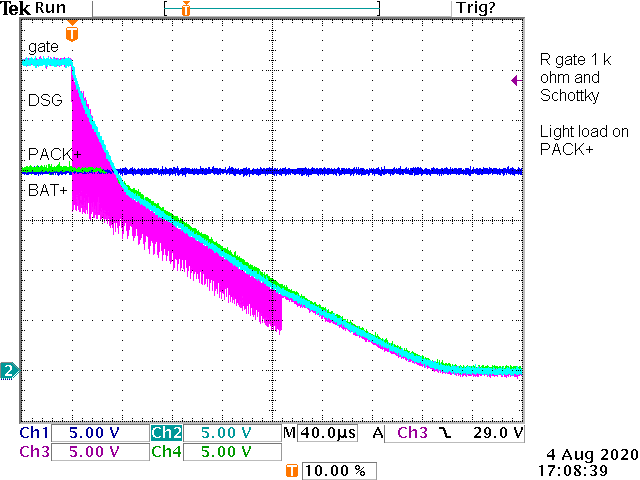

Oscilloscope captures of DSG driver turn-off are shown below, with the DSG pin driving the gate of a CSD19536KCS NFET, which has a typical Ciss of 9250 pF. Figure 8-6 shows the signals when using a 1-kΩ series gate resistor between the DSG pin and the FET gate, and a light load on PACK+, such that the voltage on PACK+ drops slowly as the FET is disabled. The pulsing on the DSG pin can be seen lasting for approximately 170 μs.

Figure 8-6 Moderate Speed DSG FET Turn-Off, Using a 1-kΩ Series Gate Resistor, and a Light Load on PACK+

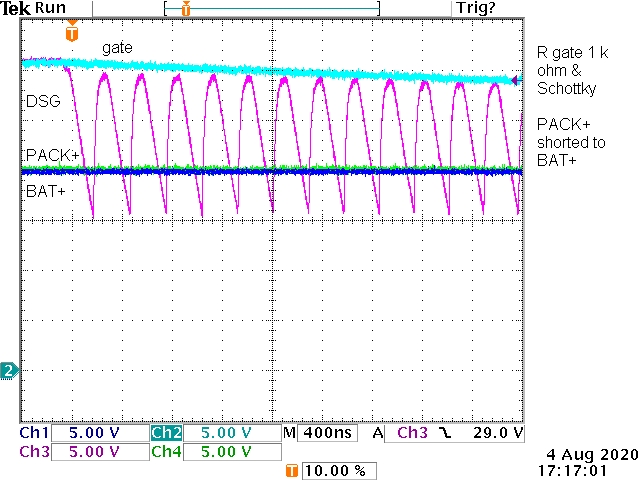

A zoomed-in version of the pulsing generated by the DSG pin is shown in Figure 8-7, this time with PACK+ shorted to the top of stack.

Figure 8-7 Zoomed-In View of the Pulsing on the DSG Pin During FET Turn-Off

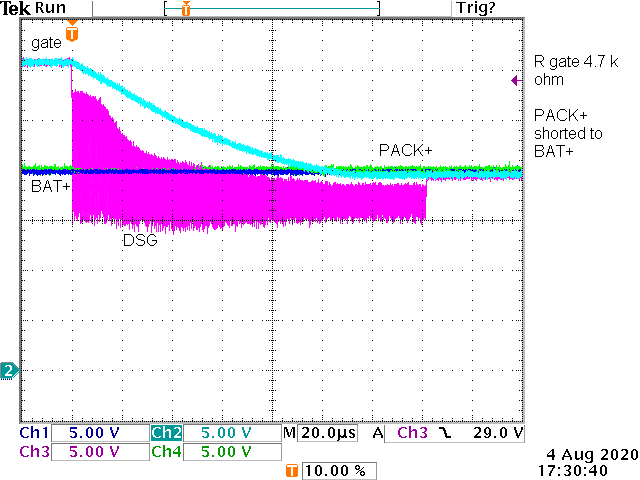

A slower turn-off case is shown in Figure 8-8, using a 4.7-kΩ series gate resistor, and the PACK+ connector shorted to the top of stack.

Figure 8-8 A Slower Turn-Off Case Using a 4.7-kΩ Series Gate Resistor, and the PACK+ Connector Shorted to the Top of the Stack

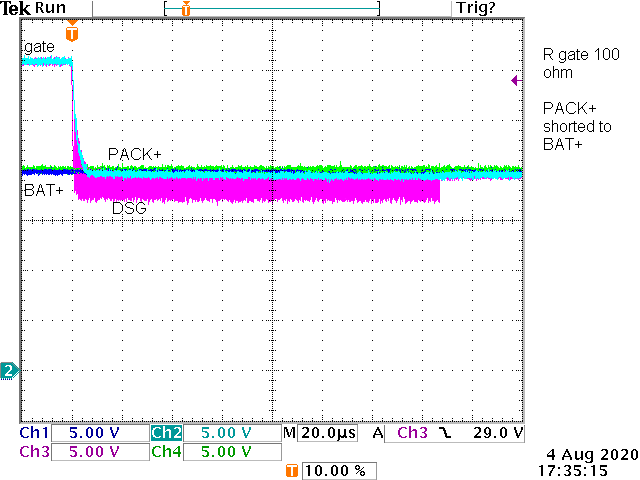

A fast turn-off case is shown in Figure 8-9, in which a 100-Ω series gate resistor is used between the DSG pin and the FET gate.

Figure 8-9 A Fast Turn-Off Case with a 100-Ω Series Gate Resistor