SLPS416C June 2014 – March 2015 CSD95372AQ5M

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Layout

- 10Application Schematic

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- DQP|12

Thermal pad, mechanical data (Package|Pins)

Orderable Information

1 Features

- 60 A Continuous Operating Current Capability

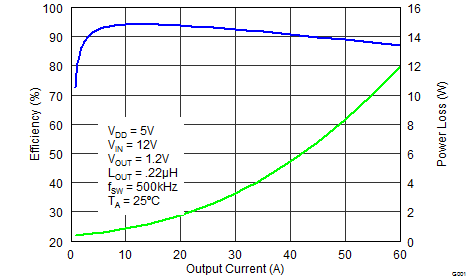

- 92.4% System Efficiency at 30 A

- Ultra-Low Power Loss of 3.3 W at 30 A

- High Frequency Operation (up to 2 MHz)

- High Density - SON 5 x 6 mm Footprint

- Ultra-Low Inductance Package

- System Optimized PCB Footprint

- 3.3 V and 5 V PWM Signal Compatible

- Diode Emulation Mode with FCCM

- Analog Temperature Output

- Input Voltages up to 16 V

- Tri-State PWM Input

- Integrated Bootstrap Switch

- Optimized Dead Time for Shoot Through Protection

- RoHS Compliant – Lead-Free Terminal Plating

- Halogen Free

2 Applications

- Multiphase Synchronous Buck Converter

- High Frequency Applications

- High Current, Low Duty Cycle Applications

- Point-of-Load DC-DC Converters

- Memory and Graphic Cards

- Desktop and Server VR11.x and VR12.x for

V-Core Synchronous Buck Converters

3 Description

The CSD95372AQ5M NexFET™ Power Stage is a highly optimized design for use in a high power, high density Synchronous Buck converters. This product integrates the driver IC and NexFET technology to complete the power stage switching function. The driver IC has a built-in selectable diode emulation function that enables DCM operation to improve light load efficiency. This combination produces high current, high efficiency, and high speed switching capability in a small 5 x 6 mm outline package. It also integrates the temperature sensing functionality to simplify system design and improve accuracy. In addition, the PCB footprint has been optimized to help reduce design time and simplify the completion of the overall system design.

Device Information(1)

| Device | Media | Qty | Package | Ship |

|---|---|---|---|---|

| CSD95372AQ5M | 13-Inch Reel | 2500 | SON 5 mm × 6 mm Package |

Tape and Reel |

| CSD95372AQ5MT | 7-Inch Reel | 250 |

Application Diagram

Typical Power Stage Efficiency and Power Loss