SNVSCA9 October 2022 LM5012

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Control Architecture

- 8.3.2 Internal VCC Regulator and Bootstrap Capacitor

- 8.3.3 Regulation Comparator

- 8.3.4 Internal Soft Start

- 8.3.5 On-Time Generator

- 8.3.6 Current Limit

- 8.3.7 N-Channel Buck Switch and Driver

- 8.3.8 Schottky Diode Selection

- 8.3.9 Enable and Undervoltage Lockout (EN/UVLO)

- 8.3.10 Power Good (PGOOD)

- 8.3.11 Thermal Protection

- 8.4 Device Functional Modes

- 9 Application and Implementation

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

- DDA|8

Thermal pad, mechanical data (Package|Pins)

- DDA|8

Orderable Information

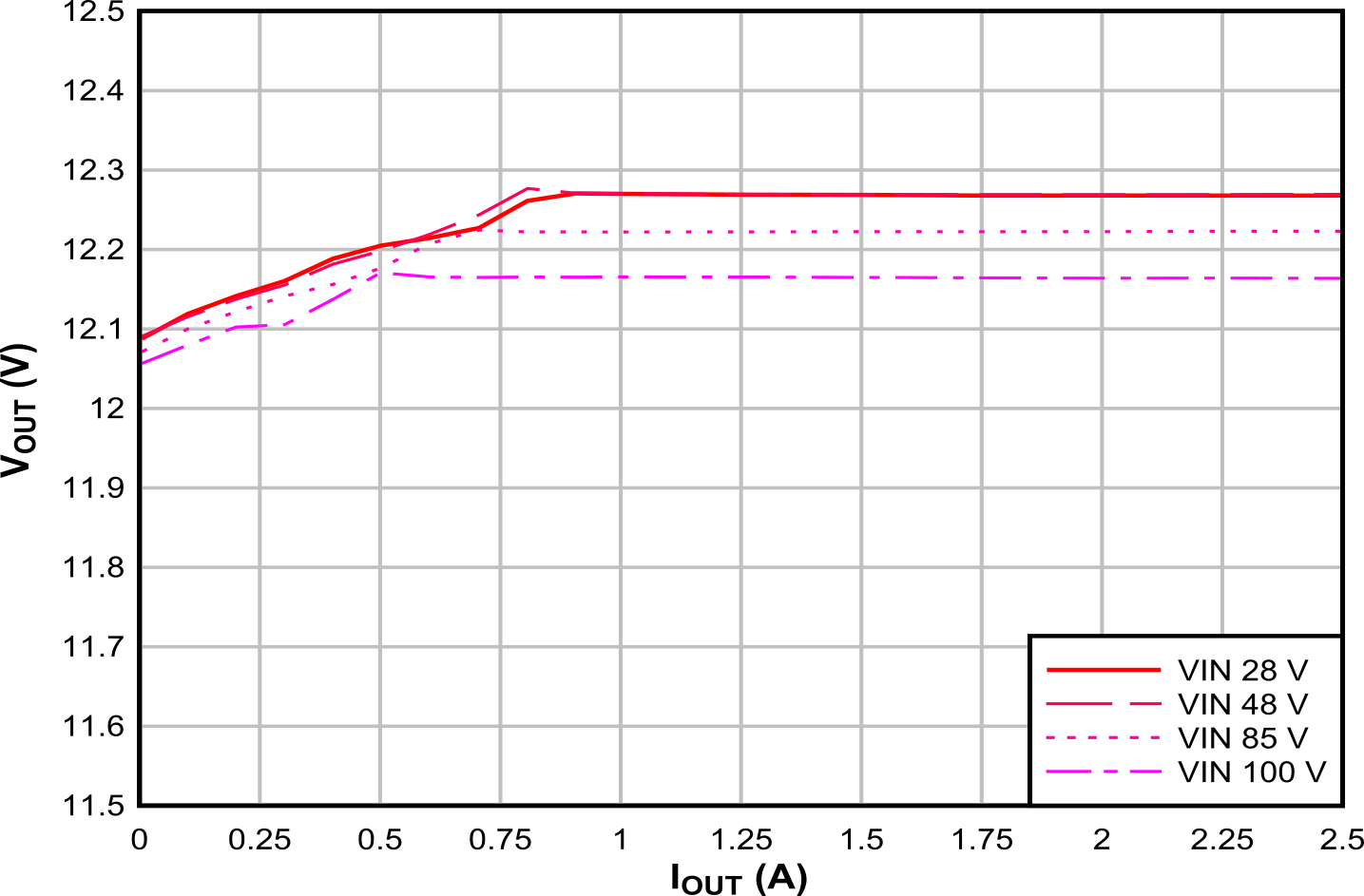

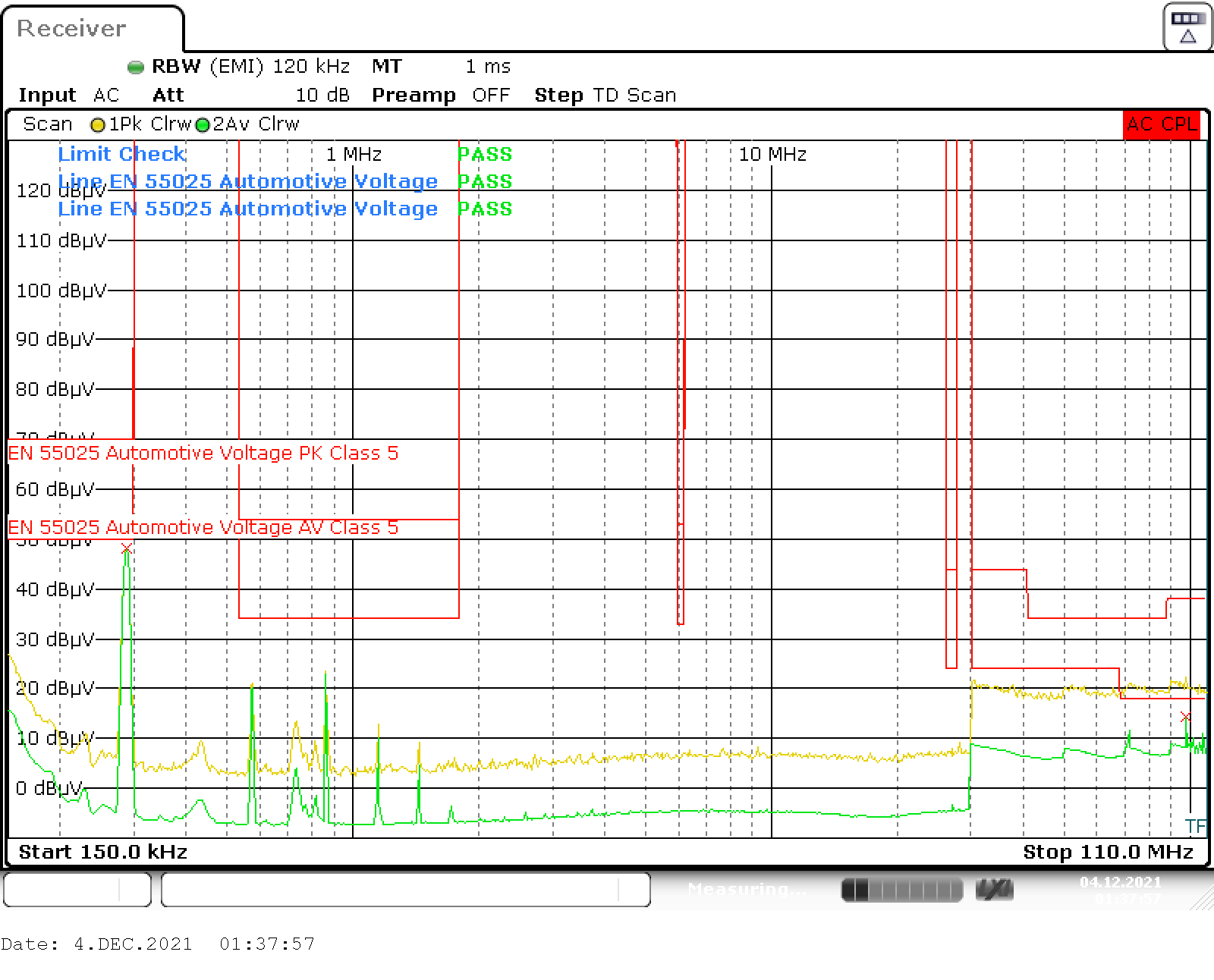

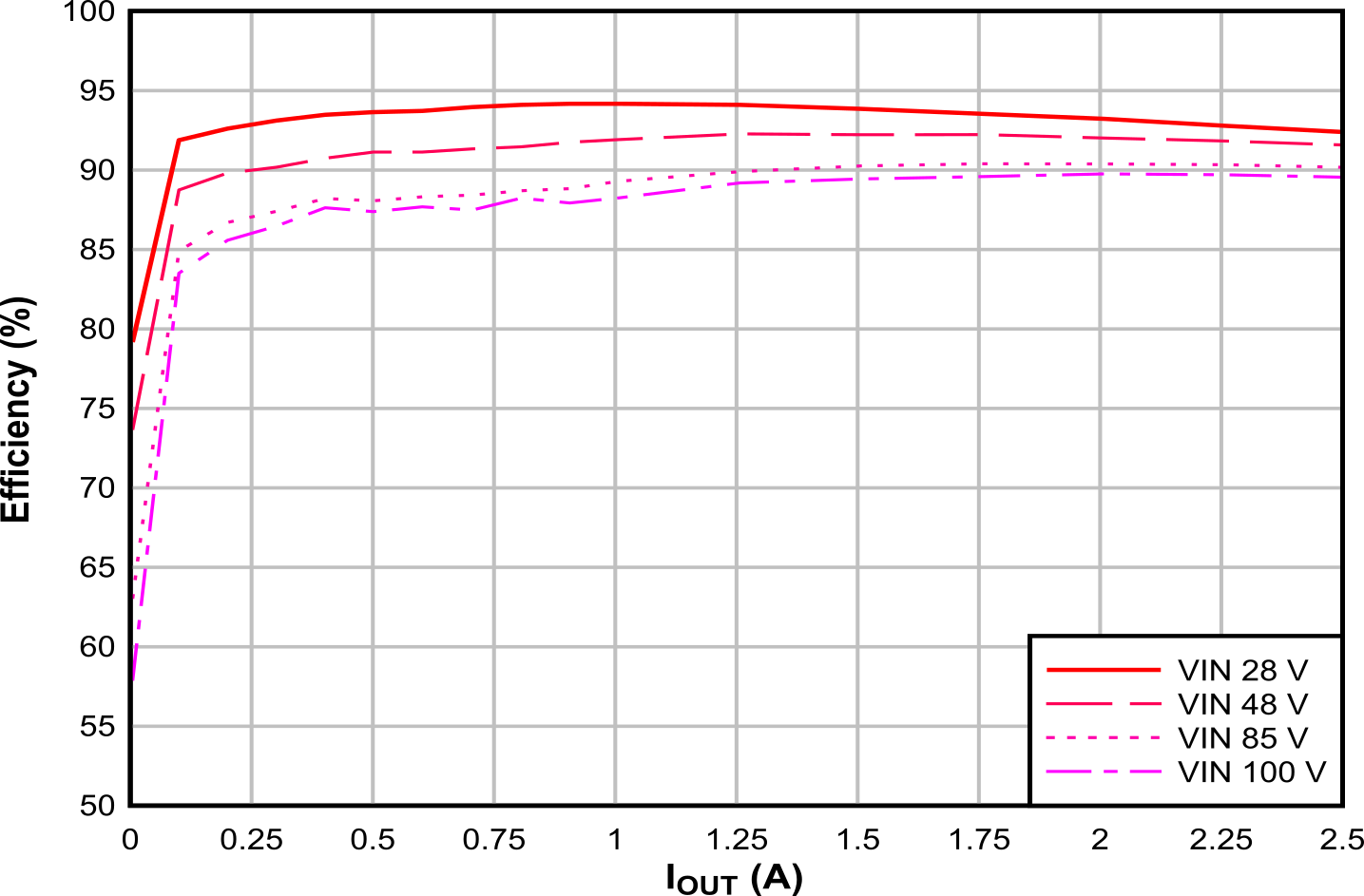

9.2.3 Application Curves

| VOUT = 12 V | RON = 102 kΩ | LO = 22 μH |

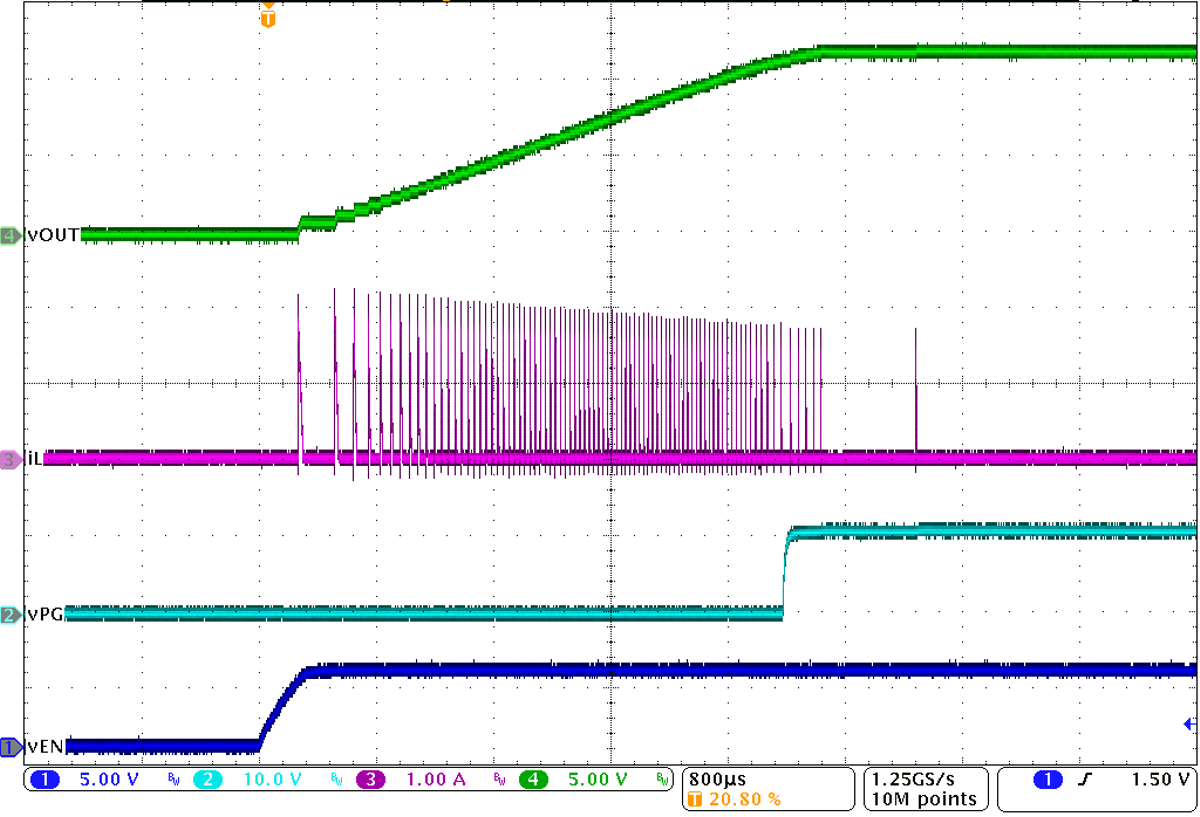

| VOUT = 12 V | RON = 102 kΩ | LO = 22 μH |

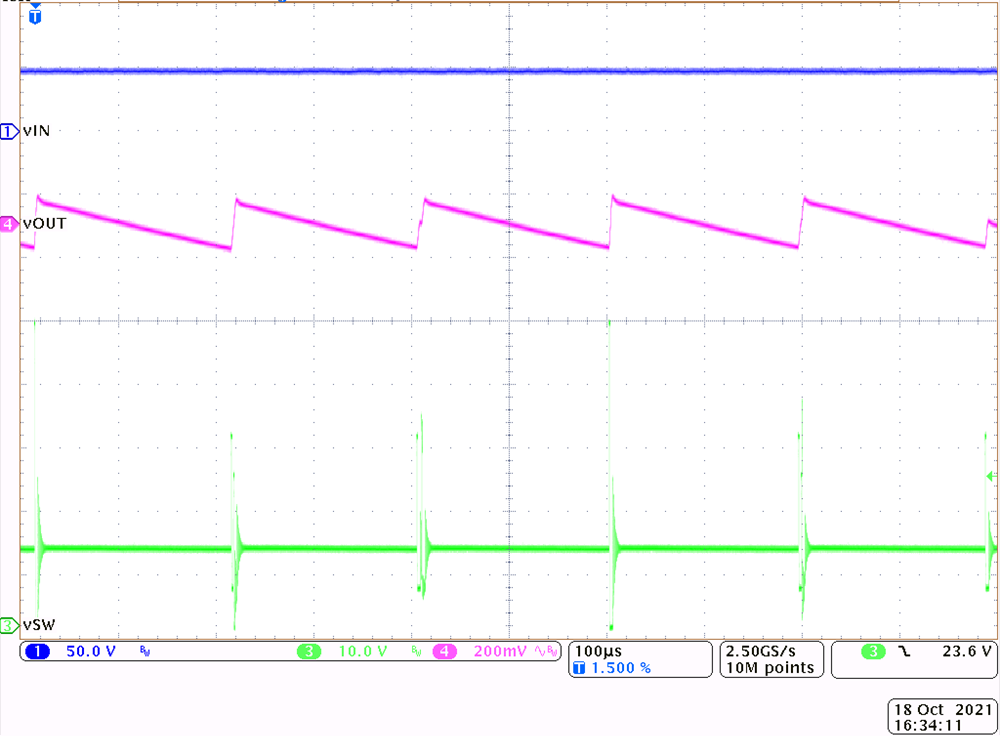

| VIN = 48 V | VOUT = 12 V | IOUT = 0 A |

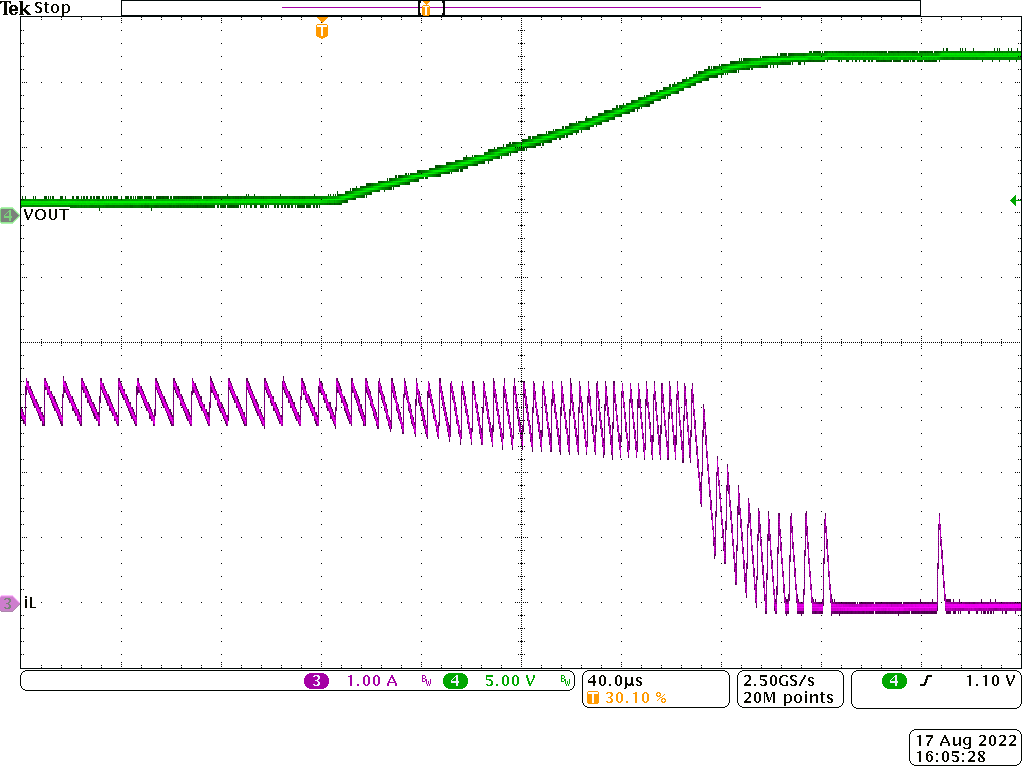

| VIN = 48 V | VOUT 12 V | Load = 0 A to Short |

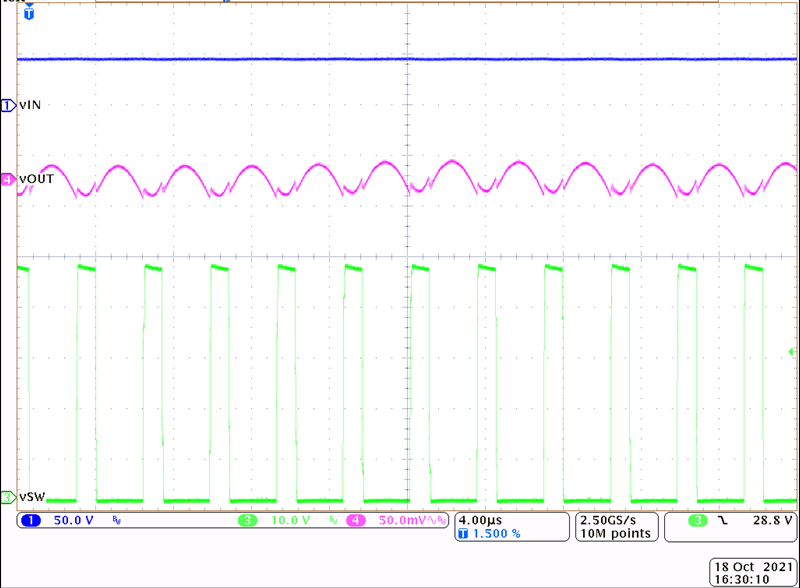

| VIN = 48 V | VOUT = 12 V | IOUT = 2.5 A |

| VIN = 48 V | VOUT = 12 V | IOUT = 3.5 A (LM5013-Q1) |

| VOUT = 12 V | RON = 102 kΩ | LO = 22 μH |

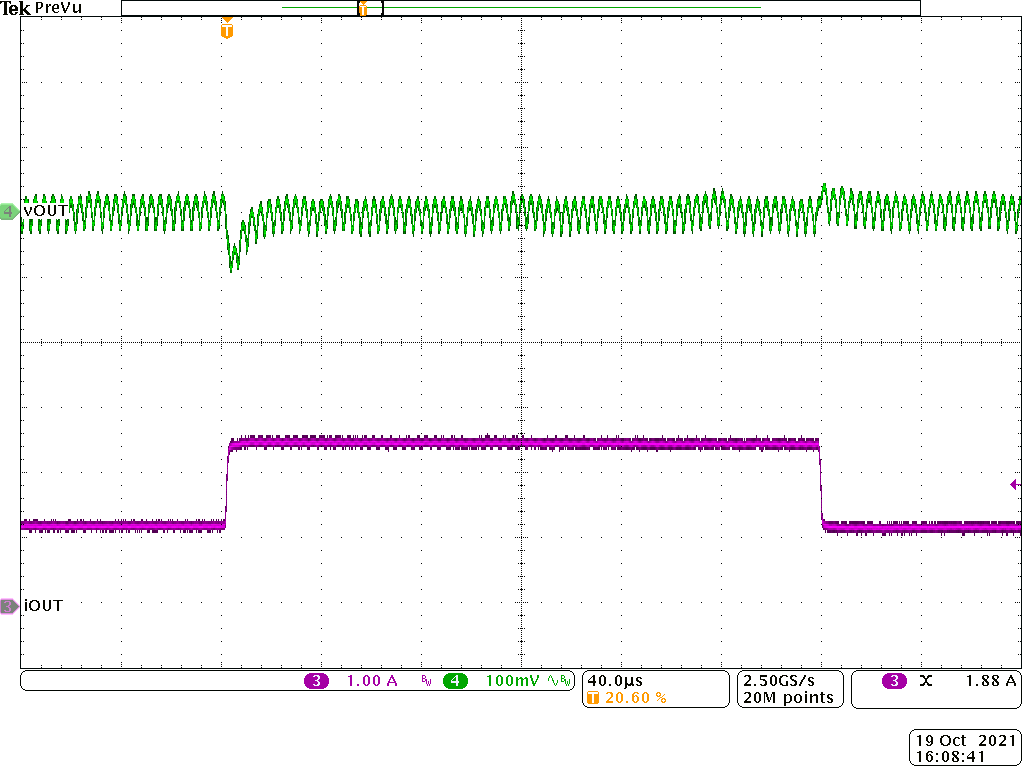

| VIN = 48 V | VOUT = 12 V | IOUT

= 1.0-A to 2.5-A (Rise/fall time = 1A/uS) |

| VIN = 48 V | VOUT 12 V | Load = 0 A to Short |

| VIN = 48 V | VOUT 12 V | IOUT = 200 mA |

| Filter used for EMC scan. Additionally, the regulator was housed in an enclosed shield. |