SNOS760D May 1999 – February 2024 LM7171

PRODUCTION DATA

- 1

- 1Features

- 2Applications

- 3Description

- 4Pin Configuration and Functions

- 5Specifications

- 6Application and Implementation

- 7Device and Documentation Support

- 8Revision History

- 9Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- D|8

- P|8

Thermal pad, mechanical data (Package|Pins)

Orderable Information

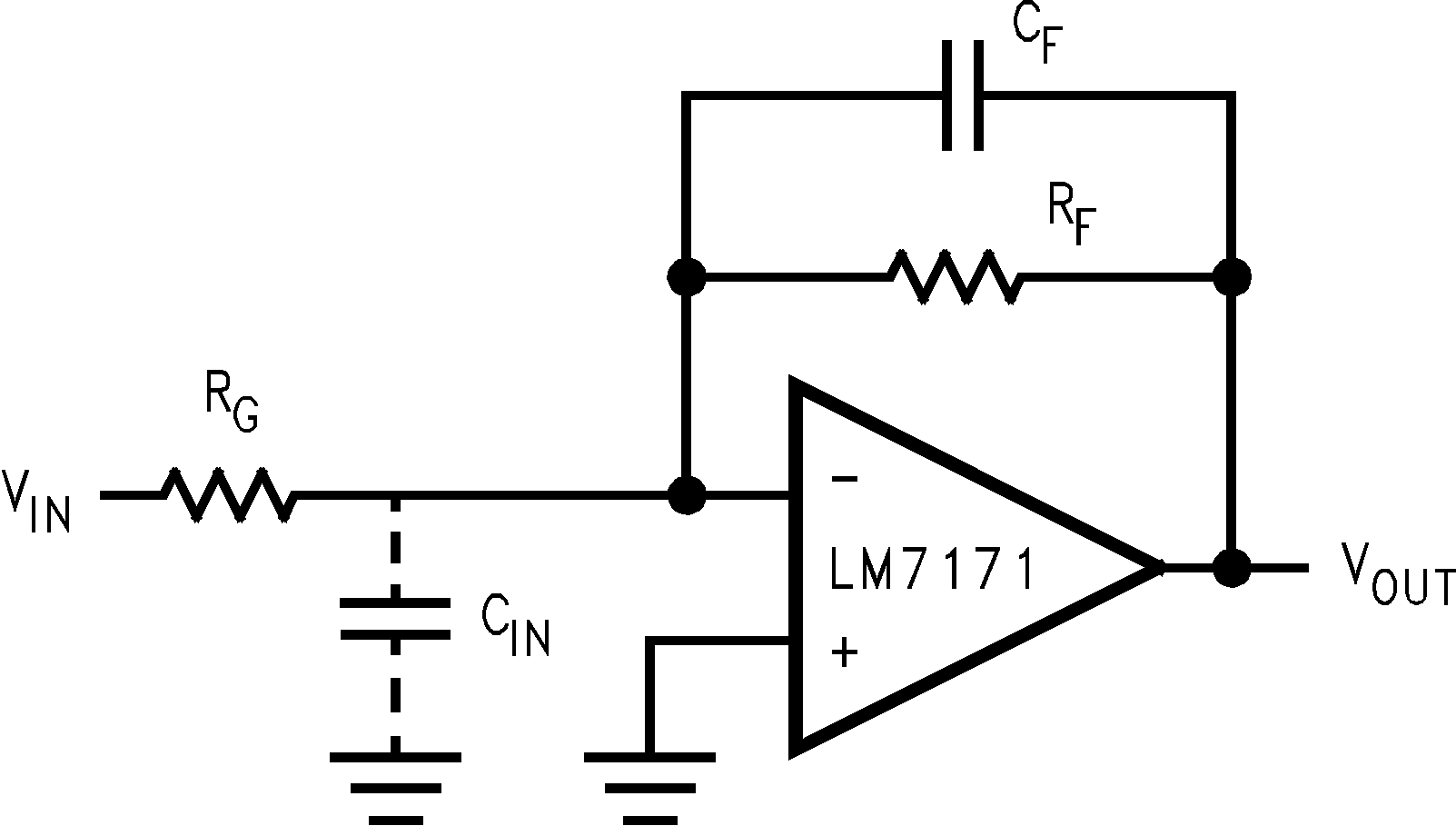

6.1.3 Compensation for Input Capacitance

The combination of an amplifier input capacitance with the gain setting resistors adds a pole that can cause peaking or oscillation. To solve this problem, a feedback capacitor with a value of

Equation 1. CF > (RG × CIN) /

RF

can be used to cancel that pole. For LM7171, a feedback capacitor of 2pF is recommended. Figure 6-1 illustrates the compensation circuit.

Figure 6-1 Compensating for Input Capacitance

Figure 6-1 Compensating for Input Capacitance