SNOSA56I February 2003 – September 2015 LMV7271 , LMV7272 , LMV7275

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 1.8-V Electrical Characteristics

- 6.6 1.8-V AC Electrical Characteristics

- 6.7 2.7-V Electrical Characteristics

- 6.8 2.7-V AC Electrical Characteristics

- 6.9 5-V Electrical Characteristics

- 6.10 5-V AC Electrical Characteristics

- 6.11 Typical Characteristics

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

Package Options

Mechanical Data (Package|Pins)

Thermal pad, mechanical data (Package|Pins)

Orderable Information

7 Detailed Description

7.1 Overview

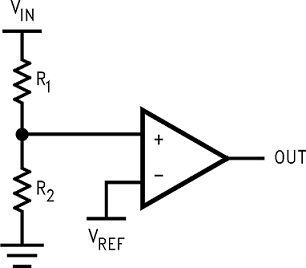

A comparator is often used to convert an analog signal to a digital signal. As shown in Figure 24, the comparator compares an input voltage (VIN) to a reference voltage (VREF). If VIN is less than VREF, the output (VO) is low. However, if VIN is greater than VREF, the output voltage (VO) is high.

Figure 24. LMV7271 Basic Comparator

Figure 24. LMV7271 Basic Comparator

7.2 Functional Block Diagram

7.3 Feature Description

7.3.1 Rail-to-Rail Input Stage

The LMV727X has an input common mode voltage range (VCM) of −0.1V below the V− to 0.1 V above V+. This is achieved by using paralleled PNP and NPN differential input pairs. When the VCM is near V+, the NPN pair is on and the PNP pair is off. When the VCM is near V−, the NPN pair is off and the PNP pair is on. The crossover point between the NPN and PNP input stages is around 950mV from V+. Because each input stage has its own offset voltage (VOS), the VOS of the comparator becomes a function of the VCM. See curves for VOS vs. VCM in the Typical Characteristics section. In application design, it is recommended to keep the VCM away from the crossover point to avoid problems. The wide input voltage range makes LMV727X ideal in power supply monitoring circuits, where the comparators are used to sense signals close to ground and power supplies.

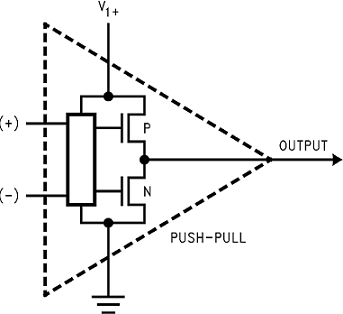

7.3.2 Output Stage, LMV7271 and LMV7272

Figure 25. LMV7271 and LMV7272 Push-Pull Output Stage

Figure 25. LMV7271 and LMV7272 Push-Pull Output Stage

The LMV7271 and LMV7272 have a push-pull output stage. This output stage keeps the total system power consumption to the absolute minimum by eliminating the need for a pullup resistor. The only current consumed is the low supply current and the current going directly into the load.

When the output switches, both PMOS and NMOS at the output stage are on at the same time for a very short time. This allows current to flow directly between V+ and V− through output transistors. The result is a short spike of current (called shoot-through current) drawn from the supply and glitches in the supply voltages. The glitches can spread to other parts of the board as noise. To prevent the glitches in supply lines, power supply bypass capacitors must be installed. See Circuit Techniques for Avoiding Oscillations in Comparator Applications for supply bypassing for details.

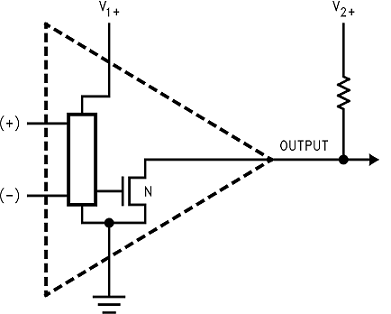

7.3.3 Output Stage, LMV7275

Figure 26. LMV7275 Open-Drain Output

Figure 26. LMV7275 Open-Drain Output

The LMV7275 has an open-drain output that requires a pullup resistor to a positive supply voltage for the output to operate properly. The internal circuitry is identical to the LMV7271 except that the upper P-channel output device is absent. When the internal output transistor is off, the output voltage will be pulled up to the external positive voltage by the external pullup resistor. This allows the output to be OR'ed with other open-drain outputs on the same bus. The output pullup resistor may be connected to any voltage level between V- and V+ for level shifting applications.

7.4 Device Functional Modes

7.4.1 Capacitive and Resistive Loads

The propagation delay is not affected by capacitive loads at the output of the LMV7271 or LMV7272. However, resistive loads slightly effect the propagation delay on the falling edge depending on the load resistance value.

The propagation delay on the rising edge of the LMV7275 depends on the load resistance and capacitance values.

7.4.2 Noise

Most comparators have rather low gain. This allows the output to alternate between high and low when the input signal changes slowly. The result is the output may oscillate between high and low when the differential input is near zero and triggers on noise. The high gain of this comparator eliminates this problem. Less than 1 μV of change on the input will drive the output from one rail to the other rail. If the input signal is noisy, the output cannot ignore the noise unless some hysteresis is provided by positive feedback. (See Hysteresis.)

7.4.3 Hysteresis

It is a standard procedure to use hysteresis (positive feedback) around a comparator to prevent oscillation due to the comparator triggering its own noise on slowly ramping signals. The following sections will describe various ways to apply hysteresis.

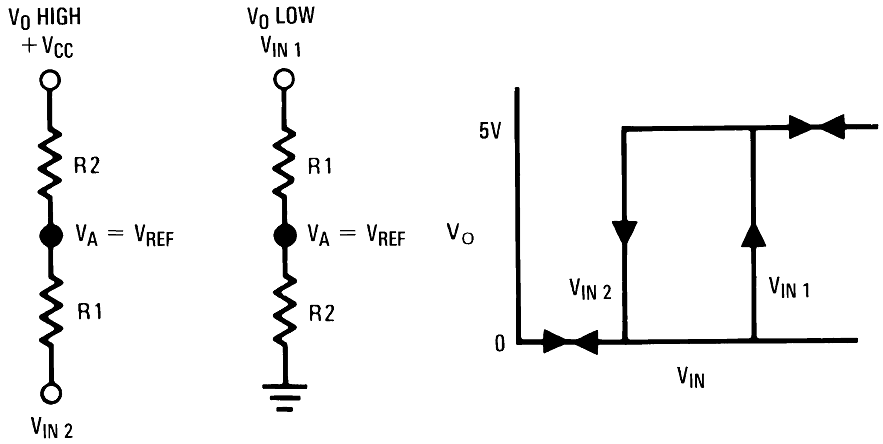

7.4.3.1 Noninverting Comparator With Hysteresis

Figure 27. Noninverting Comparator With Hysteresis

Figure 27. Noninverting Comparator With Hysteresis

A noninverting comparator with hysteresis requires a two resistor network, and a voltage reference (VREF) at the inverting input. When VIN is low, the output is also low. For the output to switch from low to high, VIN must rise up to VIN1 where VIN1 is calculated by:

As soon as VO switches to VCC, VA steps to a value greater than VREF which is given by:

To make the comparator switch back to its low state, VIN must equal VREF before VA will again equal VREF. VIN2 can be calculated by:

The hysteresis of this circuit is the difference between VIN1 and VIN2.

Figure 28. Noninverting Comparator Thresholds

Figure 28. Noninverting Comparator Thresholds

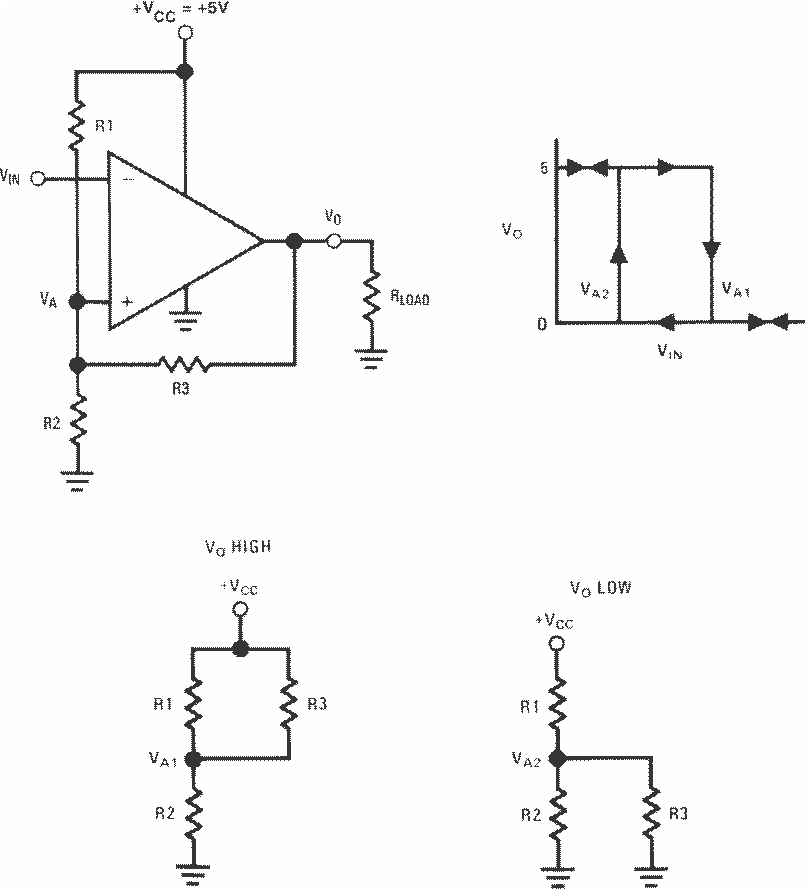

7.4.3.2 Inverting Comparator With Hysteresis

Figure 29. Inverting Comparator With Hysteresis

Figure 29. Inverting Comparator With Hysteresis

The inverting comparator with hysteresis requires a three resistor network that is referenced to the supply voltage VCC of the comparator (Figure 29). When VIN at the inverting input is less than VA, the voltage at the noninverting node of the comparator (VIN < VA), the output voltage is high (for simplicity assume VO switches as high as VCC). The three network resistors can be represented as R1||R3 in series with R2. The lower input trip voltage VA1 is defined as

When VIN is greater than VA (VIN > VA), the output voltage is low and very close to ground. In this case the three network resistors can be presented as R2//R3 in series with R1. The upper trip voltage VA2 is defined as

The total hysteresis provided by the network is defined as

A good typical value of ΔVA would be in the range of 5 to 50 mV. This is easily obtained by choosing R3 as 1000 to 100 times (R1||R2) for 5-V operation, or as 300 to 30 times (R1||R2) for 1.8-V operation.

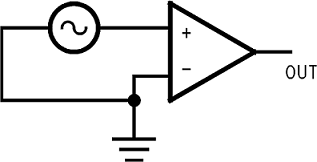

7.4.4 Zero Crossing Detector

Figure 30. Simple Zero Crossing Detector

Figure 30. Simple Zero Crossing Detector

In a zero crossing detector circuit, the inverting input is connected to ground and the noninverting input is connected to a 100 mVPP AC signal. As the signal at the noninverting input crosses 0 V, the output of the comparator changes state.

7.4.4.1 Zero Crossing Detector With Hysteresis

Figure 31. Zero Crossing Detector With Hysteresis

Figure 31. Zero Crossing Detector With Hysteresis

To improve switching times and centering the input threshold to ground a small amount of positive feedback is added to the circuit. Voltage divider R4 and R5 establishes a reference voltage, V1, at the positive input. By making the series resistance, R1 plus R2 equal to R5, the switching condition, V1 = V2, will be satisfied when VIN = 0.

The positive feedback resistor, R6, is made very large with respect to R5 || R6 = 2000 R5). The resultant hysteresis established by this network is very small (ΔV1 < 10 mV) but it is sufficient to insure rapid output voltage transitions.

Diode D1 is used to insure that the inverting input terminal of the comparator never goes below approximately −100 mV. As the input terminal goes negative, D1 will forward bias, clamping the node between R1 and R2 to approximately −700 mV. This sets up a voltage divider with R2 and R3 preventing V2 from going below ground. The maximum negative input overdrive is limited by the current handling ability of D1.

7.4.5 Threshold Detector

Figure 32. Threshold Detector

Figure 32. Threshold Detector

Instead of tying the inverting input to 0 V, the inverting input can be tied to a reference voltage. As the input on the noninverting input passes the VREF threshold, the output of the comparator changes state. It is important to use a stable reference voltage to ensure a consistent switching point.

7.4.6 Universal Logic Level Shifter (LMV7275 only)

Figure 33. Logic Level Shifter

Figure 33. Logic Level Shifter

The output of LMV7275 is an unconnected drain of an NMOS device, which can be pulled up, through a resistor, to any desired output level within the permitted power supply range. Hence, the following simple circuit works as a universal logic level shifter, pulling up the signal to the desired level.

For example, VA could be the 5-V analog supply voltage, where VB could be the 3.3-V supply of the processor. The output will now be compatable with the 3.3-V logic.

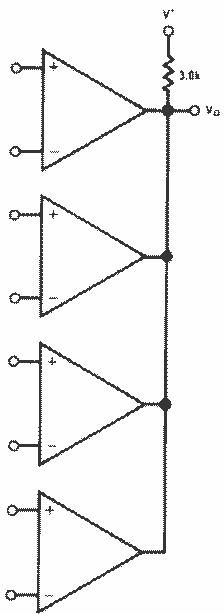

7.4.7 OR'ING the Output (LMV7275 only)

Figure 34. OR’ing the Outputs

Figure 34. OR’ing the Outputs

Because the LMV7275 output is an unconnected NMOS drain, many open-drain outputs can be tied together, pulled up to V+ by a common resistor to provide an output OR'ing function. If any of the comparator outputs goes low, the output VO goes low.