SLLS132D September 1991 – October 2023 SN75ALS173

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

Package Options

Refer to the PDF data sheet for device specific package drawings

Mechanical Data (Package|Pins)

- NS|16

- N|16

Thermal pad, mechanical data (Package|Pins)

Orderable Information

3 Description

The SN75ALS173 is a monolithic quadruple differential line receiver with 3-state outputs. It is designed to meet the requirements of ANSI Standards EIA/TIA-422-B, EIA/TIA-423-B, RS-485, and several ITU recommendations. Advanced low-power Schottky technology provides high speed without the usual power penalty. The four receivers have an ORed pair of enables in common. Either G high or G low enables all of the receivers. The device features high input impedance, input hysteresis for increased noise immunity, and input sensitivity of ±200 mV over a common-mode input voltage range of –12 V to 12 V.

The SN75ALS173 is characterized for operation from 0°C to 70°C.

| PART NUMBER | PACKAGE(1) | PACKAGE SIZE(2) |

|---|---|---|

| SN75ALS173 | N (PDIP, 16) | 19.3 mm × 9.4 mm |

| NS (SOP, 16) | 10.2 mm × 7.8 mm |

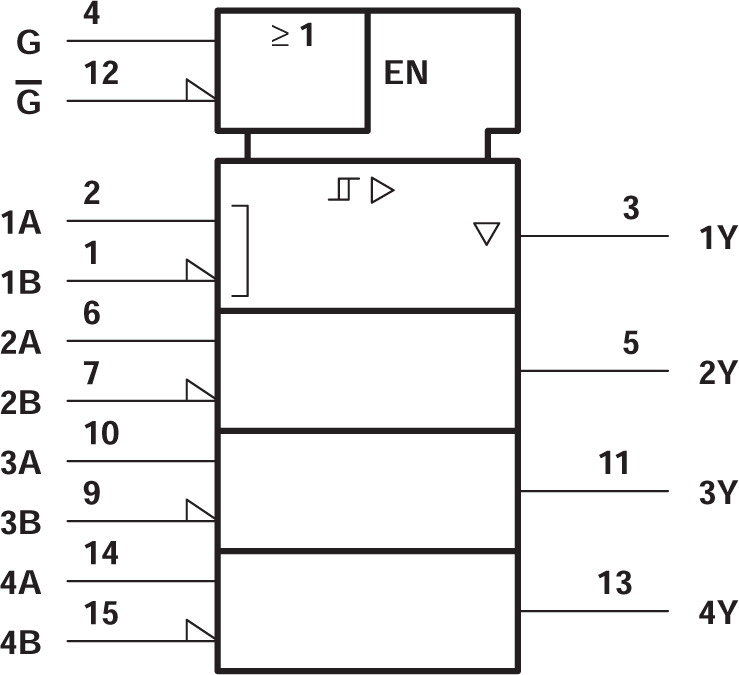

Logic Symbol(1)

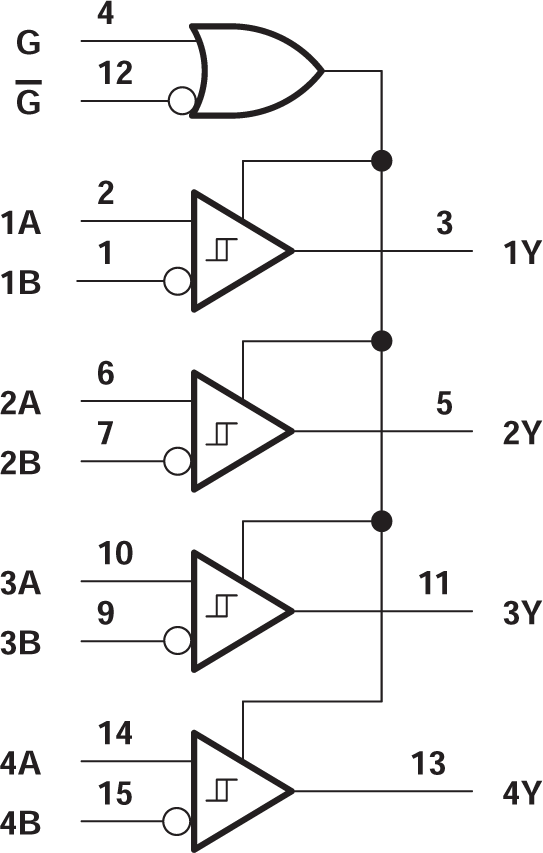

Logic Symbol(1) Logic Diagram (Positive Logic)

Logic Diagram (Positive Logic)