SLAS663C August 2009 – June 2016 TLV320AIC3106-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Description (Continued)

- 6 Device Comparison Table

- 7 Pin Configuration and Functions

-

8 Specifications

- 8.1 Absolute Maximum Ratings

- 8.2 ESD Ratings

- 8.3 Recommended Operating Conditions

- 8.4 Thermal Information

- 8.5 Electrical Characteristics

- 8.6 Switching Characteristics I2S/LJF/RJF In Master Mode

- 8.7 Switching Characteristics I2S/LJF/RJF In Slave Mode

- 8.8 Switching Characteristics DSP In Master Mode

- 8.9 Switching Characteristics DSP In Slave Mode

- 8.10 Typical Characteristics

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3

Feature Description

- 9.3.1 Audio Data Converters

- 9.3.2 Stereo Audio ADC

- 9.3.3 Automatic Gain Control (AGC)

- 9.3.4 Stereo Audio DAC

- 9.3.5 Digital Audio Processing For Playback

- 9.3.6 Digital Interpolation Filter

- 9.3.7 Delta-Sigma Audio Dac

- 9.3.8 Audio Dac Digital Volume Control

- 9.3.9 Analog Output Common-Mode Adjustment

- 9.3.10 Audio DAC Power Control

- 9.3.11 Audio Analog Inputs

- 9.3.12 Analog Input Bypass Path Functionality

- 9.3.13 ADC PGA Signal Bypass Path Functionality

- 9.3.14 Input Impedance and VCM Control

- 9.3.15 MICBIAS Generation

- 9.3.16 Analog Fully Differential Line Output Drivers

- 9.3.17 Analog High Power Output Drivers

- 9.3.18 Short Circuit Output Protection

- 9.3.19 Jack and Headset Detection

- 9.3.20 General-Purpose I/O

- 9.4 Device Functional Modes

- 9.5

Programming

- 9.5.1 Hardware Reset

- 9.5.2 Digital Control Serial Interface

- 9.5.3 I2C Control Mode

- 9.5.4 I2C Bus Debug In A Glitched System

- 9.5.5 Digital Audio Data Serial Interface

- 9.5.6 Right-Justified Mode

- 9.5.7 Left-Justified Mode

- 9.5.8 I2S Mode

- 9.5.9 DSP Mode

- 9.5.10 TDM Data Transfer

- 9.5.11 Audio Clock Generation

- 9.6 Register Maps

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, And Orderable Information

Package Options

Mechanical Data (Package|Pins)

- RGZ|48

Thermal pad, mechanical data (Package|Pins)

- RGZ|48

Orderable Information

11 Power Supply Recommendations

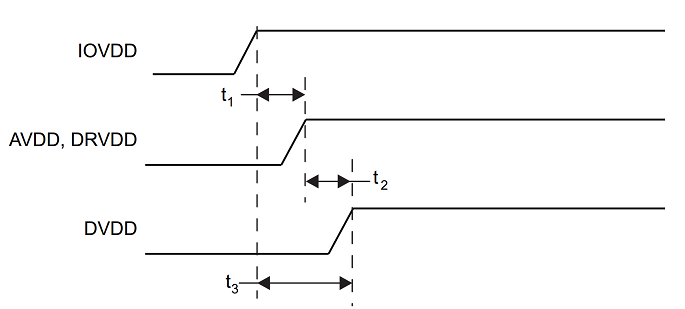

The TLV320AIC3106-Q1 has been designed to be extremely tolerant of power supply sequencing. However, in some rare instances, unexpected conditions can be attributed to power supply sequencing. The following sequence provides the most robust operation.

IOVDD must be powered up first. The analog supplies, which include AVDD and DRVDD, must be powered up second. The digital supply DVDD must be powered up last. Keep RESET low until all supplies are stable. The analog supplies must be greater than or equal to DVDD at all times.

Figure 43. TLV320AIC3101 Power Supply Sequencing

Figure 43. TLV320AIC3101 Power Supply Sequencing

Table 190. TLV320AIC3101 Power Supply Sequencing

| PARAMETER | MIN | MAX | UNIT | |

|---|---|---|---|---|

| t1 | IOVDD to AVDD, DRVDD | 0 | ms | |

| t2 | AVDD to DVDD | 0 | 5 | ms |

| t3 | IOVDD, to DVDD | 0 | ms | |