JAJSF36L November 2008 – February 2019 ADC14155QML-SP

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 ADC14155 Converter Electrical Characteristics DC Parameters

- 6.6 ADC14155 Converter Electrical Characteristics (Continued) DYNAMIC Parameters

- 6.7 ADC14155 Converter Electrical Characteristics (Continued) Logic and Power Supply Electrical Characteristics

- 6.8 ADC14155 Converter Electrical Characteristics (Continued) Timing and AC Characteristics

- 6.9 Timing Diagram

- 6.10 Transfer Characteristic

- 6.11 Typical Performance Characteristics, DNL, INL

- 6.12 Typical Performance Characteristics, Dynamic Performance

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- NBA|48

サーマルパッド・メカニカル・データ

発注情報

11.1.1 デバイスの項目表記

アパーチャ遅延は、クロックの立ち下がりエッジから、変換を行うために入力信号が取り込まれるか保持されるまでの時間です。

アパーチャ・ジッタ(アパーチャ不確定性)は、サンプル間のアパーチャ遅延のばらつきです。アパーチャ・ジッタは、出力にノイズとして現れます。

クロック・デューティ・サイクルは、繰り返しデジタル波形の1周期に対するHIGH期間の割合です。本データシートに記載する仕様は、ADCのクロック入力信号に適用されます。

同相電圧(VCM)は、ADCの両方の入力端子に印加される共通のDC電圧です。

変換レイテンシは、変換開始からその変換データが出力ドライバ段で得られるまでの期間をクロック・サイクル数で表したものです。各サンプリングに対するデータは、そのサンプリングが行われた後、パイプライン遅延および出力遅延の経過後に出力ピン上で有効になります。新しいデータはクロック・サイクルごとに有効ですが、その出力データは変換からパイプライン遅延の分だけ遅れます。

微分非直線性(DNL)は、理想的なステップ・サイズである1LSBからの最大偏差として表します。

有効ビット数(ENOB)は、信号/(ノイズ+歪み)比(SINAD)を別の方法で規定したものです。ENOBは(SINAD-1.76)/6.02として定義され、この値のビット数を持つ完全なADCと等価なコンバータであることを意味します。

フルパワー帯域幅は、再構築された出力基本波が、フルスケール入力について、低周波数の値より3dB低下する周波数の測定値です。

ゲイン誤差は、伝達関数の理想的な勾配からの偏差です。次の式で計算できます。

正側ゲイン誤差と負側ゲイン誤差として、次のように表すこともできます。

積分非直線性(INL)は、負のフルスケール(最初のコード遷移の1/2LSB下)から正のフルスケール(最後のコード遷移の1/2LSB上)まで引いた直線からの個々のコードの偏差として表します。この直線からの各コードの偏差は、そのコード値の中央から測定します。

相互変調歪み(IMD)は、ADCの入力に2つの正弦波周波数を同時に入力した結果、新たなスペクトル成分が生じる現象です。元の周波数の総電力に対する相互変調成分の電力の比として定義されます。IMDは通常dBFSで表します。

最下位ビット(LSB)は、すべてのビットのうち値または重みが最も小さいビットです。この値はVFS/2nであり、「VFS」はフルスケール入力電圧、「n」はADCの分解能(ビット)です。

ミッシング・コードは、ADCの出力に現れることのない出力コードです。ADC14155QMLにはミッシング・コードがないことが保証されています。

最上位ビット(MSB)は、値または重みが最も大きいビットです。このビットの値は、フルスケールの半分です。

負側フルスケール誤差は、最初のコード遷移点の実測値と負側フルスケールから1/2LSB高いところにある理想値との差です。

オフセット誤差は、コード8191から8192へと遷移させるために必要な2つの入力電圧の差[(VIN+)-(VIN–)]です。

出力遅延は、クロックの立ち下がりエッジから、出力ピンに更新されたデータが現れるまでの遅延時間です。

パイプライン遅延(レイテンシ) 「変換レイテンシ」を参照してください。

正側フルスケール誤差は、最後のコード遷移点の実測値と正側フルスケールから1.5LSB低いところにある理想値との差です。

電源電圧変動除去比(PSRR)は、電源電圧の変動をADCでどの程度除去できるかを表したものです。PSRRは、最大DC電源限界値でのADCのフルスケールの出力に対する、最小DC電源限界値でのADCのフルスケールの出力の比であり、dBで表します。

信号/ノイズ比(SNR)は、サンプリング周波数の半分を下回る、高調波やDCを除いた、その他すべてのスペクトル成分の実効値に対する入力信号の実効値の比であり、dBで表します。

信号/(ノイズ+歪み)比(S/(N+D)またはSINAD)は、クロック周波数の半分を下回る、高調波を含み、DCを除いた、その他すべてのスペクトル成分の実効値に対する入力信号の実効値の比であり、dBで表します。

スプリアス・フリー・ダイナミック・レンジ(SFDR)は、入力信号の実効値とピーク・スプリアス信号との差であり、dBで表します。ここで言うスプリアス信号とは、出力スペクトルに現れる信号であり、入力に現れるものではありません。

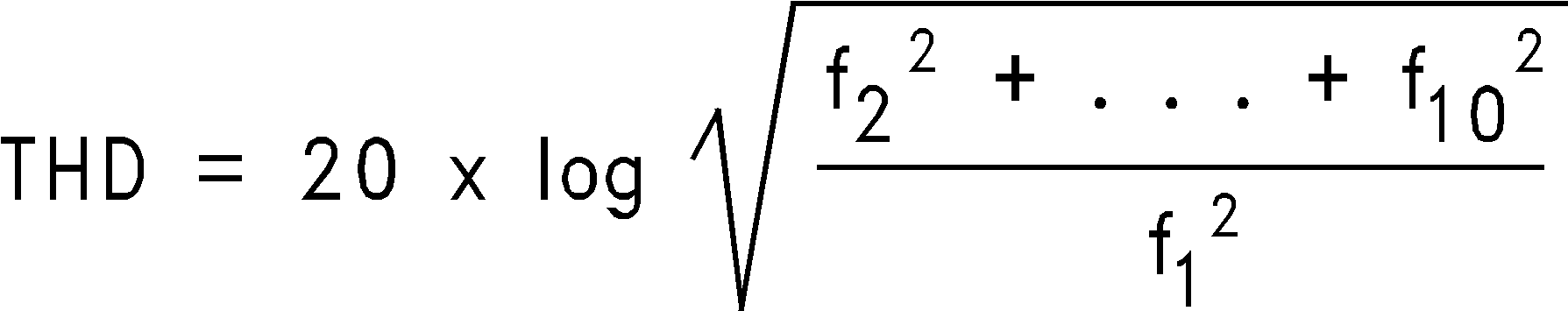

全高調波歪み(THD)は、基本周波数の出力レベルに対する、最初の9つの高調波の合計出力レベルの実効値の比であり、dBで表します。THDは次の式で計算されます。

ここでf1は基本(出力)周波数のRMS電力であり、f2からf10は出力スペクトルに現れる最初の9つの高調波周波数のRMS電力です。

2次高調波歪み(2ND HARM)は、出力に現れる入力周波数のRMS電力と2次高調波レベルの電力との差であり、dBで表します。

3次高調波歪み(3RD HARM)は、出力に現れる入力周波数のRMS電力と3次高調波レベルの電力との差であり、dBで表します。