JAJSKC9E September 2020 – November 2022 DP83TG720S-Q1

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 ピン構成および機能

- 6 仕様

-

7 詳細説明

- 7.1 概要

- 7.2 機能ブロック図

- 7.3 機能説明

- 7.4

デバイスの機能モード

- 7.4.1 パワーダウン

- 7.4.2 リセット

- 7.4.3 スタンバイ

- 7.4.4 通常

- 7.4.5 スリープ

- 7.4.6 状態遷移

- 7.4.7 MDI (Media Dependent Interface)

- 7.4.8 MAC インターフェイス

- 7.4.9 シリアル・マネージメント・インターフェイス

- 7.4.10 ダイレクト・レジスタ・アクセス

- 7.4.11 拡張レジスタ・スペース・アクセス

- 7.4.12 書き込みアドレス動作

- 7.4.13 読み出しアドレス動作

- 7.4.14 書き込み動作 (ポスト・インクリメントなし)

- 7.4.15 読み出し動作 (ポスト・インクリメントなし)

- 7.4.16 書き込み動作 (ポスト・インクリメントあり)

- 7.4.17 読み出し動作 (ポスト・インクリメントあり)

- 7.5 プログラミング

- 7.6 レジスタ・マップ

- 8 アプリケーションと実装

- 9 電源に関する推奨事項

- 10テキサス・インスツルメンツの 100BT1 PHY との互換性

- 11レイアウト

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

11.1.1 信号トレース

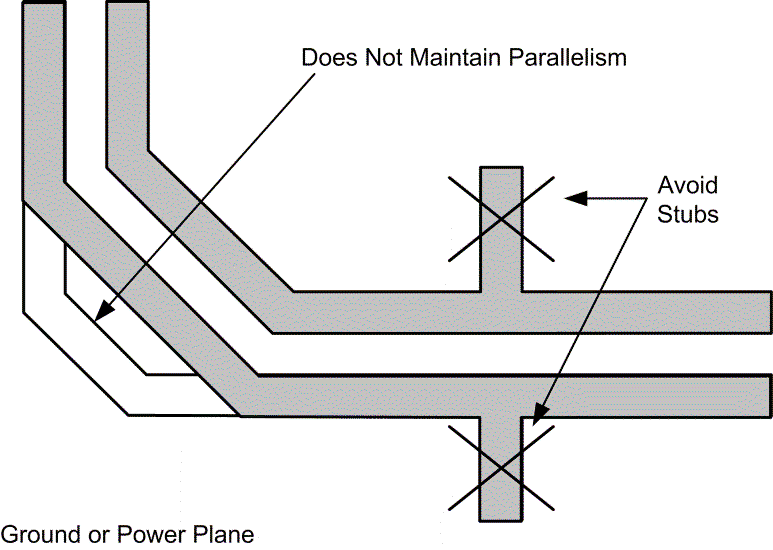

PCB トレースは損失が大きいため、長いトレースが信号品質を低下させる可能性があります。トレースはできるだけ短くする必要があります。特に記述のない限り、すべての信号トレースは 50Ω のシングルエンド・インピーダンスとするものとします。差動トレースは、50Ω シングルエンドおよび 100Ω 差動とするものとします。初めから終わりまでインピーダンスが制御されるように注意します。インピーダンスの不連続性は反射を引き起こし、放射とシグナル・インテグリティの問題につながります。スタブは、すべての信号トレース (特に差動信号ペア) で回避するものとします。

図 11-1 差動信号トレースの配線

図 11-1 差動信号トレースの配線差動ペア内では、トレースを互いに並行させ、長さを一致させる必要があります。長さを一致させることで遅延の差が最小化され、同相ノイズと放射の増加を防止できます。MAC インターフェイス接続でも、長さを一致させることは重要です。すべての送信信号トレースは互いに同じ長さとし、すべての受信信号トレースは互いに同じ長さとします。

理想的には、信号パスのトレースには交差もビアも存在しないようにします。ビアにはインピーダンスの不連続性を生じさせるため、できるだけ少なくします。トレース・ペアは同じ層に配線します。異なる層の信号は、それらの間に少なくとも 1 つの復帰パス・プレーンがない限り、互いに交差させてはなりません。差動ペアは、それらの間の結合距離を常に一定に保つ必要があります。利便性と効率性を高めるため、重要な信号 (例:MDI 差動ペア、基準クロック、MAC IF トレース) を最初に配線することを推奨します。