JAJSKI6C May 2020 – July 2022 DRV8424 , DRV8425

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 ピン構成および機能

- 6 仕様

- 7 詳細説明

- 8 アプリケーションと実装

- 9 電源に関する推奨事項

- 10レイアウト

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

- RGE|24

発注情報

3 概要

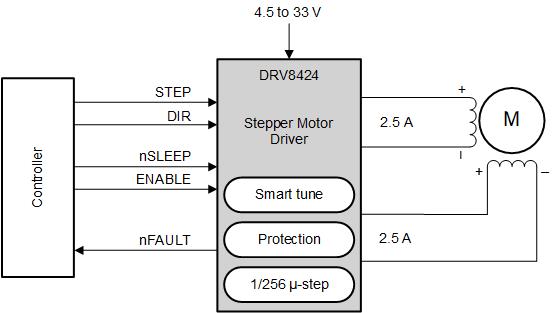

DRV8424/25 は、産業用および民生用アプリケーション向けのステッピング・モータ・ドライバです。このデバイスには、2 つの N チャネル・パワー MOSFET H ブリッジ・ドライバ、マイクロステッピング・インデクサ、および電流検出機能が完全に統合されています。DRV8424 は最大 2.5A のフルスケール出力電流を駆動でき、 DRV8425 は最大 2A のフルスケール出力電流を駆動できます (PCB 設計に依存)。

DRV8424/25 は、2 つの外部電力検出抵抗が不要な内部電流検出アーキテクチャを採用しているため、PCB 面積とシステム・コストを低減できます。本デバイスは、スマート・チューン、スロー、ミックスのディケイ・オプションを選択できる内部 PWM 電流レギュレーション方式を採用しています。スマート・チューンは、最適な電流レギュレーションを自動的に調整し、モータの変動と経年変化を補償し、モータからの可聴ノイズを低減します。

シンプルな STEP/DIR インターフェイスにより、外部コントローラからステッピング・モータの方向とステップ速度を制御できます。デバイスは、フルステップから 1/256 マイクロステッピングまでのモードに構成可能です。専用の nSLEEP ピンを使用して、低消費電力のスリープ・モードを実現します。電源の低電圧、チャージ・ポンプ障害、過電流、短絡、過熱に対する保護機能が備わっています。フォルト条件は、nFAULT ピンで通知されます。

| 部品番号 | パッケージ | 本体サイズ (公称) |

|---|---|---|

| DRV8424PWPR | HTSSOP (28) | 9.7mm × 4.4mm |

| DRV8424RGER | VQFN (24) | 4.0mm × 4.0mm |

| DRV8425PWPR | HTSSOP (28) | 9.7mm × 4.4mm |

| DRV8425RGER | VQFN (24) | 4.0mm × 4.0mm |

概略回路図

概略回路図