JAJSHH8B August 2019 – January 2021 DRV8874-Q1

PRODUCTION DATA

7.3.3.2.2 サイクル単位電流チョッピング

サイクル単位モードの場合、IOUT が ITRIP を超過してから、EN/IN1 ピンまたは PH/IN2 ピンの次の制御入力エッジまで、H ブリッジがブレーキ (ローサイド・スロー・ディケイ状態、両方のローサイド MOSFET がオン) に移行します。このため、外部コントローラによる電流チョッピング方式の追加制御が可能です。図 7-4 に、これを示します。サイクル単位モードでは、ブレーキ (ローサイド・スロー・ディケイ状態) に移行した後、出力をリセットするために新しい制御入力エッジが必要なため、100% デューティ・サイクル電流レギュレーションをサポートしていません。

図 7-4 サイクル単位電流レギュレーション

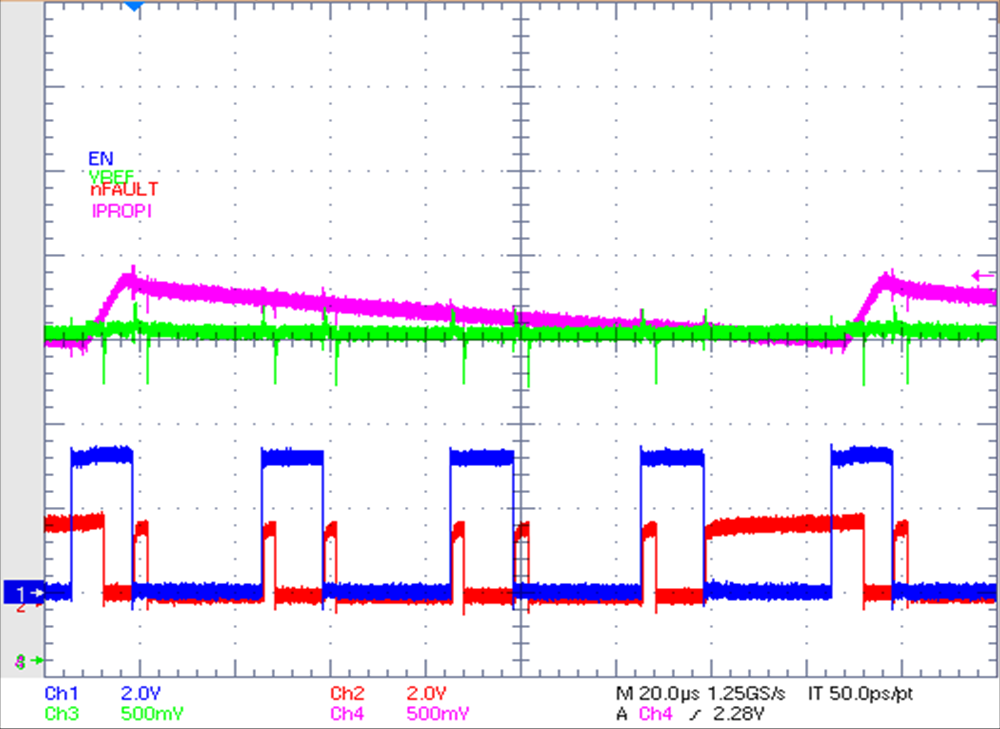

図 7-4 サイクル単位電流レギュレーション本デバイスは、サイクル単位モードにおいて、H ブリッジが内部電流チョッピングに移行すると常に nFAULT ピンを Low にして表示します。これを使って、デバイスの出力が制御入力と異なっているかどうか、または負荷が ITRIP スレッショルドに達したかどうかを判断できます。これを図 7-5 に示します。nFAULT は、デバイスが次の制御入力エッジを受信し、出力をリセットするとすぐに解放されます。

図 7-5 nFAULT が電流チョッピング・インジケータとして機能するサイクル単位電流レギュレーション

図 7-5 nFAULT が電流チョッピング・インジケータとして機能するサイクル単位電流レギュレーションnFAULT ピンが電流チョッピング状態出力として Low になっても、デバイスの機能は影響されません。nFAULT ピンは状態出力としてのみ使用され、デバイスは通常動作を継続します。デバイス・フォルト (「Topic Link Label7.3.4」で概説しています) と電流チョッピング状態出力を区別するために、nFAULT ピンを制御入力と比較できます。電流チョッピング状態出力は、制御入力が順方向または逆方向の駆動状態 (図 7-1) を指示している場合にのみアサートできます。nFAULT ピンの挙動が図 7-5 に示す動作から逸脱した場合、以下の状況のいずれかが発生しています。

- デバイス・フォルトが発生した場合、電流チョッピングではなくフォルト条件を示すために nFAULT ピンが Low にプルされます。デバイス・フォルトの種類によっては、制御入力が Hi-Z またはスロー・ディケイ状態を指示していても、nFAULT は Low に維持される場合があります。

- 制御入力がドライブからスロー・ディケイに移行した際、IOUT > ITRIP の場合、nFAULT ピンは tBLK の間 High になった後再び Low になります。この原因として、制御入力の PWM 周波数またはデューティ・サイクルに応じて生じるオフ時間が短すぎるために IOUT 電流が ITRIP スレッショルドを下回るまで減衰できないことが考えられます。図 7-6 に、この条件の例を示します。IOUT > ITRIP という条件は、オシロスコープでは VIPROPI > VREF として観測できます。

| チャネル1 = EN | チャネル2 = nFAULT | ||

| チャネル3 = VREF | チャネル4 = IPROPI |