JAJSOE2 September 2022 DS320PR822

PRODUCTION DATA

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

8.2.1.3 Application Curves

The DS320PR822 is a linear redriver that can be used to extend channel reach of a PCIe link. Normally, PCIe-compliant Tx and Rx are equipped with signal-conditioning functions and can handle channel losses of up to 36 dB at 16 GHz. With the DS320PR822, the total channel loss between a PCIe root complex and an end point can be extended up to 58 dB at 16 GHz.

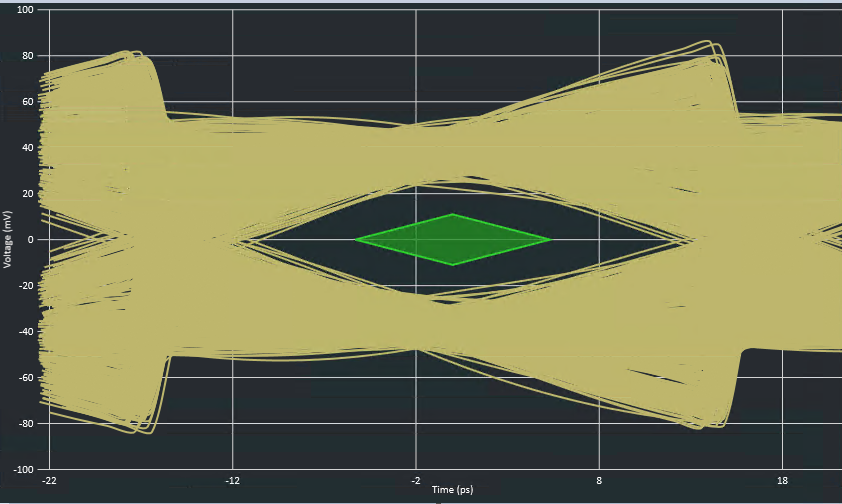

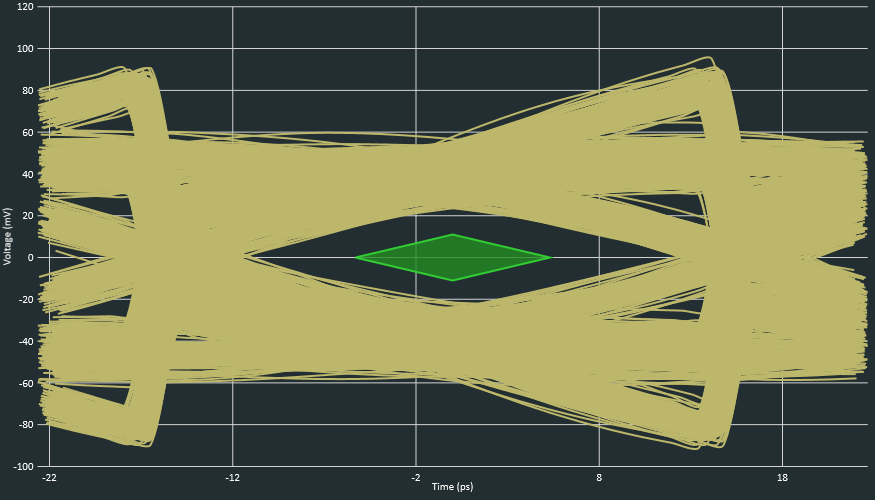

To demonstrate the reach extension capability of the DS320PR822, two comparative setups are constructed. In first setup as shown in Figure 8-3 there is no redriver in the PCIe 5.0 link. Figure 8-4 shows eye diagram at the end of the link using SigTest. In second setup as shown in Figure 8-5, the DS320PR822 is inserted in the middle to extend link reach. Figure 8-6 shows SigTest eye diagram.

Figure 8-4 PCIe 5.0 link Baseline

Setup Without Redriver Eye Diagram Using SigTest

Figure 8-4 PCIe 5.0 link Baseline

Setup Without Redriver Eye Diagram Using SigTest Figure 8-6 PCIe 5.0 Link Setup with

the DS320PR822 Eye Diagram Using SigTest

Figure 8-6 PCIe 5.0 Link Setup with

the DS320PR822 Eye Diagram Using SigTestTable 8-1 provides the PCIe 5.0 links without and with the DS320PR822. The illustration shows that redriver is capable of ≅22 dB reach extension at PCIe 5.0 speed with EQ = 10 (EQ gain of 16 dB) and GAIN1,2 = L1 (flat gain of −4 dB). Note: actual reach extension depends on various signal integrity factors. It is recommended to run signal intergrity simulations with all the components in the link to get any guidance.

| Setup | Pre Channel Loss | Post Channel Loss | Total Loss | Eye at BER 1E-12 | SigTest Pass? |

|---|---|---|---|---|---|

| Baseline – no DUT | — | — | ≅36 dB | 14 ps, 41 mV | Pass |

| With DUT (DS320PR822) | ≅29 dB | ≅29 dB | ≅58 dB | 14 ps, 33 mV | Pass |