JAJS771H October 1999 – October 2018 LM4041-N , LM4041-N-Q1

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 LM4041-N-xx 1.2 Electrical Characteristics (Industrial Temperature Range)

- 6.6 LM4041-N-xx 1.2 Electrical Characteristics (Industrial Temperature Range)

- 6.7 LM4041-N-xx 1.2 Electrical Characteristics (Extended Temperature Range)

- 6.8 LM4041-N-xx ADJ (Adjustable) Electrical Characteristics (Industrial Temperature Range)

- 6.9 LM4041-N-xx ADJ (Adjustable) Electrical Characteristics (Extended Temperature Range)

- 6.10 Typical Characteristics

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

9.1 Application Information

The LM4041-N is a precision micro-power curvature-corrected bandgap shunt voltage reference. For space-critical applications, the LM4041-N is available in the sub-miniature SOT-23 and SC70 surface-mount package. The LM4041-N has been designed for stable operation without the need of an external capacitor connected between the + pin and the – pin. If, however, a bypass capacitor is used, the LM4041-N remains stable. Design effort is further reduced with the choice of either a fixed 1.2 V or an adjustable reverse breakdown voltage. The minimum operating current is 60 μA for the LM4041-N 1.2 V and the LM4041-N ADJ. Both versions have a maximum operating current of 12 mA.

LM4041-Ns using the SOT-23 package have pin 3 connected as the (–) output through the die attach interface of the package. Therefore, pin 3 of the LM4041-N 1.2 must be left floating or connected to pin 2 and pin 3 of the LM4041-N ADJ pinout.

The LM4041-N devices using the SC70 package have pin 2 connected as the (–) output through the die attach interface of the package. Therefore, the LM4041-N pin 2 of the LM4041-N 1.2 must be left floating or connected to pin 1, and the pin 2 of the LM4041-N ADJ is the (–) output.

The typical thermal hysteresis specification is defined as the change in 25°C voltage measured after thermal cycling. The device is thermal cycled to temperature –40°C and then measured at +25°C. Next the device is thermal cycled to temperature 125°C and again measured at 25°C. The resulting VOUT delta shift between the 25°C measurements is thermal hysteresis. Thermal hysteresis is common in precision references and is induced by thermal-mechanical package stress. Changes in environmental storage temperature, operating temperature and board mounting temperature are all factors that can contribute to thermal hysteresis.

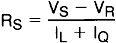

In a conventional shunt regulator application (Figure 17), an external series resistor (RS) is connected between the supply voltage and the LM4041-N. RS determines the current that flows through the load (IL) and the LM4041-N (IQ). Because load current and supply voltage may vary, RS must be small enough to supply at least the minimum acceptable IQ to the LM4041-N even when the supply voltage is at its minimum and the load current is at its maximum value. When the supply voltage is at its maximum and IL is at its minimum, RS must be large enough so that the current flowing through the LM4041-N is less than 12 mA.

RS must be selected based on the supply voltage, (VS), the desired load and operating current, (IL and IQ), and the reverse breakdown voltage of the LM4041-N, VR.

The output voltage of the LM4041-N SDJ can be adjusted to any value in the range of 1.24 V through 10 V. It is a function of the internal reference voltage (VREF) and the ratio of the external feedback resistors as shown in Figure 19 . The output voltage is found using Equation 2.

where

- VO is the output voltage.

The actual value of the internal VREF is a function of VO. The corrected VREF is determined by Equation 3.

where

- VY = 1.240 V

- and ΔVO = (VO − VY)

ΔVREF/ΔVO is found in the electrical characteristics tables in the Specificationsand is typically −1.55 mV/V. You can get a more accurate indication of the output voltage by replacing the value of VREF in Equation 2 with the value found using Equation 3.

NOTE

The actual output voltage can deviate from that predicted using the typical value of

ΔVREF / ΔVO in Equation 3. For C-grade parts, the worst-case ΔVREF / ΔVO is −2.5 mV/V. For D-grade parts, the worst-case ΔVREF / ΔVO is −3.0 mV/V.