JAJSC47I June 2011 – October 2019 LM5113

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要(続き)

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

- DPR|10

発注情報

9.2.2.1 VDD Bypass Capacitor

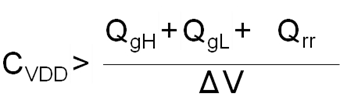

The VDD bypass capacitor provides the gate charge for the low-side and high-side transistors and to absorb the reverse recovery charge of the bootstrap diode. The required bypass capacitance can be calculated with Equation 1.

QgH and QgL are gate charge of the high-side and low-side transistors respectively. Qrr is the reverse recovery charge of the bootstrap diode, which is typically around 4 nC. ΔV is the maximum allowable voltage drop across the bypass capacitor. A 0.1-µF or larger value, good-quality, ceramic capacitor is recommended. The bypass capacitor should be placed as close to the pins of the IC as possible to minimize the parasitic inductance.