JAJSG97A September 2018 – March 2019 LMG3410R050 , LMG3411R050

ADVANCE INFORMATION for pre-production products; subject to change without notice.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12デバイスおよびドキュメントのサポート

- 13メカニカル、パッケージ、および注文情報

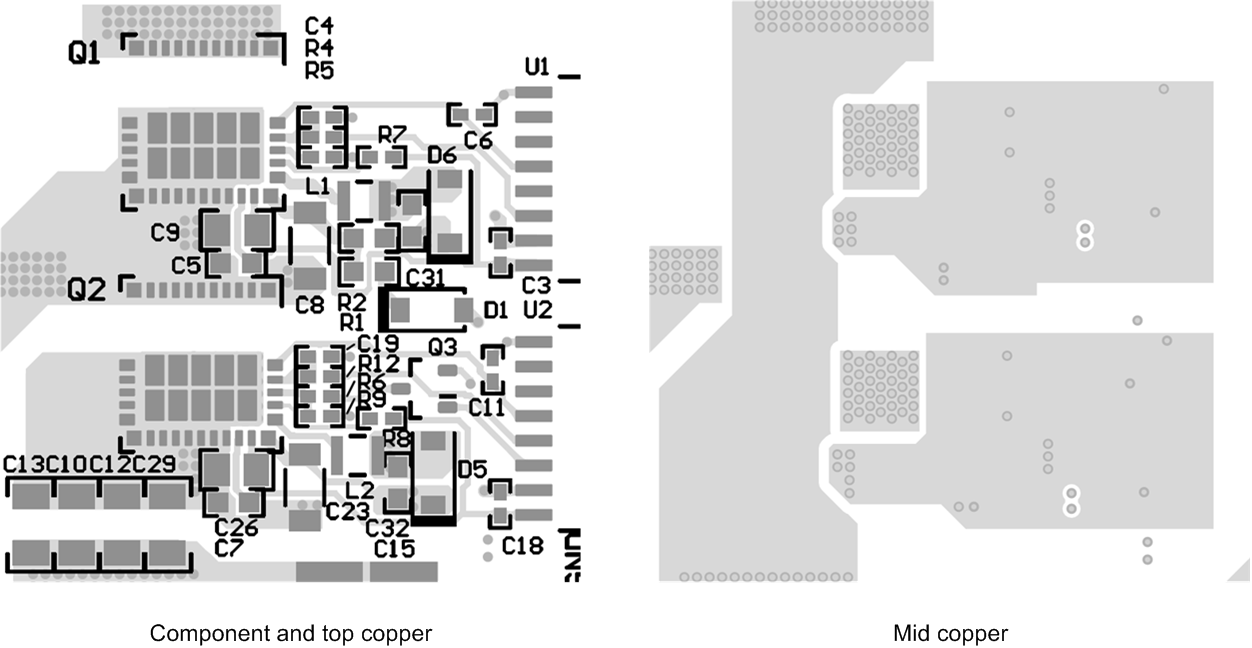

11.2 Layout Example

Correct layout of the LMG341xR050 and its surrounding components is essential for correct operation. The layout shown here reflects the power stage schematic in Figure 4. It may be possible to obtain acceptable performance with alternate layout schemes, however this layout has been shown to produce good results and is intended as a guideline.

Figure 9. Example Half-Bridge Layout

Figure 9. Example Half-Bridge Layout