JAJSER5A February 2018 – April 2018 LMK05028

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 概要(続き)

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagrams

- 9.3

Feature Description

- 9.3.1 Oscillator Input (XO_P/N)

- 9.3.2 TCXO/OCXO Input (TCXO_IN)

- 9.3.3 Reference Inputs (INx_P/N)

- 9.3.4 Clock Input Interfacing and Termination

- 9.3.5 Reference Input Mux Selection

- 9.3.6 Hitless Switching

- 9.3.7 Gapped Clock Support on Reference Inputs

- 9.3.8 Input Clock and PLL Monitoring, Status, and Interrupts

- 9.3.9

PLL Channels

- 9.3.9.1 PLL Frequency Relationships

- 9.3.9.2 Analog PLL (APLL)

- 9.3.9.3 APLL XO Doubler

- 9.3.9.4 APLL Phase Frequency Detector (PFD) and Charge Pump

- 9.3.9.5 APLL Loop Filter

- 9.3.9.6 APLL Voltage Controlled Oscillator (VCO)

- 9.3.9.7 APLL VCO Post-Dividers (P1, P2)

- 9.3.9.8 APLL Fractional N Divider (N) With SDM

- 9.3.9.9 REF-DPLL Reference Divider (R)

- 9.3.9.10 TCXO/OCXO Input Doubler and M Divider

- 9.3.9.11 TCXO Mux

- 9.3.9.12 REF-DPLL and TCXO-DPLL Time-to-Digital Converter (TDC)

- 9.3.9.13 REF-DPLL and TCXO-DPLL Loop Filter

- 9.3.9.14 REF-DPLL and TCXO-DPLL Feedback Dividers

- 9.3.10 Output Clock Distribution

- 9.3.11 Output Channel Muxes

- 9.3.12 Output Dividers

- 9.3.13 Clock Outputs (OUTx_P/N)

- 9.3.14 Glitchless Output Clock Start-Up

- 9.3.15 Clock Output Interfacing and Termination

- 9.3.16 Output Synchronization (SYNC)

- 9.3.17 Zero-Delay Mode (ZDM) Configuration

- 9.3.18 PLL Cascading With Internal VCO Loopback

- 9.4 Device Functional Modes

- 9.5 Programming

- 9.6 Register Maps

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13デバイスおよびドキュメントのサポート

- 14メカニカル、パッケージ、および注文情報

5 概要(続き)

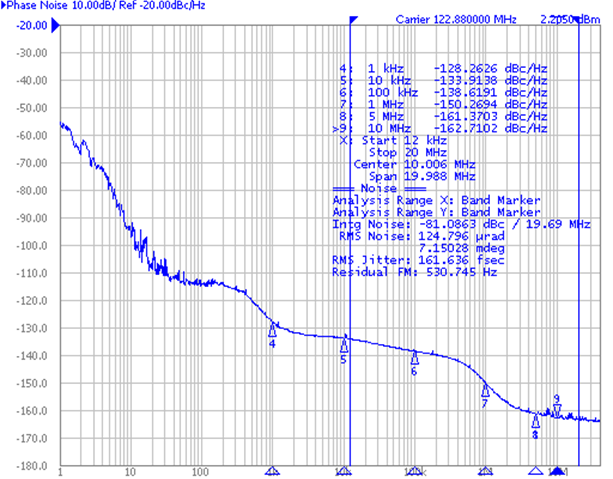

2つのPLLチャネルを備えており、150fs RMSのジッタで最大8つの出力クロックを生成できます。各PLL領域は4つの基準入力のいずれかを選択して、その出力を同期できます。

各PLLチャネルは、ジッタ/ワンダ減衰およびフラクショナル周波数変換用のプログラミング可能なループ帯域幅を備えており、柔軟に周波数を設定できます。各PLLチャネルでサポートする同期オプションには、位相キャンセレーションによるヒットレス・スイッチング、デジタル・ホールドオーバー、1ppt/ステップ未満のDCOモードによる高精度のクロック・ステアリング(IEEE 1588 PTPスレーブ)、ゼロ遅延モードによる決定性入出力位相オフセットがあります。高度な基準入力監視ブロックが、強力なクロック異常検出を実行し、基準喪失(LOR)時の出力クロックの外乱を最小限に抑えることができます。

低周波のTCXO/OCXOによりフリーラン/ホールドオーバー周波数安定性を決定して、LOR中に標準に準拠した同期を保持できる一方、ホールドオーバー周波数安定性やワンダが重視されない場合には標準のXOを使用できます。I2CまたはSPIインターフェイスによって完全にプログラミング可能であり、内蔵EEPROMまたはROMによる起動時のカスタム周波数設定にも対応しています。EEPROMは出荷時設定済みで、インシステム・プログラミングが可能です。

| AC-LVPECL出力、fIN=25MHz、fTCXO=10MHz (OCXO)、fXO=48.0048MHz、fTCXO-TDC=20MHz |