JAJSGH0D november 2018 – october 2020 SN6505A-Q1 , SN6505B-Q1 , SN6505D-Q1

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Parameter Measurement Information

- 8 Detailed Description

- 9 Application and Implementation

- 10Power Supply Recommendations

- 11Layout

- 12Device and Documentation Support

- 13Mechanical, Packaging, and Orderable Information

9.2.2.5.3 Recommended Transformers

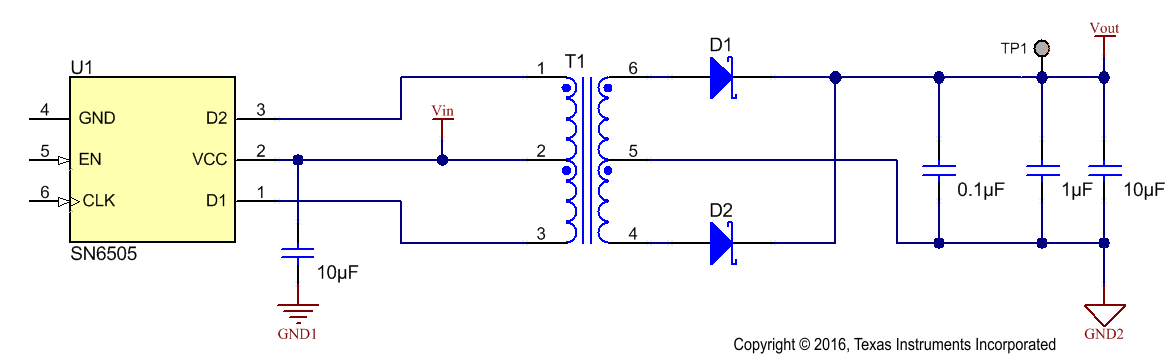

Depending on the application, use the minimum configuration in Figure 9-7 or standard configuration in Figure 9-8.

Figure 9-7 Unregulated Output for Low-Current Loads With Wide Supply Range

Figure 9-7 Unregulated Output for Low-Current Loads With Wide Supply Range Figure 9-8 Regulated Output for Stable Supplies and High Current Loads

Figure 9-8 Regulated Output for Stable Supplies and High Current LoadsThe Wurth Electronics Midcom isolation transformers in Table 9-3 are optimized designs for the device, providing high efficiency and small form factor at low-cost.

The 1:1.1 and 1:1.7 turns-ratios are designed for logic applications with wide supply rails and low load currents. These applications operate without LDO, thus achieving further cost-reduction.

Table 9-3 Recommended Isolation Transformers Optimized for the Device

| TURNS RATIO | V × T (Vμs) | ISOLATION (VRMS) | DIMENSIONS (mm) | APPLICATION | LDO(1) | ORDER NO. | MANUFACTURER |

|---|---|---|---|---|---|---|---|

| 1:1.1 ±2% | 7 | 2500 | 6.73 x 10.05 x 4.19 | 3.3 V → 3.3 V, 100mA, SN6505B/D-Q1 Refer to Figure 6-13 and Figure 6-14 | No | 760390011 | Wurth Electronics / Midcom |

| 1:1.1 ±2% | 11 | 5 V → 5 V, 100mA, SN6505B/D-Q1 Refer to Figure 6-15 and Figure 6-16 | 760390012 | ||||

| 1:1.7 ±2% | 3.3 V → 5 V, 100mA, SN6505B/D-Q1 Refer to Figure 6-17 and Figure 6-18 | 760390013 | |||||

| 1:1.3 ±2% | 3.3 V → 3.3 V, 100mA, SN6505B/D-Q1 Refer to Figure 6-19 and Figure 6-20 | Yes | 760390014 | ||||

| 1:1.3 ±2% | 5 V → 5 V, 100mA, SN6505B/D-Q1 Refer to Figure 6-21 and Figure 6-22 | 760390014 | |||||

| 1:2.1 ±2% | 3.3 V → 5 V, 100mA, SN6505B/D-Q1 Refer to Figure 6-23 and Figure 6-24 | 760390015 | |||||

| 1.23:1 ±2% | 5 V → 3.3 V, 100mA, SN6505B/D-Q1 | 750313710 | |||||

| 1:1.7 ±2% | 8.9 | 8.3 x 12.6 x 4.1 | 3.3 V → 3.3 V, 1A, SN6505B/D-Q1 Refer to Figure 6-25 and Figure 6-26 | 750316028 | |||

| 1:2.1 ±2% | 3.3 V → 5 V, 1A, SN6505B/D-Q1 Refer to Figure 6-27 and Figure 6-28 | No | 750316029 | ||||

| 1.3:1 ±2% | 10.8 | 5 V → 3.3 V, 1A, SN6505B/D-Q1 Refer to Figure 6-29 and Figure 6-30 | 750316030 | ||||

| 1:1.1 ±2% | 8.6 | 3.3 V → 3.3 V , 1A , SN6505B/D-Q1 5 V → 5 V , 1A , SN6505B/D-Q1 Refer to Figure 6-11 and Figure 6-12 | 750315371 | ||||

| 1:1.1 ±2% | 11 | 5000 | 9.14 x 12.7 x 7.37 | 3.3 V → 3.3 V, 100mA, SN6505B/D-Q1 | 750313734 | ||

| 1:1.1 ±2% | 5 V → 5 V, 100mA, SN6505B/D-Q1 | 750313734 | |||||

| 1:1.7 ±2% | 3.3 V → 5 V, 100mA, SN6505B/D-Q1 | 750313769 | |||||

| 1:1.3 ±2% | 3.3 V → 3.3 V, 100mA, SN6505B/D-Q1 5 V → 5 V, 100mA, SN6505B/D-Q1 | Yes | 750313638 | ||||

| 1:2.1 ±2% | 3.3 V → 5 V, 100mA, SN6505B/D-Q1 | 750313626 | |||||

| 1.3:1 ±2% | 5 V → 3.3 V, 100mA , SN6505B/D-Q1 | No | 750313638 | ||||

| 1:1.75 ±2% | 41 | 12.32 x 15.41 x 11.05 | 3.3 V → 3.3 V, 1A, SN6505A-Q1 Refer to Figure 6-3 and Figure 6-4 | Yes | 750316031 | ||

| 1:2 ±2% | 3.3 V → 5 V, 1A, SN6505A-Q1 Refer to Figure 6-5 and Figure 6-6 | No | 750316032 | ||||

| 1.3:1 ±2% | 42 | 5.0 V → 3.3 V, 1A, SN6505A-Q1 Refer to Figure 6-7 and Figure 6-8 | 750316033 | ||||

| 1:1.1 ±2% | 23 | 12.32 x 15.41 x 11.89 | 3.3 V → 3.3 V, 1A, SN6505A-Q1 5 V → 5 V, 1A , SN6505A-Q1 Refer to Figure 6-1 and Figure 6-2 | 750315240 | |||

| 1:1.3 ±3% | 11 | 5000 | 10.4 x 12.2 x 6.1 | 3.3 V → 3.3 V, 300mA, SN6505B/D-Q1 5 V → 5 V, 300mA , SN6505B/D-Q1 | No | HCT-SM-1.3-8-2 | Bourns |

| 1:1.5 ±3% | 34.4 | 2500 | 10 x 12.07 x 5.97 | 3.3 V → 3.3 V, 1A, SN6505A/B/D-Q1 5 V → 5 V, 1A , SN6505A/B/D-Q1 | Yes | DA2303-AL | Coilcraft |

| 1:2.2 ±3% | 21.5 | 2500 | 10 x 12.07 x 5.97 | 3.3 V → 5 V, 1A, SN6505A/B/D-Q1 | DA2304-AL |

(1) For configurations with LDO, a higher voltage than the required output voltage is generated, to allow for LDO drop-out. Figures show the voltage and efficiency at the LDO input.