JAJSPG9H August 1987 – January 2023 SN65ALS180 , SN75ALS180

PRODUCTION DATA

- 1 特長

- 2 概要

- 3 Revision History

- 4 Pin Configuration and Functions

-

5 Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 Recommended Operating Conditions

- 5.3 Thermal Information

- 5.4 Electrical Characteristics - Driver

- 5.5 Switching Characteristics - Driver

- 5.6 Symbol Equivalents

- 5.7 Electrical Characteristics - Receivers

- 5.8 Switching Characteristics - Receivers

- 5.9 Typical Characteristics

- 6 Parameter Measurement Information

- 7 Detailed Description

- 8 Application and Implementation

- 9 Device and Documentation Support

- 10Mechanical, Packaging, and Orderable Information

パッケージ・オプション

デバイスごとのパッケージ図は、PDF版データシートをご参照ください。

メカニカル・データ(パッケージ|ピン)

- N|14

サーマルパッド・メカニカル・データ

発注情報

2 概要

SN65ALS180 および SN75ALS180 差動ドライバおよびレシーバのペアは、マルチポイント・バス伝送ラインでの双方向データ通信用に設計された IC です。これらのデバイスは平衡伝送ライン用に設計されており、TIA/EIA-422-B、TIA/EIA-485-A、ITU 勧告 V.11 を満たしています。

SN65ALS180 および SN75ALS180 は、3 ステート差動ライン・ドライバと差動入力ライン・レシーバを統合しており、どちらも 5V 単一電源で動作します。ドライバとレシーバはそれぞれアクティブ High、アクティブ Low のイネーブルを備えており、それらのイネーブルを外部で互いに接続することで、方向制御として機能させることができます。ドライバの差動出力とレシーバの差動入力は、自由度が増すように個別の端子に接続されており、ドライバがディセーブルされた場合、または VCC = 0 の場合、バスへの負荷が最小化されるように設計されています。

これらのポートは広い正および負の同相モード電圧範囲を持っているため、本デバイスはパーティライン・アプリケーションに適しています。

パッケージ情報

| 部品番号 | パッケージ(1) | 本体サイズ (公称) |

|---|---|---|

| SNx5ALS176 | D (SOIC) | 8.65mm × 3.91mm |

| N (PDIP) | 19.3mm × 6.35mm |

(1) 利用可能なすべてのパッケージについては、データシートの末尾にある注文情報を参照してください。

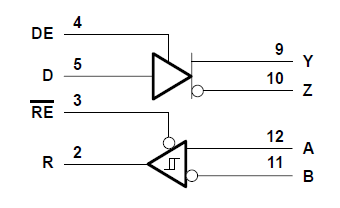

論理図 (正論理)

論理図 (正論理)