SLOS918A August 2015 – October 2015 TAS5404-Q1

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

- 9 Detailed Description

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

- PHD|64

サーマルパッド・メカニカル・データ

- PHD|64

発注情報

10 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

10.1 Application Information

The TAS5404-Q1 device is a four-channel class-D audio amplifier designed for use in automotive head units and external amplifier modules. The TAS5404-Q1 device incorporates all the functionality required to perform in the demanding OEM applications area.

10.2 Typical Application

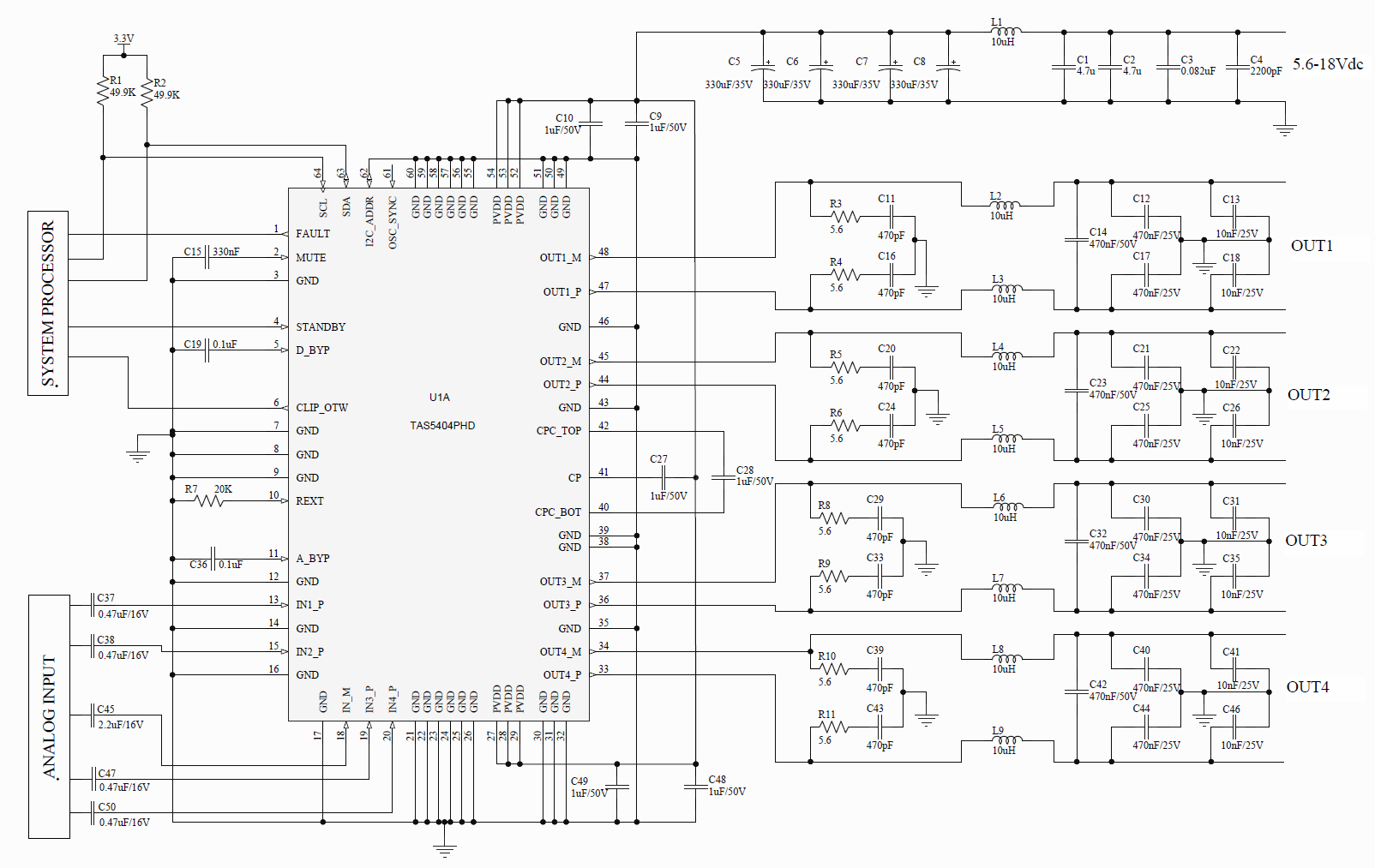

Figure 20 shows a typical application circuit for the TAS5404-Q1 device.

Figure 20. TAS5404-Q1 Typical Application Schematic

Figure 20. TAS5404-Q1 Typical Application Schematic

10.2.1 Design Requirements

- Power Supplies

- Communication

- External Components

The TAS5404-Q1 device requires only a single power supply compliant with the recommended operation range. The TAS5404-Q1 device is designed to work with either a vehicle battery or regulated boost power supply.

The TAS5404-Q1 device communicates with the system controller with both discrete hardware control pins and with I 2 C. The TAS5404-Q1 device is an I 2 C slave and thus requires a master. If a master I 2 C-compliant device is not present in the system, the TAS5404-Q1 device can only be used with the default settings. Diagnostic information is limited to the discrete reporting FAULT pin.

Table 24 lists the components required for the TAS5404-Q1 device.

Table 24. Supporting Components

| EVM Designator | Quanity | Value | Size | Description | Use in Application |

|---|---|---|---|---|---|

| C37, C38, C47, C50 | 4 | 0.47μF ± 10% | 1206 | Film, 16-V | Analog audio input filter, bypass |

| C5, C6, C7, C8 | 4 | 330 μF ± 20% | 10 mm | Low-ESR aluminum capacitor, 35-V | Power supply |

| C9, C10, C48, C49, C27, C28 | 6 | 1 μF ± 10% | 0805 | X7R ceramic capacitor, 50-V | Power supply |

| C45 | 1 | 2.2uF ± 10% | 0805 | Film, 16-V | Analog audio input filter, bypass |

| C14, C23, C32, C42 | 4 | 470nF ± 10% | 0805 | X7R ceramic capacitor, 50-V | Amplifier output filtering |

| C11, C15, C20, C24, C29, C33, C39, C43 | 8 | 470 pF ± 10% | 0603 | X7R ceramic capacitor, 50-V | Amplifier output snubbers |

| C19, C36 | 2 | 0.1 μF ± 10% | 0603 | X7R ceramic capacitor, 25-V | Power supply |

| C4 | 1 | 2200 pF ± 10% | 0603 | X7R ceramic capacitor, 50-V | Power supply |

| C3 | 1 | 0.082 μF ± 10% | 0603 | X7R ceramic capacitor, 25-V | Power supply |

| C1, C2 | 2 | 4.7 μF ± 10% | 1206 | X7R ceramic capacitor, 25-V | Power supply |

| C12, C17, C21, C25, C30, C34, C40, C44 | 8 | 0.47 μF ± 10% | 0603 | X7R ceramic capacitor, 25-V | Output EMI filtering |

| C15 | 1 | 220nF ± 10% | 0603 | X7R ceramic capacitor, 25-V | Mute timing |

| L1 | 1 | 10 μH ± 20% | 13.5 mm ×13.5 mm | Shielded ferrite inductor | Power supply |

| L2, L3, L4, L5, L6, L7, L8, L9 | 8 | 10 μH ± 20% | 12 mm × 14 mm | Dual inductor | Amplifier output filtering |

| R1, R2 | 2 | 49.9 kΩ ± 1% | 0805 | Resistors, 0.125-W | Analog audio input filter |

| R3, R4, R5, R6, R8, R9, R10, R11 | 8 | 5.6 Ω ± 5% | 0805 | Resistors, 0.125-W | Output snubbers |

| R7 | 1 | 20.0 kΩ ± 1% | 0805 | Resistors, 0.125-W | Power supply |

10.2.2 Detailed Design Procedure

10.2.2.1 Hardware and Software Design

- Hardware Schematic Design: Using Figure 20 as a guide, integrate the hardware into the system schematic.

- Following the recommended layout guidelines, integrate the TAS5404-Q1 device and the supporting components into the system PCB file.

- Thermal Design: The TAS5404-Q1 device has an exposed thermal pad which requires proper soldering. For more information, see the application reports Semiconductor and IC Package Thermal Metrics (SPRA953), and the PowerPAD Thermally Enhanced Package (SLMA002G).

- Develop software: The EVM User's Guide has detailed instructions for how to set up the TAS5404-Q1 device, interpret diagnostic information, and so forth. For information about control registers, see the Table 7 section.

For questions and support go to the E2E forums.

10.2.2.2 Parallel Operation (PBTL)

The TAS5404-Q1 device can drive more current by paralleling BTL channels on the load side of the LC output filter. Parallel operation requires identical I2C settings for any two paralleled channels to have reliable system performance and even power dissipation on multiple channels. For smooth power up, power down, and mute operation, the same control commands (such as mute, play, Hi-Z, and so on) should be sent to the paralleled channels at the same time. The TAS5404-Q1 device also supports load diagnostics for parallel connection. Paralleling on the TAS5404-Q1 device side of the LC output filter is not supported, because it can result in device failure. When paralleling channels, use the parallel BTL I2C control bits in register 0x0D. Parallel channels 1 and 2, and/or channels 3 and 4. Setting these bits allows the thermal foldback to react on both channels equally. Provide the audio input to channel 2 if paralleing channels 1 and 2, and channel 3 if paralleling channels 3 and 4.

10.2.2.3 Input Filter Design

The IN_M pin should have an impedance to GND that is equivalent to the parallel combination of the input impedances of all IN_P channels combined, including any source impedance from the previous stage in the system design. For example, if each of the four IN_P channels have a 1-µF dc blocking capacitor, 1 kΩ of series resistance due to an input RC filter, and 1 kΩ of source resistance from the DAC supplying the audio signal, then the IN_M channel should have a 4-µF capacitor in series with a 500-Ω resistor to GND (4 × 1 µF in parallel = 4 µF; 4 × 2 kΩ in parallel = 500 Ω).

10.2.2.4 Amplifier Output Filtering

The output FETs drive the amplifier outputs in an H-bridge configuration. These transistors are either fully off or on. The result is a square-wave output signal with a duty cycle that is proportional to the amplitude of the audio signal. The amplifier outputs require a low-pass filter to filter out the PWM modulation carrier frequency. People frequently call the filter the L-C filter, due to the presence of an inductive element L and a capacitive element C to make up the 2-pole low-pass filter. The L-C filter attenuates the carrier frequency, reducing electromagnetic emissions and smoothing the current waveform which the load draws from the power supply. See the Class-D LC Filter Design application report (SLOA119) for a detailed description on proper component selection and design of an L-C filter based upon the desired load and response.

10.2.2.5 Line Driver Applications

In many automotive audio applications, the end user would like to use the same head unit to drive either a speaker (with several ohms of impedance) or an external amplifier (with several kilohms of impedance). The design is capable of supporting both applications; however, the one must design the output filter and system to handle the expected output load conditions.