JAJSCG3 September 2016 TLV171 , TLV2171 , TLV4171

PRODUCTION DATA.

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 改訂履歴

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11デバイスおよびドキュメントのサポート

- 12メカニカル、パッケージ、および注文情報

8 Application and Implementation

NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI’s customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

8.1 Application Information

The TLVx171 family of operational amplifiers provides high overall performance in a large number of general-purpose applications. As with all amplifiers, applications with noisy or high-impedance power supplies require decoupling capacitors placed close to the device pins. In most cases, 0.1-µF capacitors are adequate. Follow the additional recommendations in the Layout Guidelines section in order to achieve the maximum performance from this device. Many applications can introduce capacitive loading to the output of the amplifier (potentially causing instability). One method of stabilizing the amplifier in such applications is to add an isolation resistor between the amplifier output and the capacitive load. The design process for selecting this resistor is given in the Typical Application section.

8.2 Typical Application

This circuit can be used to drive capacitive loads such as cable shields, reference buffers, MOSFET gates, and diodes. The circuit uses an isolation resistor (RISO) to stabilize the output of an operational amplifier. RISO modifies the open-loop gain of the system to ensure that the circuit has sufficient phase margin.

Figure 30. Unity-Gain Buffer With RISO Stability Compensation

Figure 30. Unity-Gain Buffer With RISO Stability Compensation

8.2.1 Design Requirements

The design requirements are:

- Supply voltage: 30 V (±15 V)

- Capacitive loads: 100 pF, 1000 pF, 0.01 μF, 0.1 μF, and 1 μF

- Phase margin: 45° and 60°

8.2.2 Detailed Design Procedure

Figure 30 shows a unity-gain buffer driving a capacitive load. Equation 1 shows the transfer function for the circuit in Figure 30. Not shown in Figure 30 is the open-loop output resistance of the operational amplifier, RO.

The transfer function in Equation 1 has a pole and a zero. The frequency of the pole (fp) is determined by (RO + RISO) and CLOAD. Components RISO and CLOAD determine the frequency of the zero (fz). A stable system is obtained by selecting RISO such that the rate of closure (ROC) between the open-loop gain (AOL) and 1/β is 20 dB/decade. Figure 31 illustrates this concept. The 1/β curve for a unity-gain buffer is 0 dB.

Figure 31. Unity-Gain Amplifier With RISO Compensation

Figure 31. Unity-Gain Amplifier With RISO Compensation

ROC stability analysis is typically simulated. The validity of the analysis depends on multiple factors, especially the accurate modeling of RO. In addition to simulating the ROC, a robust stability analysis includes a measurement of overshoot percentage and ac gain peaking of the circuit using a function generator, oscilloscope, and gain and phase analyzer. Phase margin is then calculated from these measurements. Table 2 shows the overshoot percentage and ac gain peaking that correspond to phase margins of 45° and 60°. For more details on this design and other alternative devices that can be used in place of the TLV171, see the Precision Design, Capacitive Load Drive Solution Using an Isolation Resistor.

Table 2. Phase Margin versus Overshoot and AC Gain Peaking

| PHASE MARGIN | OVERSHOOT | AC GAIN PEAKING |

|---|---|---|

| 45° | 23.3% | 2.35 dB |

| 60° | 8.8% | 0.28 dB |

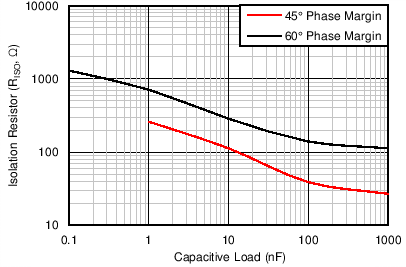

8.2.3 Application Curve

Using the described methodology, the values of RISO that yield phase margins of 45º and 60º for various capacitive loads were determined. The results are shown in Figure 32.

Figure 32. Isolation Resistor Required for Various Capacitive Loads to Achieve a Target Phase Margin

Figure 32. Isolation Resistor Required for Various Capacitive Loads to Achieve a Target Phase Margin