at TA = 25°C, VIN = 1.4 V or

VIN = VOUT(nom) + 0.3 V (whichever is greater),

VBIAS = open, VOUT(nom) = 0.8 V, VEN = 1.1 V,

CIN = 10 μF, COUT = 22 μF, CNR/SS = 0 nF,

CFF = 0 nF, and PG pin pulled up to VIN with 100 kΩ

(unless otherwise noted)

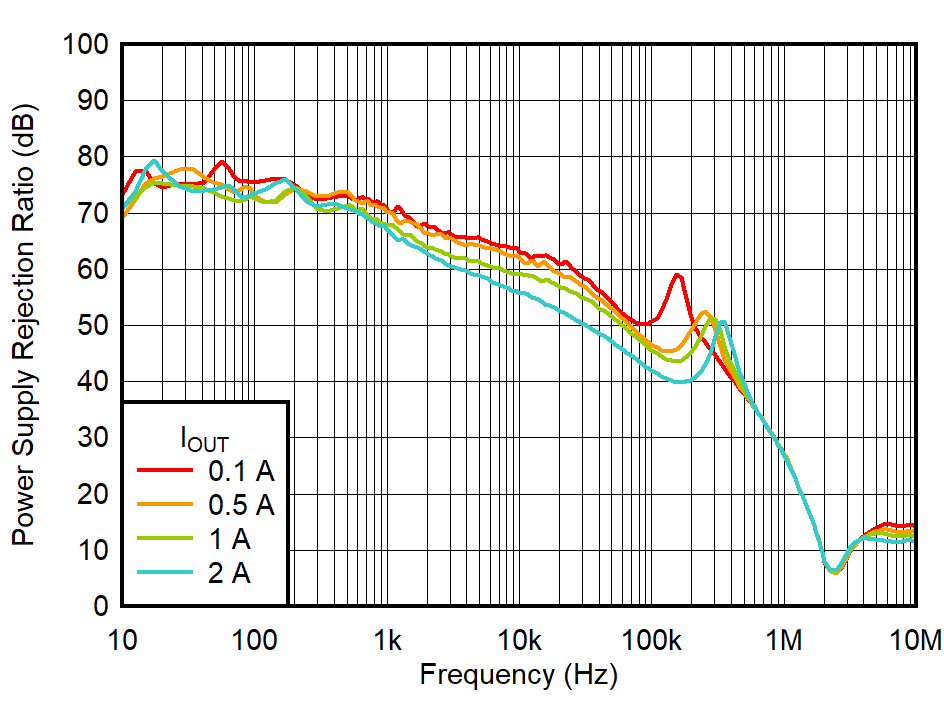

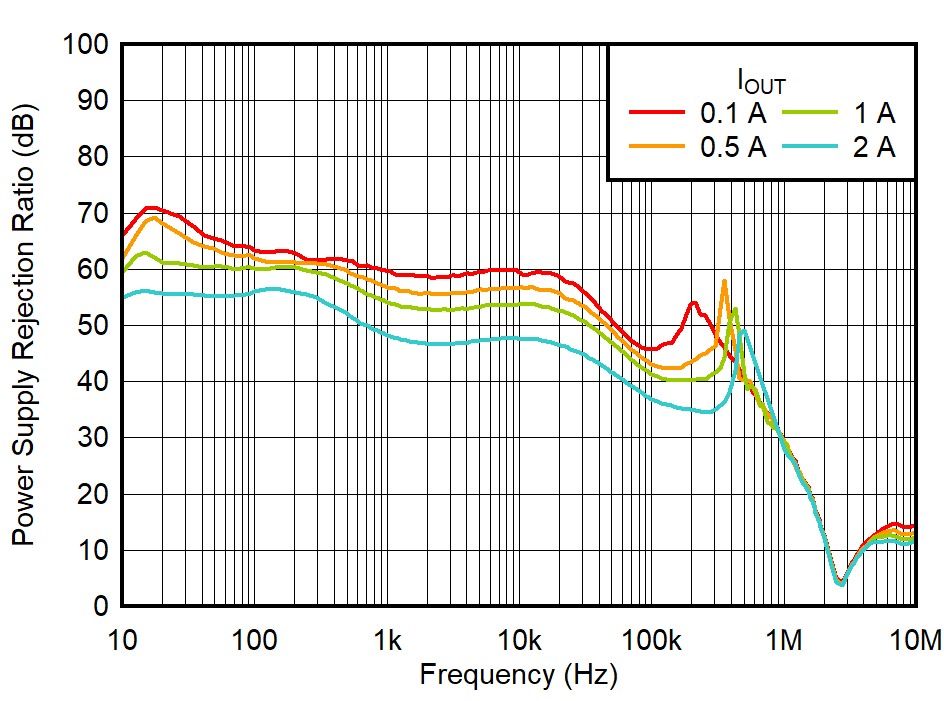

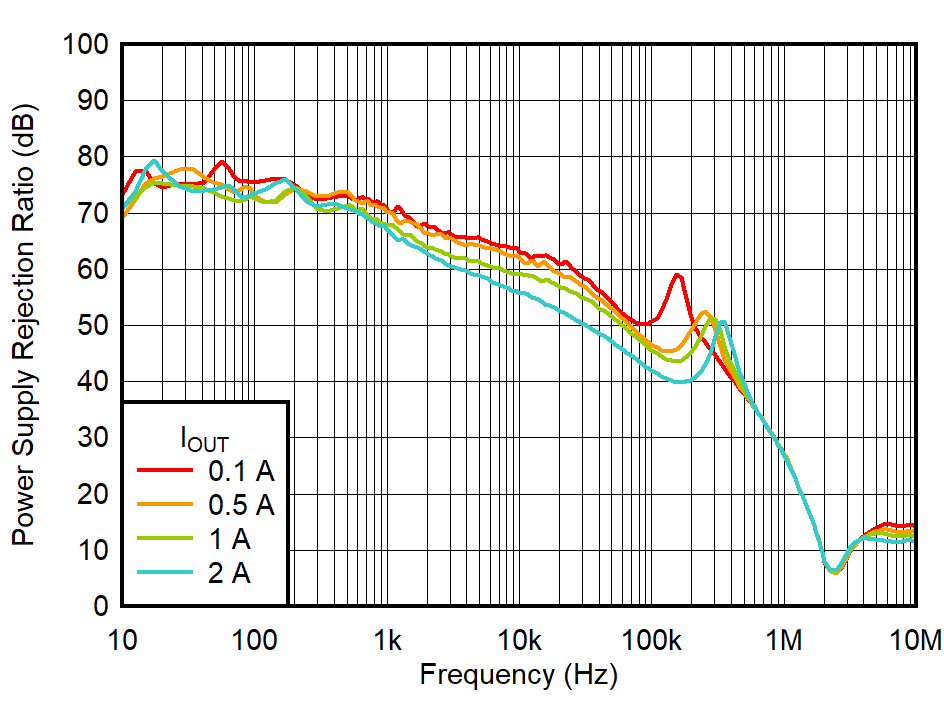

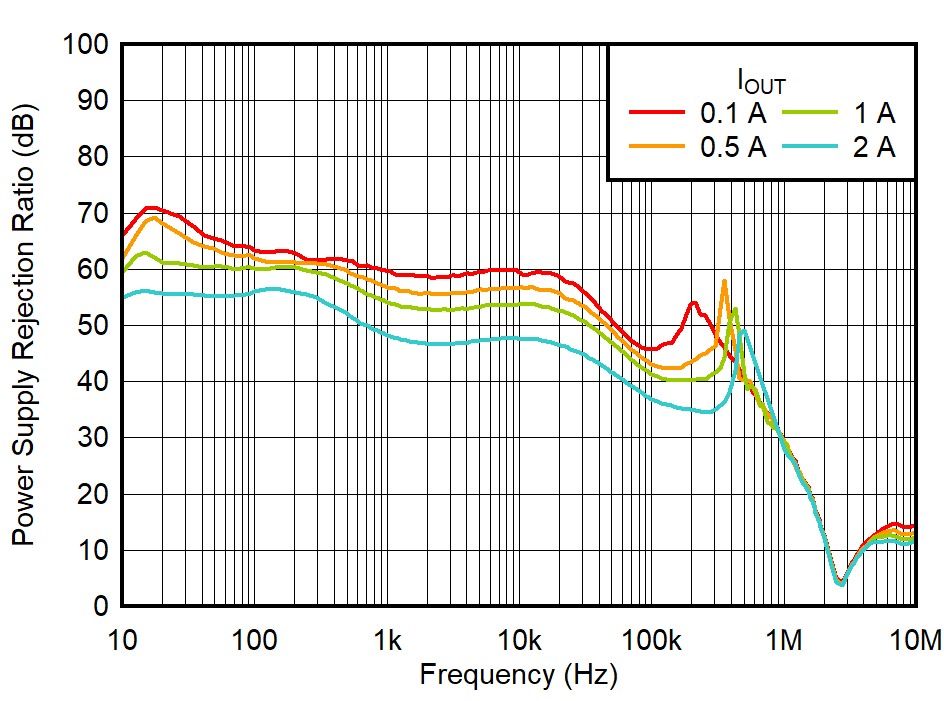

VIN = 1.1 V, VBIAS = 5 V,

COUT = 22 μF, CNR/SS = 10 nF,

CFF = 10

nF |

Figure 7-43 PSRR

vs Frequency and IOUT

| IOUT = 1 A, COUT = 22 μF,

CNR/SS = 10 nF, CFF = 10

nF |

| |

Figure 7-45 PSRR

vs Frequency and VIN

VIN = VOUT + 0.3 V or

VIN = 1.1 V (whichever is greater) and

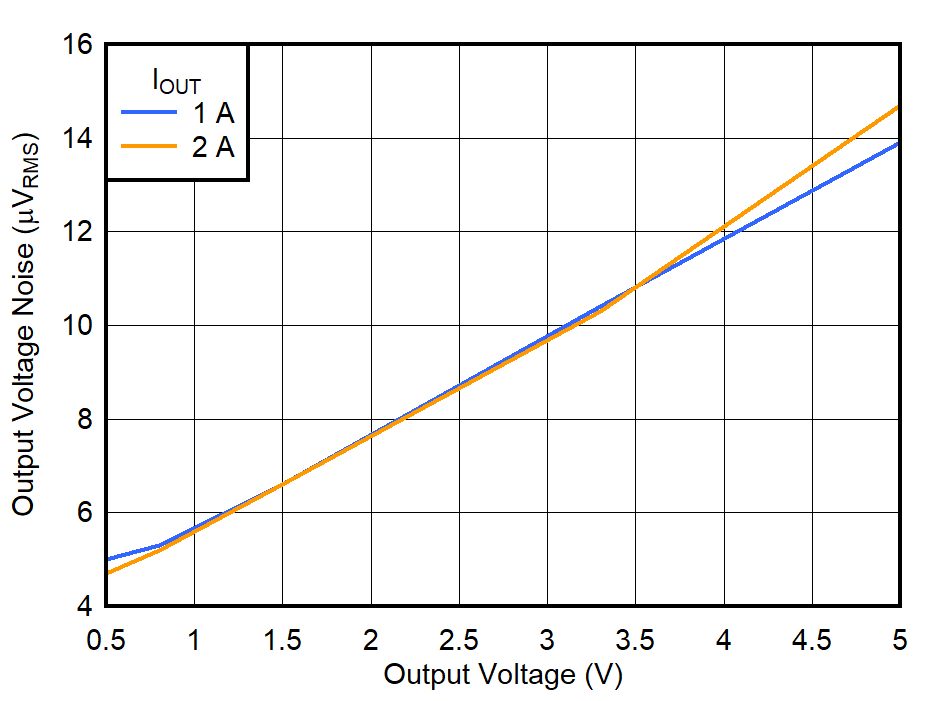

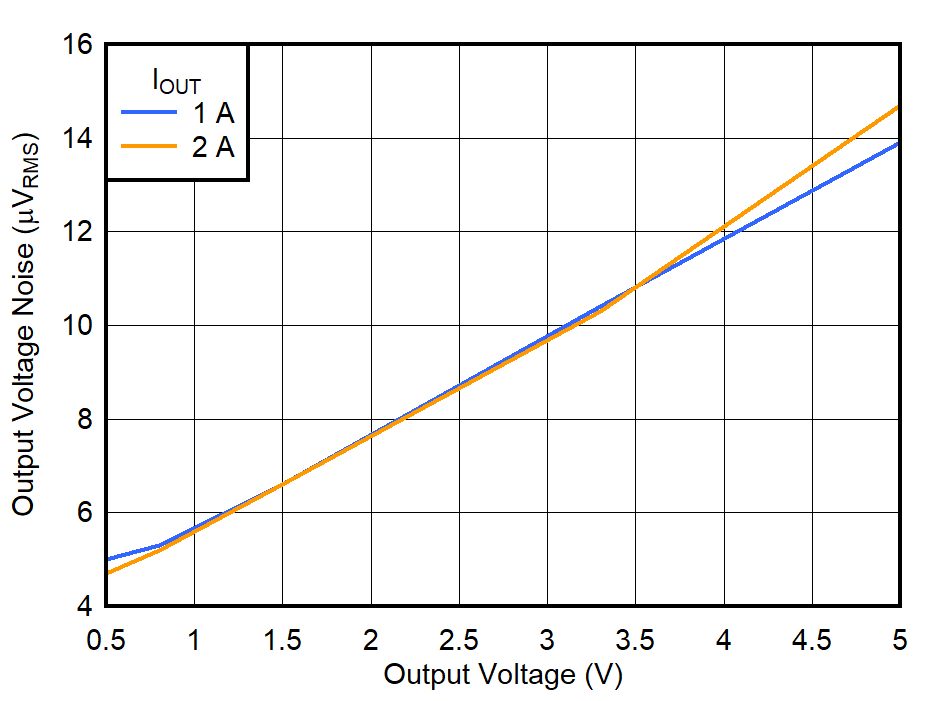

VBIAS = 5 V for VOUT ≤ 2.2 V,

COUT = 47

μF || 10μF || 10μF, CNR/SS = 10 nF,

CFF = 10 nF, RMS noise BW = 10 Hz to 100

kHz |

Figure 7-47 Output Voltage Noise vs VOUT Figure 7-49 Dropout Voltage vs Output Current With BIAS

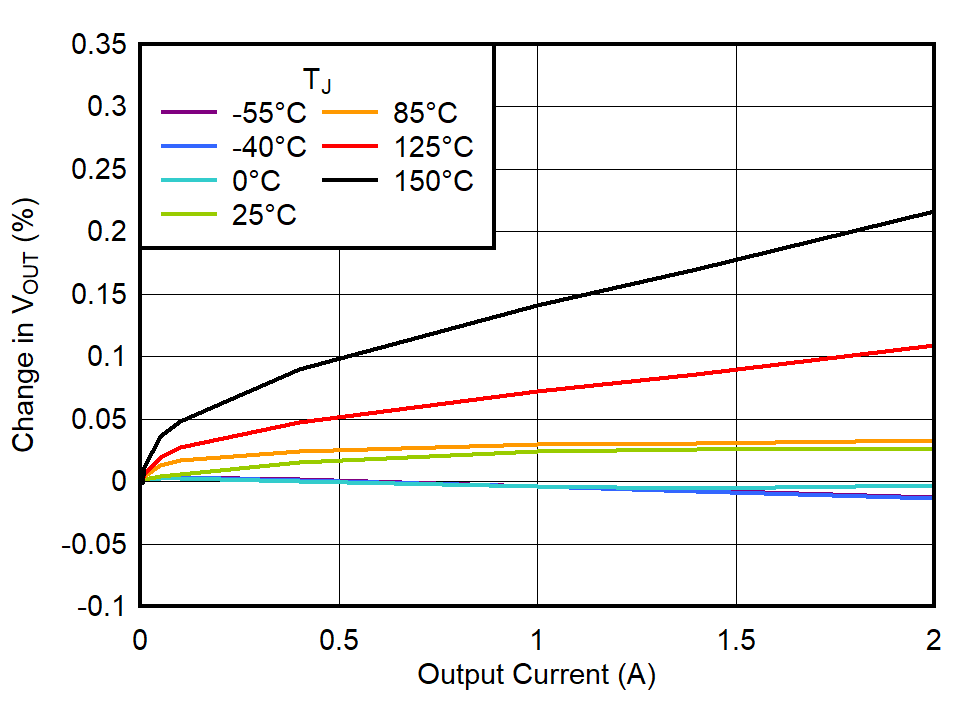

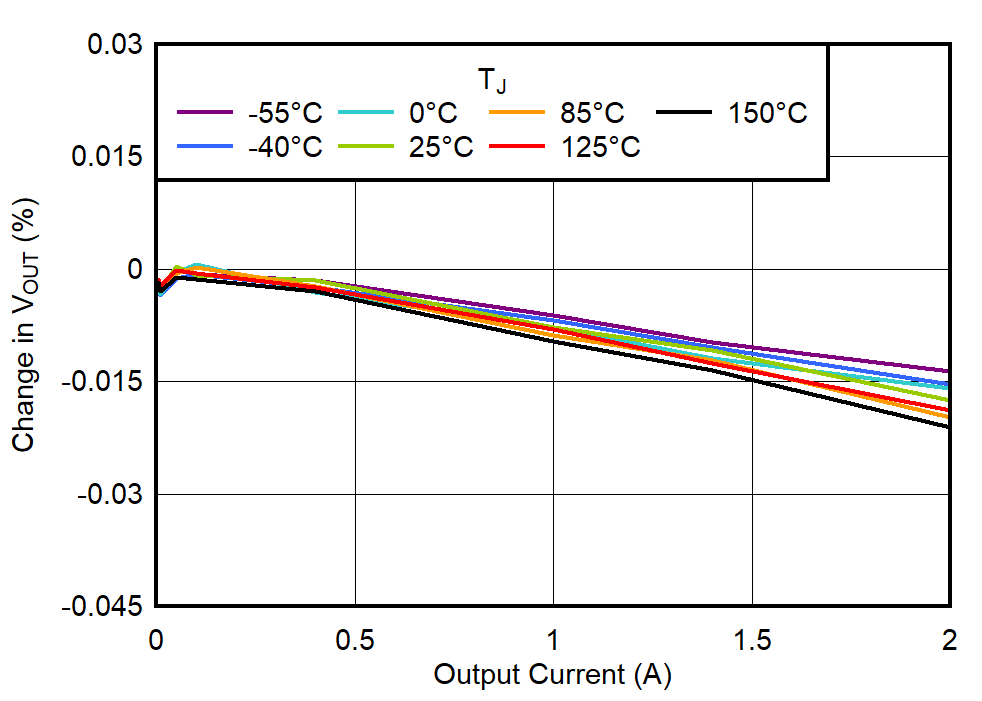

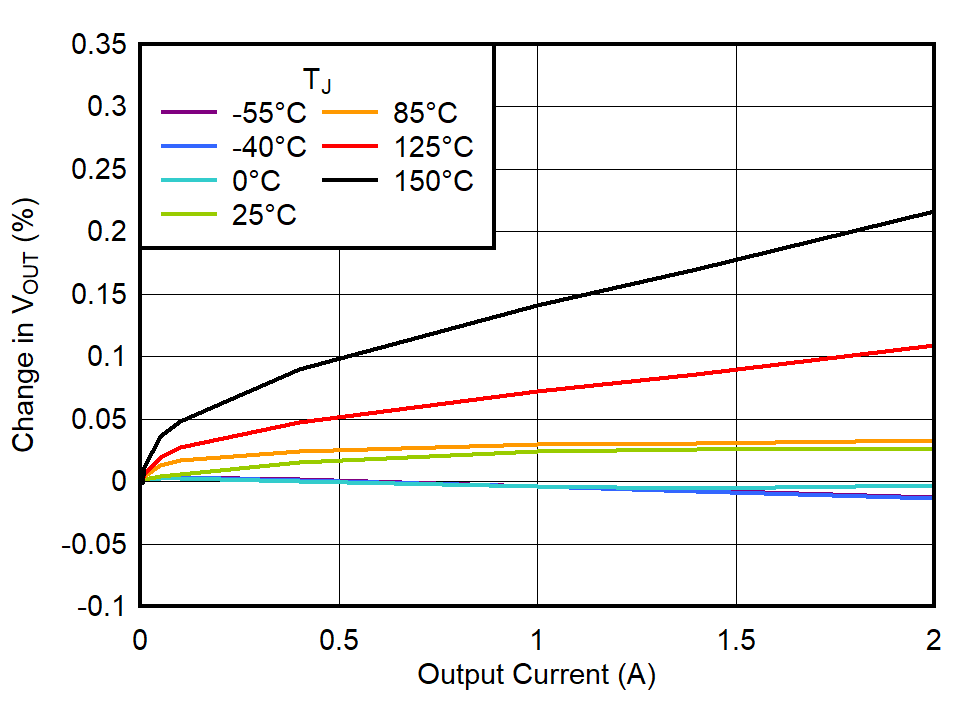

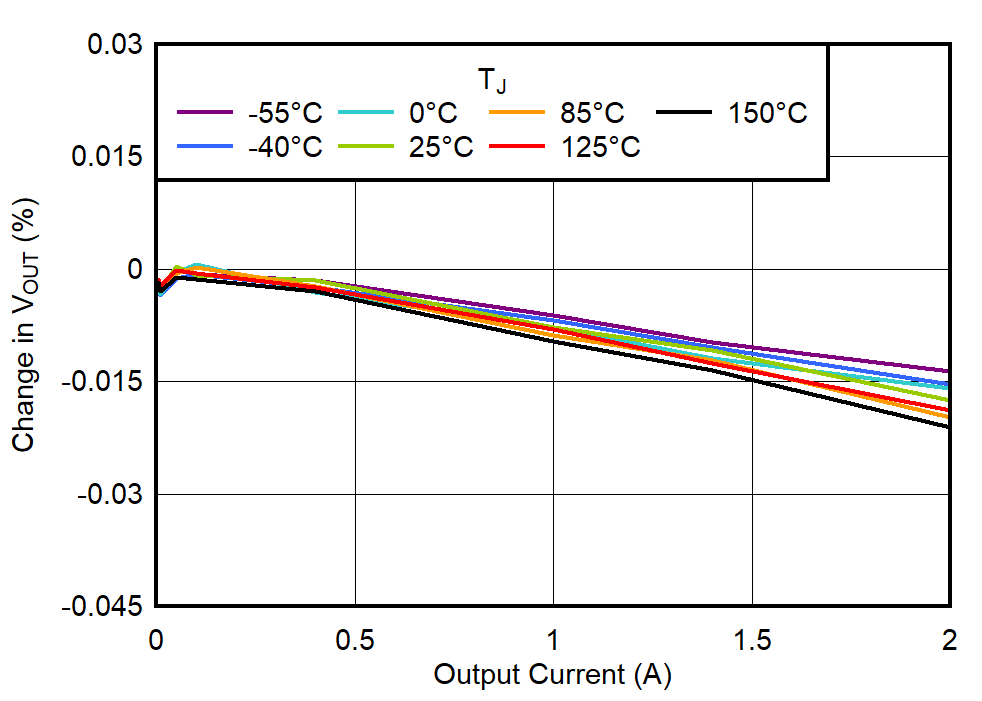

Figure 7-49 Dropout Voltage vs Output Current With BIAS Figure 7-51 Load

Regulation

Figure 7-51 Load

Regulation

| VIN = 5.55 V, VOUT = 5.15

V |

Figure 7-53 Load

Regulation (5-V Output)

| VOUT = 0.5 V, VIN = 1.1 V,

IOUT = 5 mA, VBIAS = 5

V |

Figure 7-55 Line

Regulation With BIAS Figure 7-57 Ground Pin Current vs Input Voltage

Figure 7-57 Ground Pin Current vs Input Voltage Figure 7-59 Shutdown Current vs Input Voltage

Figure 7-59 Shutdown Current vs Input Voltage Figure 7-61 INR/SS Current vs Input Voltage

Figure 7-61 INR/SS Current vs Input Voltage Figure 7-63 VBIAS UVLO vs Temperature

Figure 7-63 VBIAS UVLO vs Temperature Figure 7-65 PG

Voltage vs PG Current Sink

Figure 7-65 PG

Voltage vs PG Current Sink Figure 7-67 PG

Threshold vs Temperature

Figure 7-67 PG

Threshold vs Temperature

VIN = 1.4 V, IOUT = 1 A,

COUT = 22 μF, CNR/SS = 10 nF,

CFF = 10

nF |

Figure 7-44 PSRR

vs Frequency and VBIAS

VIN = 5.5 V, VOUT = 5 V,

COUT = 47 μF || 10 μF || 10μF,

CNR/SS = 10 nF,

CFF = 10 nF |

Figure 7-46 PSRR

vs Frequency and IOUT (VOUT = 5 V) Figure 7-48 Dropout Voltage vs Output Current Without BIAS

Figure 7-48 Dropout Voltage vs Output Current Without BIAS Figure 7-50 Dropout Voltage vs Output Current (High VIN)

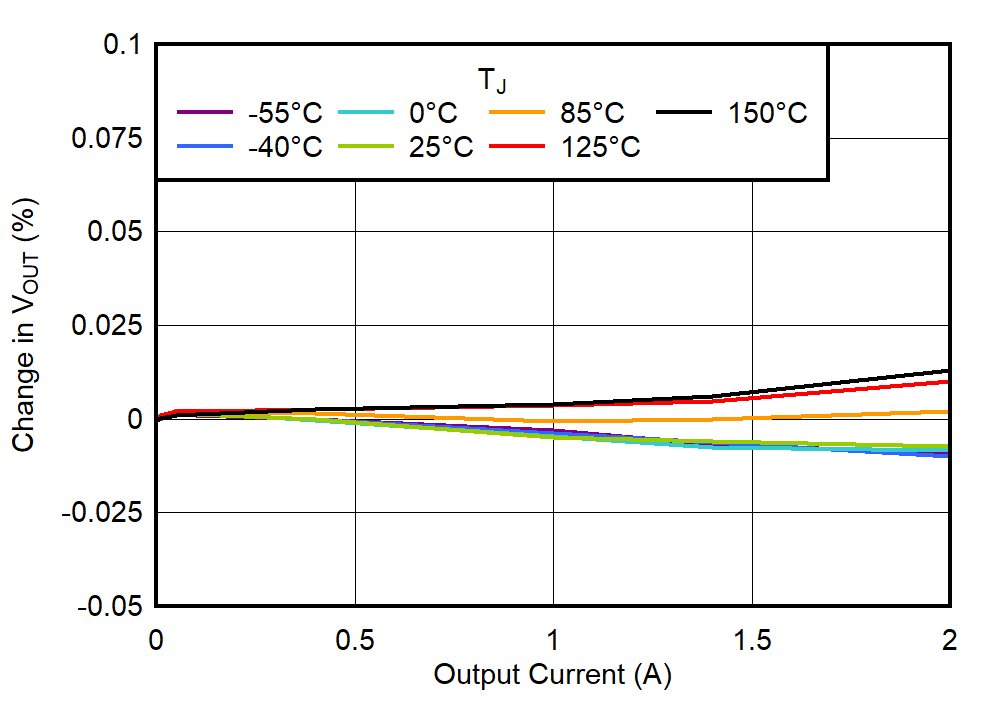

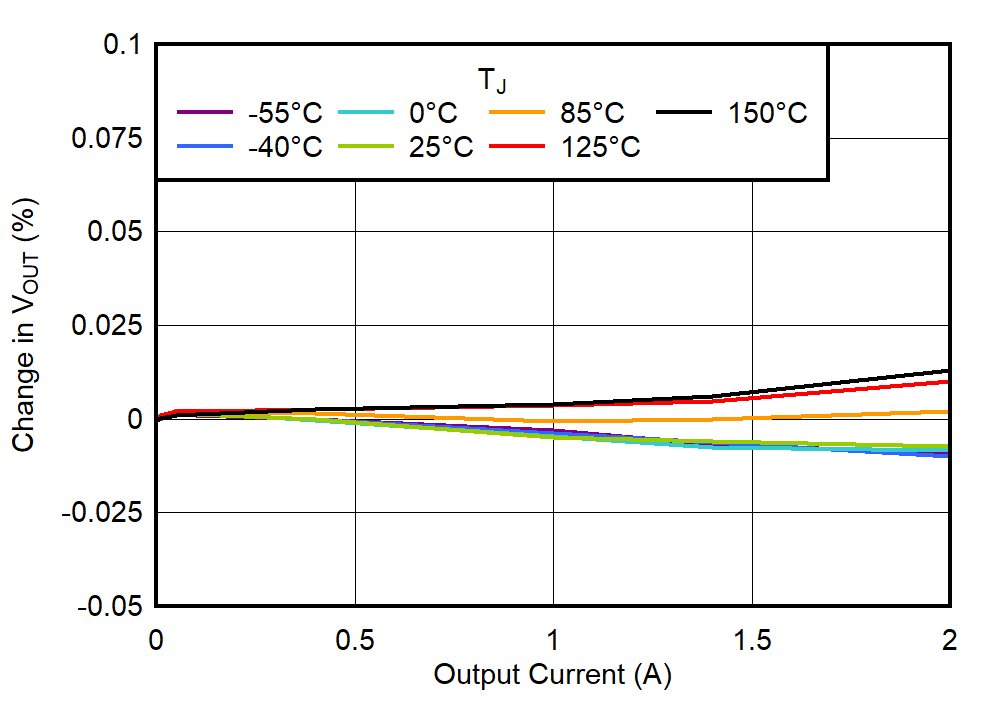

Figure 7-50 Dropout Voltage vs Output Current (High VIN) Figure 7-52 Load

Regulation (3.3-V Output)

Figure 7-52 Load

Regulation (3.3-V Output)

| VOUT = 0.5 V, IOUT = 5

mA |

| |

Figure 7-54 Line

Regulation vs VIN Figure 7-56 Line

Regulation vs VIN (5.2-V Output)

Figure 7-56 Line

Regulation vs VIN (5.2-V Output) Figure 7-58 BIAS

Pin Current vs Bias Voltage

Figure 7-58 BIAS

Pin Current vs Bias Voltage Figure 7-60 Shutdown Current vs Bias Voltage

Figure 7-60 Shutdown Current vs Bias Voltage Figure 7-62 VIN UVLO vs Temperature

Figure 7-62 VIN UVLO vs Temperature Figure 7-64 Enable Threshold vs Temperature

Figure 7-64 Enable Threshold vs Temperature Figure 7-66 PG

Voltage vs PG Current Sink

Figure 7-66 PG

Voltage vs PG Current Sink