JAJSLS2D march 2013 – april 2021 UCD3138064

PRODUCTION DATA

- 1

- 1 特長

- 2 アプリケーション

- 3 概要

- 4 Functional Block Diagram

- 5 Revision History

- 6 Device Options

- 7 Pin Configuration and Functions

-

8 Specifications

- 8.1 Absolute Maximum Ratings #GUID-DB56AA00-A5E9-4426-9853-ACC9CCD10656/SLUSB727999

- 8.2 Handling Ratings

- 8.3 Recommended Operating Conditions

- 8.4 Thermal Information

- 8.5 Electrical Characteristics

- 8.6 Timing Characteristics

- 8.7 PMBus/SMBus/I2C Timing

- 8.8 Power On Reset (POR) / Brown Out Reset (BOR)

- 8.9 Typical Clock Gating Power Savings

- 8.10 Typical Characteristics

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3

Feature Description

- 9.3.1 System Module

- 9.3.2 Peripherals

- 9.3.3 Automatic Mode Switching

- 9.3.4 DPWMC, Edge Generation, Intramux

- 9.3.5 Filter

- 9.3.6 Communication Ports

- 9.3.7 Real Time Clock

- 9.3.8 Timers

- 9.3.9 General Purpose ADC12

- 9.3.10 Miscellaneous Analog

- 9.3.11 Brownout

- 9.3.12 Global I/O

- 9.3.13 Temperature Sensor Control

- 9.3.14 I/O Mux Control

- 9.3.15 Current Sharing Control

- 9.3.16 Temperature Reference

- 9.4 Device Functional Modes

- 9.5 Memory

-

10Applications and

Implementation

- 10.1 Application Information

- 10.2

Typical Application

- 10.2.1 Design Requirements

- 10.2.2 Detailed Design Procedure

- 10.2.3 Application Curves

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

パッケージ・オプション

メカニカル・データ(パッケージ|ピン)

サーマルパッド・メカニカル・データ

発注情報

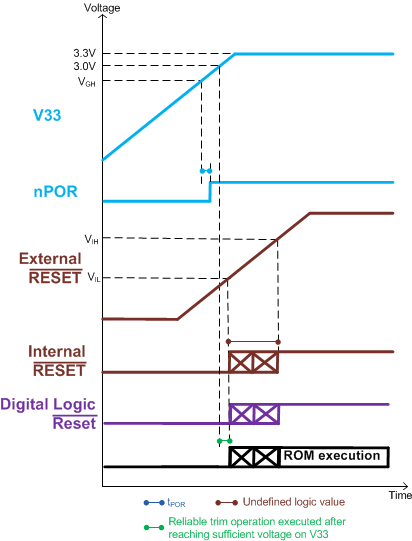

11.4 Recommendation for RC Time Constant of RESET Pin for UCD3138 and UCD3138064

Ideally, the ARM core should begin execution of ROM code only after V33>3V. The ROM code reads trim values and loads trim registers. Lack of sufficient voltage during this operation can result in unexpected device functioning. Depending on V33 slew rate, the duration for which there is insufficient voltage on V33 is varied. During this time, a reliable trim operation is not ensured. Applying an RC filter between V33 and the RESET pin can increase the delay from V33 power up to the device coming out of reset.

Figure 11-2 Recommended Timing Diagram of V33 and

RESET for UCD3138 and UCD3138064

Figure 11-2 Recommended Timing Diagram of V33 and

RESET for UCD3138 and UCD3138064Example Solution:

If the V33 supply slew rate is 0.6 V/ms, then the minimum τ required is calculated as follows:

If R and C are 2.21 k and 2.2 uF, then τ evaluates as:

These values of 2.21 kΩ and 2.2 µF will ensure that the RESET will be a logic-0 until V33 crosses 3V. [τ > τRESET_MIN]