JAJT284 February 2024 LM74700-Q1 , LM74900-Q1

4 優先順位付きパワー マルチプレクサの構成

優先順位付きパワー マルチプレクサは、1 次電源電圧が指定のスレッショルドを下回ると、1 次電源から補助電源 (AUX) または 2 次電源に自動的に切り替えます。利用可能で許容可能な制限範囲内であれば、常に 1 次電源が負荷に電力を供給する最初の電源になります。たとえば、パワー ディストリビューション ユニット内でサブシステムへの 1 次電源の上流スマート ヒューズが切れた場合、優先順位付きパワー マルチプレクサ回路は自動的に AUX 電源を出力に接続し、1 次電源をその出力から切断して、サブシステム動作の中断を防止します。上流スマート ヒューズがリセットされ、1 次電源電圧が許容可能なスレッショルドまで上昇すると、優先順位付きパワー マルチプレクサ回路は自動的に 1 次電源を出力に接続し、AUX 電源を遮断します。

パワー マルチプレクサ回路では、各電源レールの 2 つのバック ツー バック MOSFET を制御するために、LM74800-Q1 や LM74900-Q1 などのコントローラが必要です。1 次電源と AUX 電源の両方が存在していて許容範囲内にあり、1 次電源が負荷に電力を供給している場合、1 次電源電圧が AUX 電源電圧より高いときに、AUX パス コントローラで逆電流をブロックする必要があります。同様に、1 次電源電圧が AUX 電源電圧より低い場合、AUX パス コントローラで順方向電流をブロックする必要があります。これにより、優先順位が最高の 1 次電源が負荷に電力を供給し、AUX 電源は 1 次電源と負荷の両方から絶縁されます。

LM74900-Q1 理想ダイオード コントローラは、外付けのバック ツー バック N チャネル MOSFET を駆動および制御して、電力パスのオン / オフ制御と過電流および過電圧保護を備えた理想ダイオード整流器をエミュレートします。図 5 に、2 つの LM74900-Q1 デバイスを共通ドレイン トポロジで使用した優先順位付きパワー マルチプレクサの回路図を示します。VAUX パスの LM74900-Q1 の過電圧ピンは、VPRIM が何らかの理由で遮断されたときに VAUX 電源が直ちに負荷に接続され、負荷への継続的な電力供給が維持されるように構成されてい ます。

図 5 LM74900-Q1 を使用した代表的な優先順位付きパワー マルチプレクサ アプリケーションの回路

図 5 LM74900-Q1 を使用した代表的な優先順位付きパワー マルチプレクサ アプリケーションの回路パワー マルチプレクサ回路は、VPRIM が遮断されたとき、または許容範囲外になったときに、負荷が VAUX からの電源に切り替わる間の出力電圧降下を低く維持しようとします。切り替え中の出力電圧降下を低く維持するには、(Q2 をオフにして) VPRIM の電力パスをオフにする間に、VAUX パスの LM74900-Q1 によって駆動される負荷スイッチ FET (Q4) を迅速にオンにする必要があります。ただし、突入電流を制限する低速スタートアップを実現するため、HGATE ピンには 55μA のゲート電流のみが供給されるよう設計されており、これは HGATE をすばやく High にするには低すぎます。抵抗 (RCP)、トランジスタ (Q5)、ダイオード (D2) を使用した小型の回路では、HGATE のソース電流を増加できます。Q5 ではチャージ ポンプ コンデンサで HGATE を直接 High にプルアップできるため、Q5 のエミッタを Q4 のゲートに接続して、ゲート ソース電流を増やすこともできます。または、RCP の抵抗値を変更して Q4 ゲート ソース電流を調整することもできます。D2 は、Q5 を迂回して Q4 をオフにするパスを形成します。

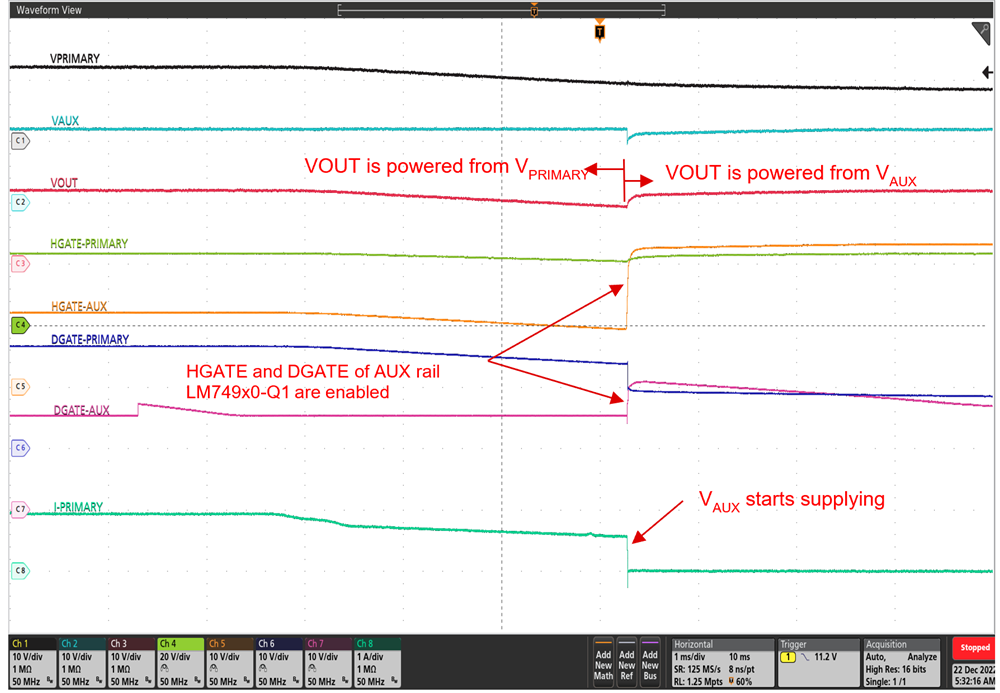

図 6 に、VPRIM が遮断され、負荷が VAUX レールに迅速に切り替わったときの波形を示します。AUX レールの HGATE は 20µs 以内にオンになり、ドロップイン出力電圧を低減します。

図 6 パワー マルチプレクサ アプリケーションでの VPRIM から VAUX への切り替え

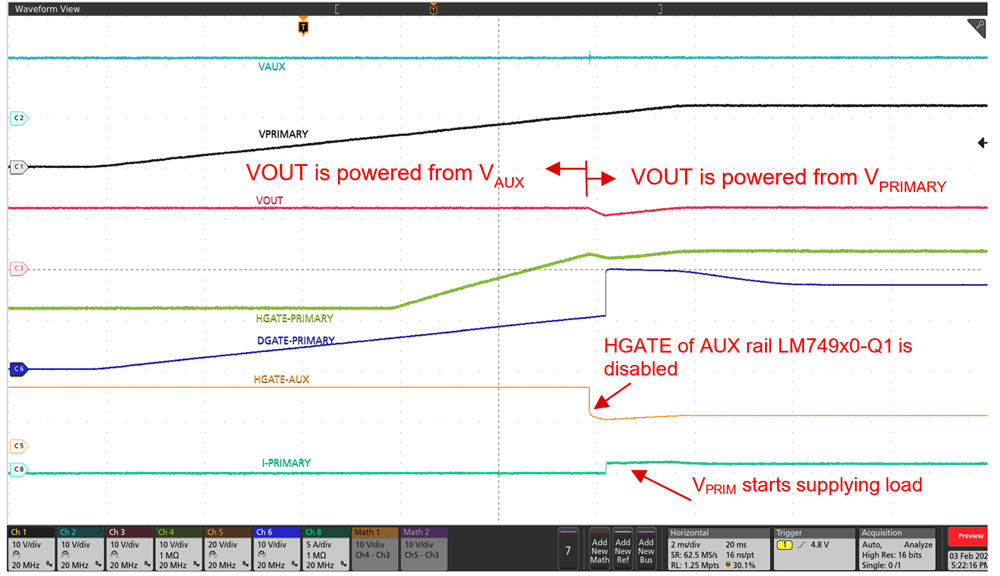

図 6 パワー マルチプレクサ アプリケーションでの VPRIM から VAUX への切り替え図 7 に、VPRIM が許容可能なレベルに回復し、優先順位付きパワーマルチプレクサ回路が負荷を VPRIM (VAUX よりも優先順位が高い) に最小の電圧降下でスムーズに切り替えたときの波形を示します。

図 7 パワー マルチプレクサ アプリケーションでの VAUX から VPRIM への切り替え

図 7 パワー マルチプレクサ アプリケーションでの VAUX から VPRIM への切り替え表 1 に、各種理想ダイオード コントローラと、それぞれの機能セットに基づいてサポートできる冗長電源トポロジを示します。

| 理想ダイオード コントローラ | OR 接続構成 | 電源多重化構成 (バック ツー バック FET 制御) | |

|---|---|---|---|

| 共通ドレイン トポロジ | 共通ソース トポロジ | ||

| LM5050-1-Q1 | ✓ | × | × |

| LM70700-Q1 | ✓ | × | × |

| LM7480-Q1 | ✓ | ✓ | ✓ |

| LM74720-Q1 | ✓ | ✓ | × |

| LM74900-Q1 | ✓ | ✓ | × |

| LM74930-Q1 | ✓ | × | ✓ |