NESA011B march 2023 – june 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507

9.3 佈線、導孔和其他 PCB 元件

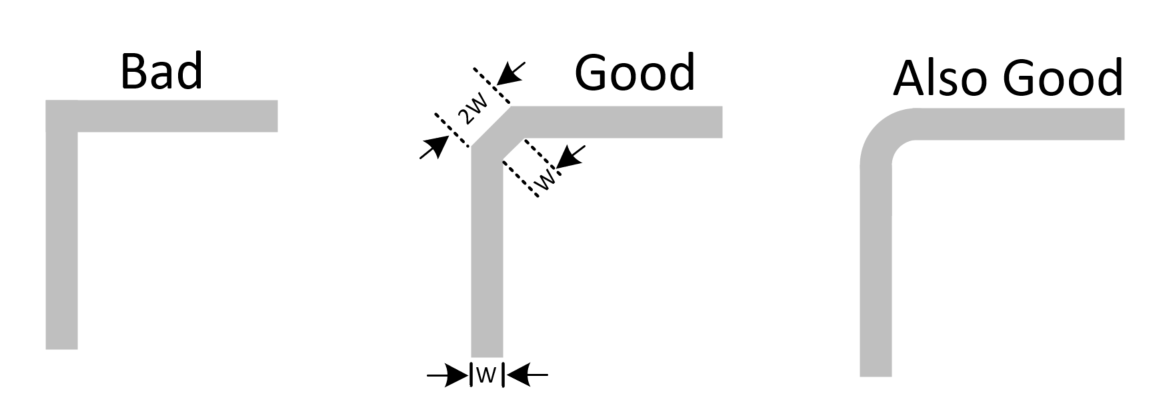

走線中若有直角,可能會導致更多輻射。角區域的電容增加,特性阻抗也有所改變。此阻抗變化會造成反射。避免在走線中出現直角彎折,嘗試以至少兩個 45° 角來佈線。爲了儘量減少任何阻抗變化,最佳的佈線方式是採用圓角彎折,如 圖 9-3 所示。

圖 9-3 正確與不正確的直角走線彎折方式

圖 9-3 正確與不正確的直角走線彎折方式爲了儘量減少串擾,不僅在單層的兩個訊號間,在相鄰層間也要以互呈 90° 方式進行佈線。較複雜的電路板在佈線時需使用導孔;但使用導孔時請務必小心,因為其會增加額外電感與電容,且會因特性阻抗變化而產生反射。導孔也會增加走線長度。使用差動訊號時,請在兩條走線中使用導孔,或也補償另一條走線中的延遲。

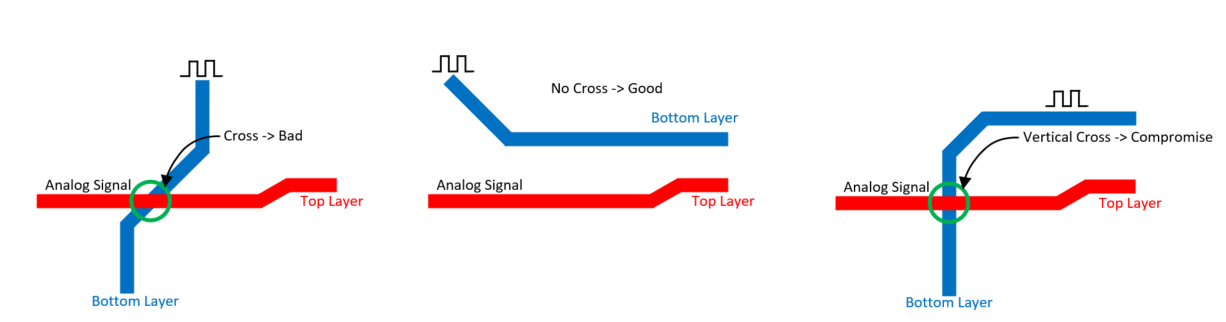

針對訊號走線,請更加注意高頻脈衝訊號的影響,特別是對相對較小類比訊號 (如感測器訊號) 的影響。過多交越會將高頻訊號的電磁雜訊與類比訊號耦合,進而產生訊號的低訊噪比,並影響訊號品質。因此在設計時必須避免交越。但如果真的有無法避免的交越,建議採用垂直相交以將電磁雜訊的干擾降至最低。圖 9-4 說明如何減少此雜訊。

圖 9-4 正確與不正確的類比訊號和高頻訊號走線交越方式

圖 9-4 正確與不正確的類比訊號和高頻訊號走線交越方式