SBAA590 june 2023 ADC12DJ5200RF , ADC32RF52 , ADC32RF54 , ADC32RF55 , ADC34RF52 , ADC34RF55

3.2 Foreground Calibration

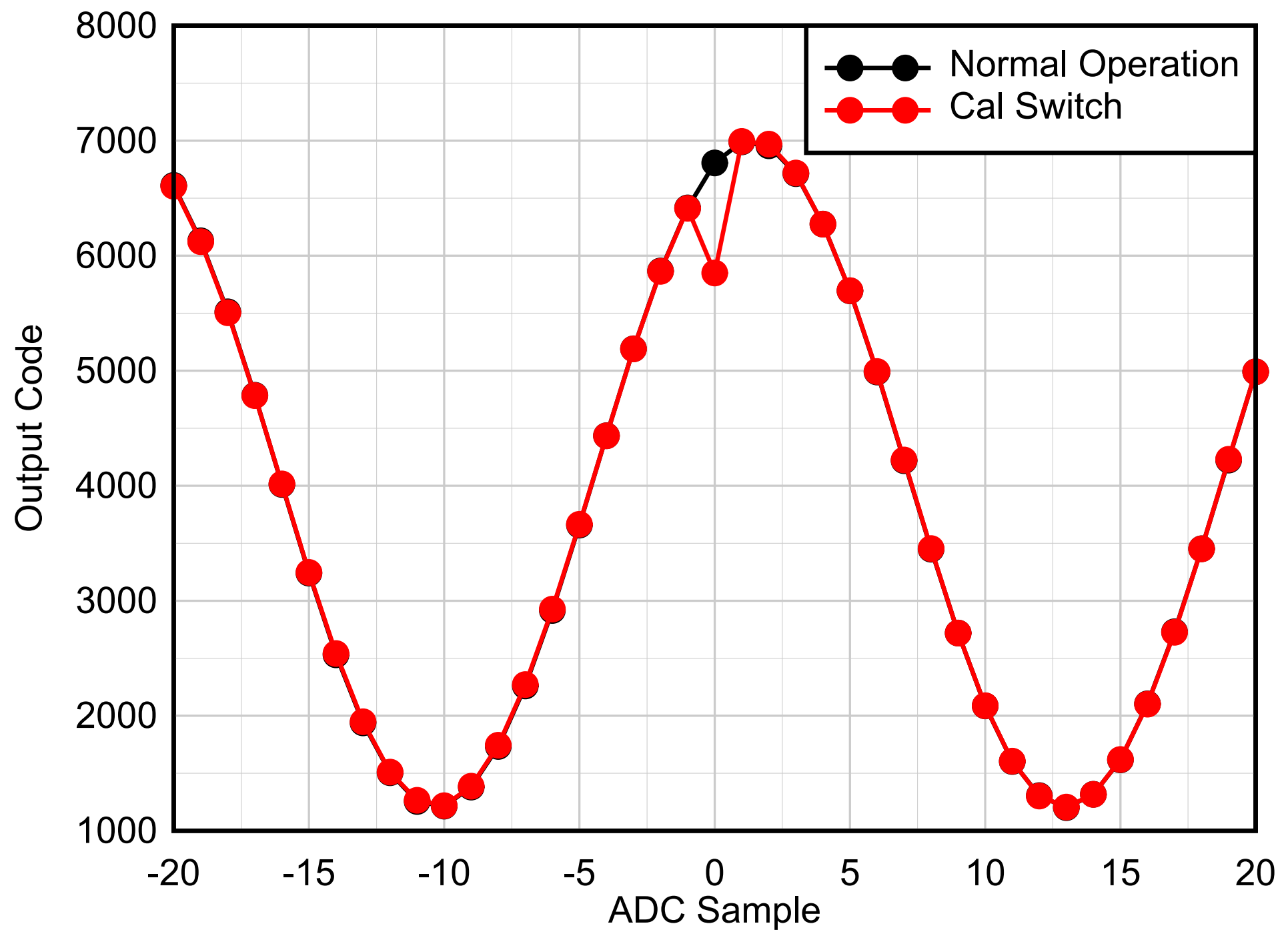

Foreground calibration, also known as real-time calibration, resembles that of the one-time calibration in Section 3.1, however instead of taking place before valid data is transmitted, foreground calibration occurs while the device is actively sending data. The resulting data at the downstream processor or FPGA can appear distorted during calibration and does not always resemble the input signal. Foreground calibration requires that the downstream processor or FPGA determine when a calibration is required by monitoring performance of the converter in real-time. In the case of foreground calibration for the ADC32RF55, additional ADC cores (the specific number of additional cores is mode dependent) are continuously calibrated behind the scenes and the moment foreground calibration takes place, the uncalibrated ADC core is swapped out with one of the calibrated ADC cores. As a result, a single sample can be dropped as shown in Figure 3-3. Foreground calibration can often be triggered using the SPI interface or through a general purpose hardware input (GPIO).

Figure 3-3 ADC32RF55 Output Codes During

Foreground Calibration

Figure 3-3 ADC32RF55 Output Codes During

Foreground Calibration