SBOA553A August 2022 – January 2023 OPA593

2 AC Considerations

The new component test application in consideration not only has the high 0.5-A output current requirement, but the added need to drive a load capacitance up to 1 µF and remain stable in the process. One microfarad is a high-capacitance load for most op amps to drive, including the OPA593. Compensation is required to assure stability, prevent oscillation, and retain good transient response characteristics.

Since the circuit must be compensated to drive the high-capacitance load it makes sense to have a plan going forward because the Leader-follower circuit has multiple loops; the U1 and U2 local loops, and a third loop that begins at the U1 output, goes to the U2 non-inverting input, and then back through Rb2 and Rb1. Compensation made to any one loop has some effect on the overall AC frequency response of the complete circuit. How to go about effectively compensating the circuit may not be readily evident and difficult to determine.

The approach documented here was to compensate U1 and U2 individually, as if each one independently drives the high-capacitive load. Next, evaluate the overall effectiveness of the stability compensation when they are connected back together. This approach turned out to work well for this OPA593 Leader-follower circuit.

Figure 2-1 shows the same circuit configuration as the Figure 1-3 circuit, but with the additional compensation components included. This circuit has proven completely effective driving a load consisting the 1-µF capacitor in parallel a resistance of 100 Ω to 500 Ω. A load resistance added in parallel with the 1-µF load capacitance serves to draw a DC current similar to an active component under test. Both U1 and U2 compensated as explained and as seen in Figure 2-1 have respective unity-gain bandwidths of approximately 55 kHz and 100 kHz. The OPA593 parallel output amplifier bandwidth is sufficient for the intended component test application.

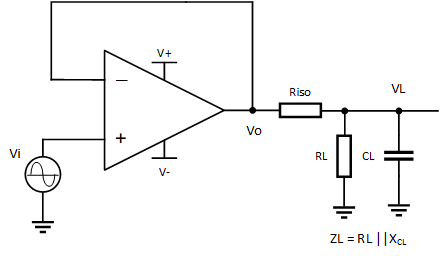

The easiest place to start from a compensation explanation is with U2 in Figure 2-1. U2 is the same follower and 3.0-Ω series output ballast resistor as in the Figure 1-3 DC circuit. What may not be apparent is that Rb2 is doubling as an “Riso” output load isolation resistor now. Adding Riso is one method of compensating an op amp, increasing its ability to drive a high-capacitive load CL and remain stable doing so. A simplified version of the U2 circuit is illustrated in Figure 2-2 where the output ballast resistor is serving the additional function as Riso.

Figure 2-2 Operational Amplifier Riso Compensation for High Cload

Figure 2-2 Operational Amplifier Riso Compensation for High CloadThe Riso compensation method is presented and further explained in the online: TI Precision Labs Series – Amplifiers, Op amp Stability – Capacitive Loads.

When the Riso compensation method is used with a single op amp as seen in Figure 2-2, a voltage divider is created by the Riso resistor and RL impedance to ground that follows it. The voltage at the divider output can be less than what is needed. However, when applied as it is in the Leader-follower circuit in Figure 2-1, the output voltage level is automatically corrected level by circuit configuration.

Compensation of U1 is a bit more involved than what was required for U2. As seen in the Figures, the 3.0-Ω ballast resistor Rb1 is positioned within the feedback loop. It is not possible to move the Rb1 outside the loop without completely undoing the way the Figure 2-1 Leader-follower configuration is designed to function.

When the output of the U1 leader amplifier is directly loaded by a 1-µF load capacitance to ground, the phase margin is highly diminished. A TINA-Spice simulation of the U1 circuit indicates a phase margin less than 0°; therefore, the circuit is unstable. The majority of the phase margin reduction is caused by the addition of 1-μF load capacitance at the output with the addition of a few degrees of reduction caused by the necessary inclusion of Rb1 within the U1 feedback loop interacting with the load capacitance.

A gain and phase plot vs. frequency obtained from the simulation demonstrates the normal –90° phase shift coming from the dominant-pole compensation of the op amp, plus another low-frequency pole breaking at about 3 kHz. That second pole adds an additional –90° of phase shift to the overall –180° phase shift. As a result of these first two poles, the phase margin falls to 0° around 23 kHz. The second pole is attributable to the U1 open-loop output impedance (Zo), the 3.0 Ω Rb1 in series with its Zo, the 1-µF load capacitance, and other impedances in the output circuitry.

The compensation goal for U1 is to keep the loop phase from falling to 0°, and to stay as high as possible above as 0°. Adding a Riso resistor like that used with U2, external to the feedback loop, is not an option here. Another method for compensating U1 is needed.

It was determined that compensating U1 for the phase shift added by the 3-kHz second pole can be accomplished by adding a capacitor across the 4.5-kΩ, feedback resistor on U1. That capacitor, when set to a value of 1.5 nF, introduces a zero into the U1 loop response in the 20- to 30-kHz frequency range. The loop-gain roll-off, which was –40 dB/dec without the capacitor, then bends upward to reduce the roll-off rate to –20 dB/dec. The added zero counters the negative phase shift of the second pole and flattens the phase sufficiently such that the phase margin of U1 remains is about 40° at 56 kHz, where the loop-gain passes through 0 dB.

The compensations applied at U1 and U2 result in phase margins of about 40° and 70°, respectively, when driving the 1-µF, 500-Ω parallel load. Those margins increase as the load resistance of the output load is reduced in value. The margins increase to 69° and 89°, respectively, when the output load is just a 500-Ω resistance.

The OPA593 parallel output amplifier compensated as described and as shown in Figure 2-1 remained stable with a variety of parallel R and C load combinations tested on the bench. The compensation developed for this amplifier has been optimized for that specific load. If the load capacitance is further increased, or even decreased, the phase margin can decrease. Compensation developed for a specific complex load does not necessarily make sure it provides an acceptable high phase margin with a different load.