SLUAAM4 December 2023 BQ76905 , BQ76907

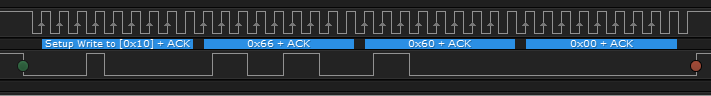

1.1 Alarm Enable - 0x66

Table 3-9 shows the Alarm Enable command that uses command 0x66. By default, the register setting for Alarm Enable is set to 0xC200. In Figure 1-1, the setting is changed to 0x0060. The data is in little endian format. The device address for the BQ7690x is 0x10 (8-bits) where the LSB is the R/W bit. A direct command follows the format I2C_Write(I2C_ADDR, Command, DataBlock), so for this example, the command can be I2C_Write(0x10, 0x66, [0x60, 0x00]).

Table 1-1 Alarm Enable Command Description

| Command | Name | Units | Type | Description |

|---|---|---|---|---|

| 0x66 | Alarm Enable | Hex | H2 | Mask for Alarm Status(). Can be written to change during operation to change which alarm sources are enabled. |

Figure 1-1 Captured I2C Waveform for

Setting Alarm Enable to 0x0060

Figure 1-1 Captured I2C Waveform for

Setting Alarm Enable to 0x0060