SLUU818A April 2012 – February 2022 TPS51219

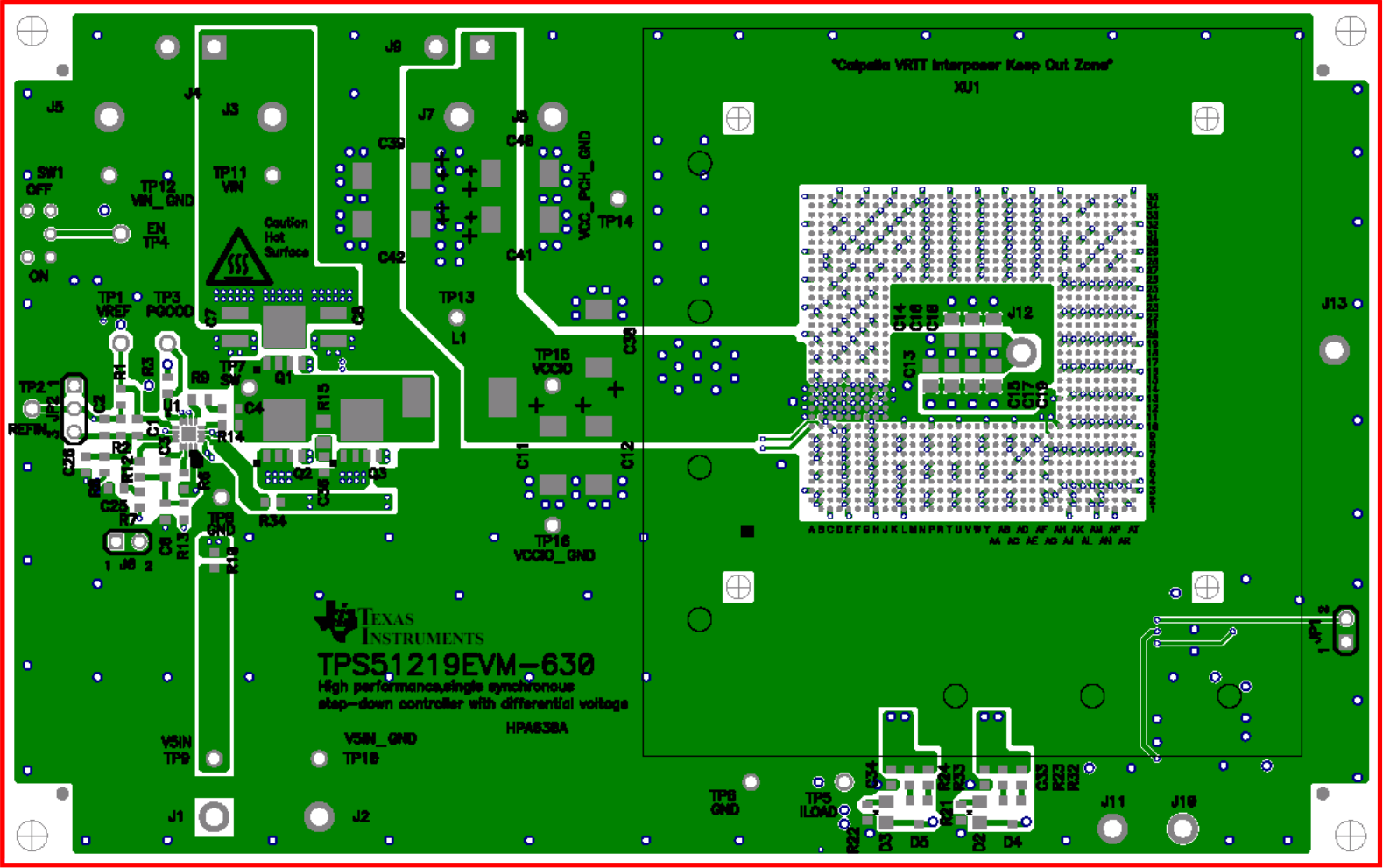

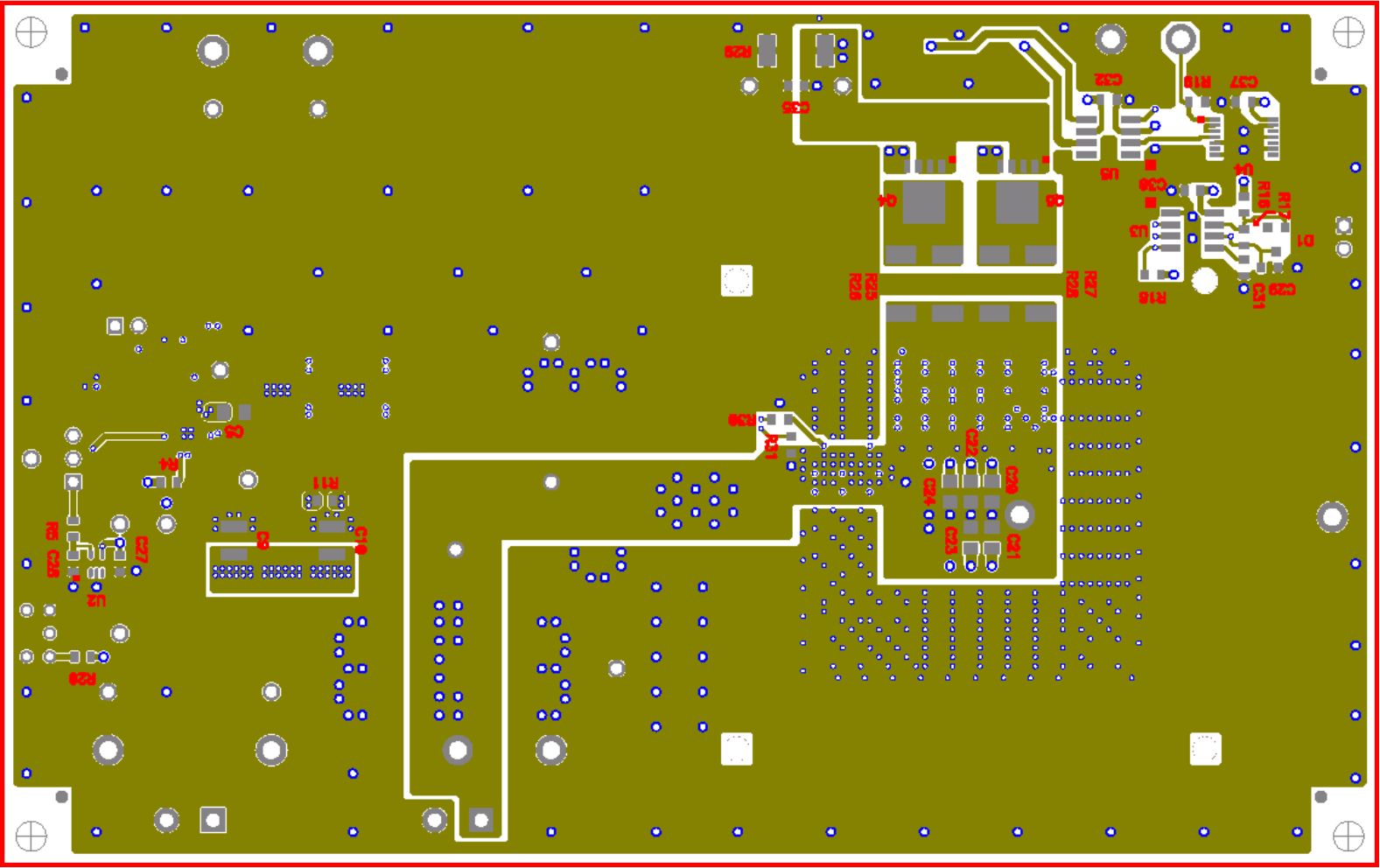

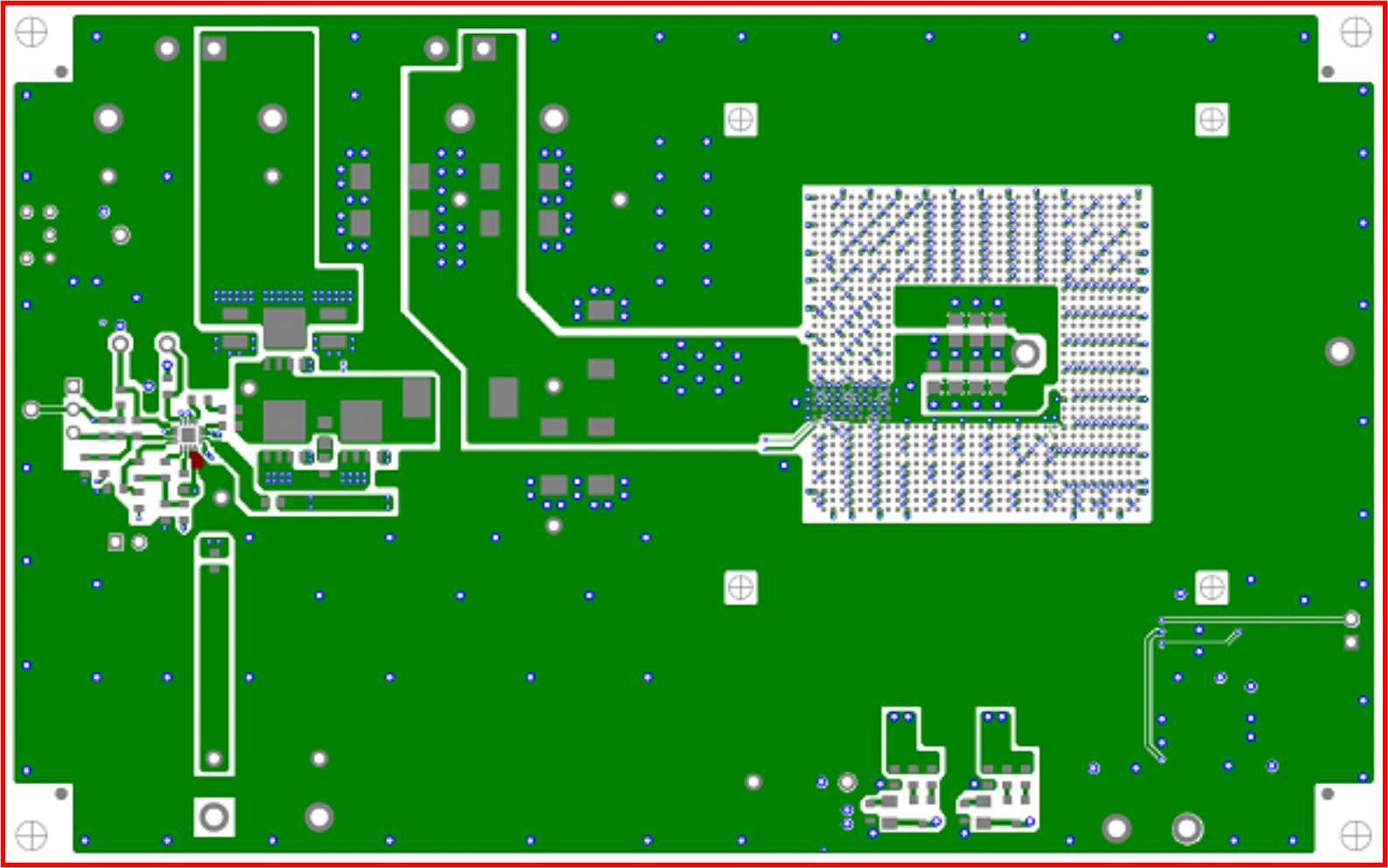

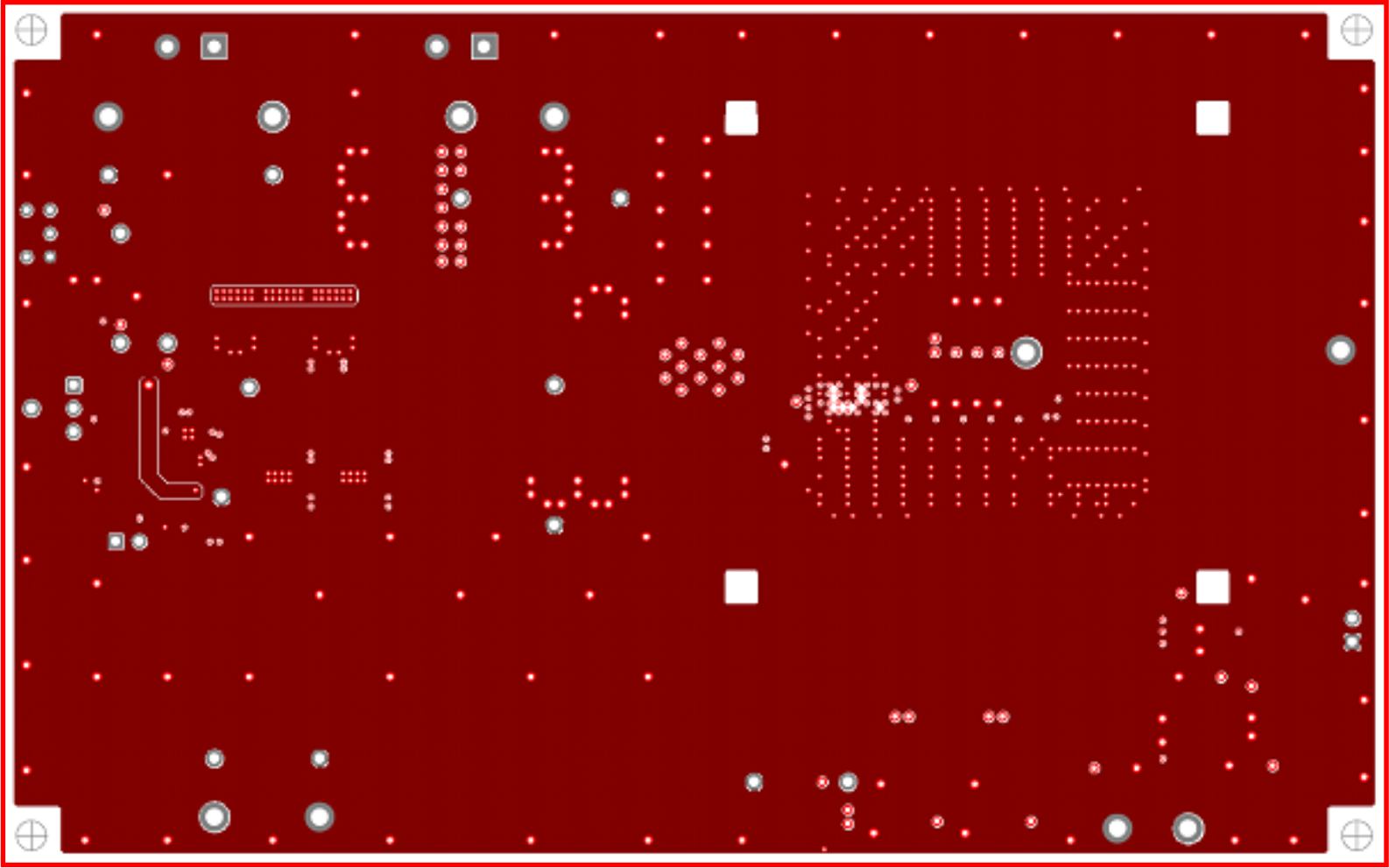

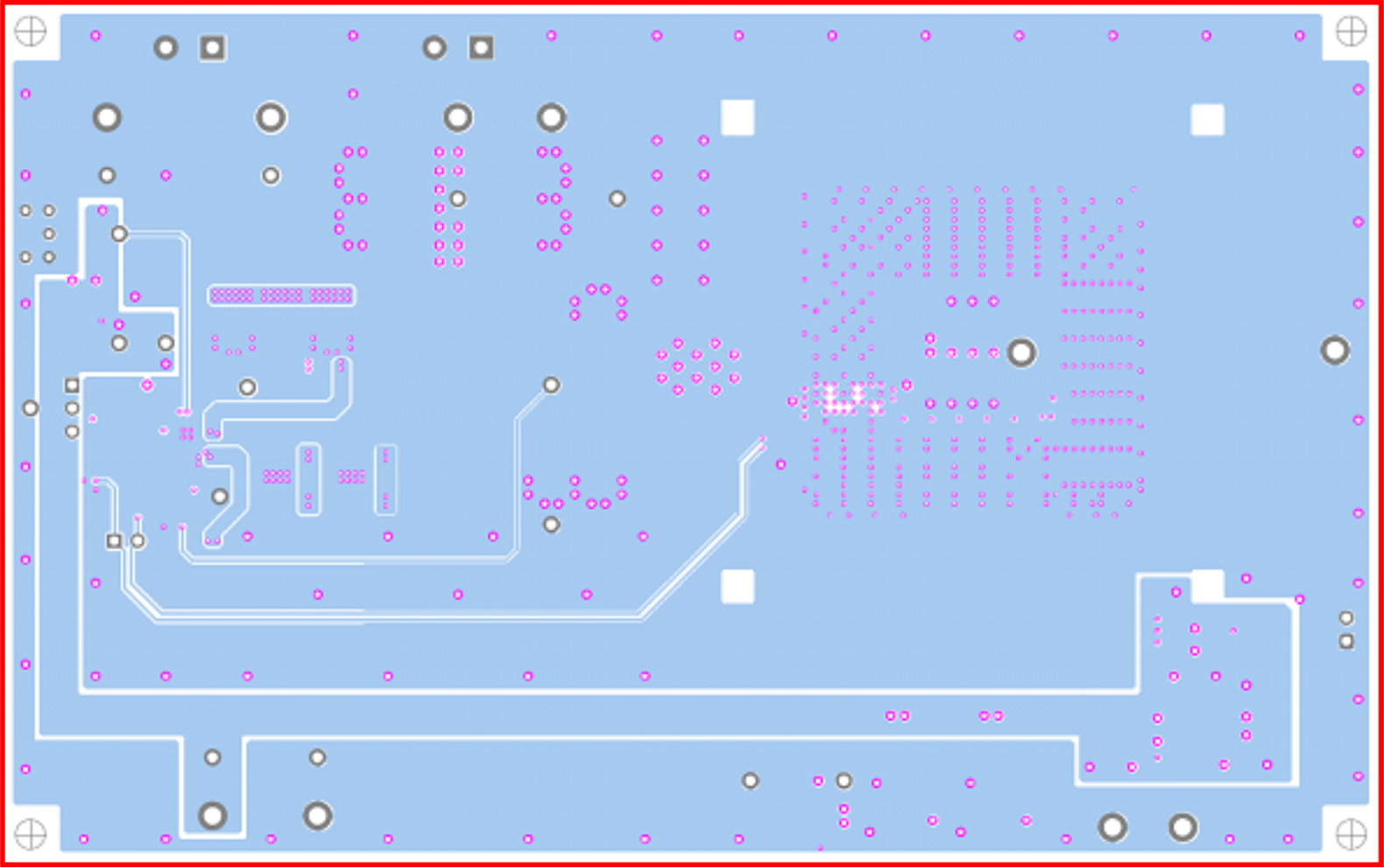

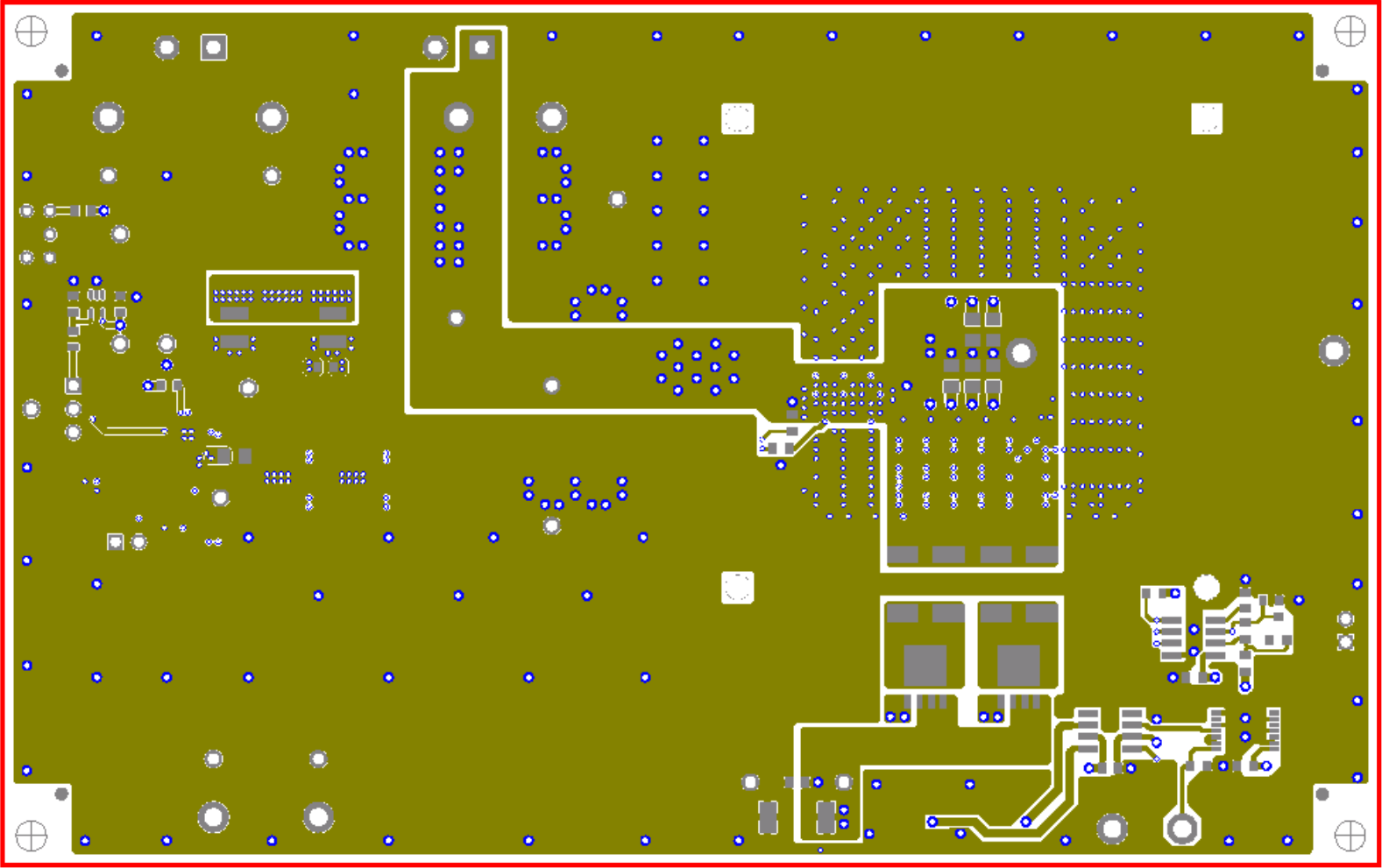

7 EVM Assembly Drawing and PCB Layout

The following figures (Figure 7-2 through Figure 7-6) show the design of the TPS51219EVM-630 printed-circuit board (PCB). The EVM has been designed using four-layer, 2-oz copper circuit board.

Figure 7-1 TPS51219EVM-630 Top Layer Assembly Drawing (Top View)

Figure 7-1 TPS51219EVM-630 Top Layer Assembly Drawing (Top View) Figure 7-2 TPS51219EVM-630 Bottom Layer Assembly Drawing (Bottom View)

Figure 7-2 TPS51219EVM-630 Bottom Layer Assembly Drawing (Bottom View) Figure 7-3 TPS51219EVM-630 Top Copper Layer (Top View)

Figure 7-3 TPS51219EVM-630 Top Copper Layer (Top View) Figure 7-4 TPS51219EVM-630 Internal Layer 1 (Top View)

Figure 7-4 TPS51219EVM-630 Internal Layer 1 (Top View) Figure 7-5 TPS51219EVM-630 Internal Layer 2 (Top View)

Figure 7-5 TPS51219EVM-630 Internal Layer 2 (Top View) Figure 7-6 TPS51219EVM-630 Bottom Copper Layer (Top View)

Figure 7-6 TPS51219EVM-630 Bottom Copper Layer (Top View)