SPRACV1B February 2022 – January 2024 AM2434 , AM6411 , AM6412 , AM6421 , AM6441 , AM6442

4.4.1 Test Setup

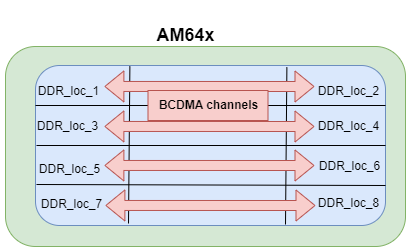

This section describes test setup used for benchamrking performed for DDR to DDR copy using UDMA.

Figure 4-5 AM64x DDR to DDR Data

Flow

Figure 4-5 AM64x DDR to DDR Data

FlowFor example:

DDR_loc_1 = 0xA0000000 + 0x00000000U

DDR_loc_2 = 0xA0000000 + 0x01000000U

DDR_loc_3 = 0xA0000000 + 0x02000000U

DDR_loc_4 = 0xA0000000 + 0x03000000U

And so on.