SPRACV1B February 2022 – January 2024 AM2434 , AM6411 , AM6412 , AM6421 , AM6441 , AM6442

4.3.2 Result and Observation

This section summarized the results and observation of test performed.

| (Bytes) |

|

||||

|---|---|---|---|---|---|

| 1 BCDMA Channel | 2 BCDMA Channels | 4 BCDMA Channels | 8 BCDMA Channels | 16 BCDMA Channels | |

| 1 | 0.89 | 1.6 | 2.29 | 2.67 | 2.61 |

| 2 | 3.2 | 4.57 | 7.11 | 6.4 | 6.4 |

| 4 | 6.4 | 9.14 | 14.2 | 12.8 | 13.13 |

| 8 | 12.8 | 21.33 | 23.27 | 26.95 | 26.95 |

| 16 | 32 | 42.67 | 56.89 | 51.2 | 53.89 |

| 32 | 51.2 | 85.33 | 102.4 | 102.4 | 105.02 |

| 64 | 102.4 | 17.67 | 204.8 | 204.8 | 210.05 |

| 128 | 204.8 | 341.33 | 455.11 | 409.6 | 420.10 |

| 256 | 292.57 | 512 | 682.67 | 963.76 | 862.31 |

| 512 | 455.11 | 744.72 | 1170.28 | 1489.45 | 1560.38 |

| 1024 | 585.14 | 1092.26 | 1489.45 | 1771.24 | 1820.44 |

| 2048 | 712.35 | 1310.72 | 1872.46 | 2048 | 2131.25 |

| 4096 | 780.19 | 1456.35 | 2048 | 2148.72 | 2166.48 |

| 8192 | 840.20 | 1618.17 | 2202.89 | 2240.55 | 2202.89 |

| 16384 | 856.68 | 1638.4 | 2259.86 | 2289.47 | 2205.21 |

| 32768 | 868.03 | 1664.40 | 2309.64 | 2314.73 | 2208.69 |

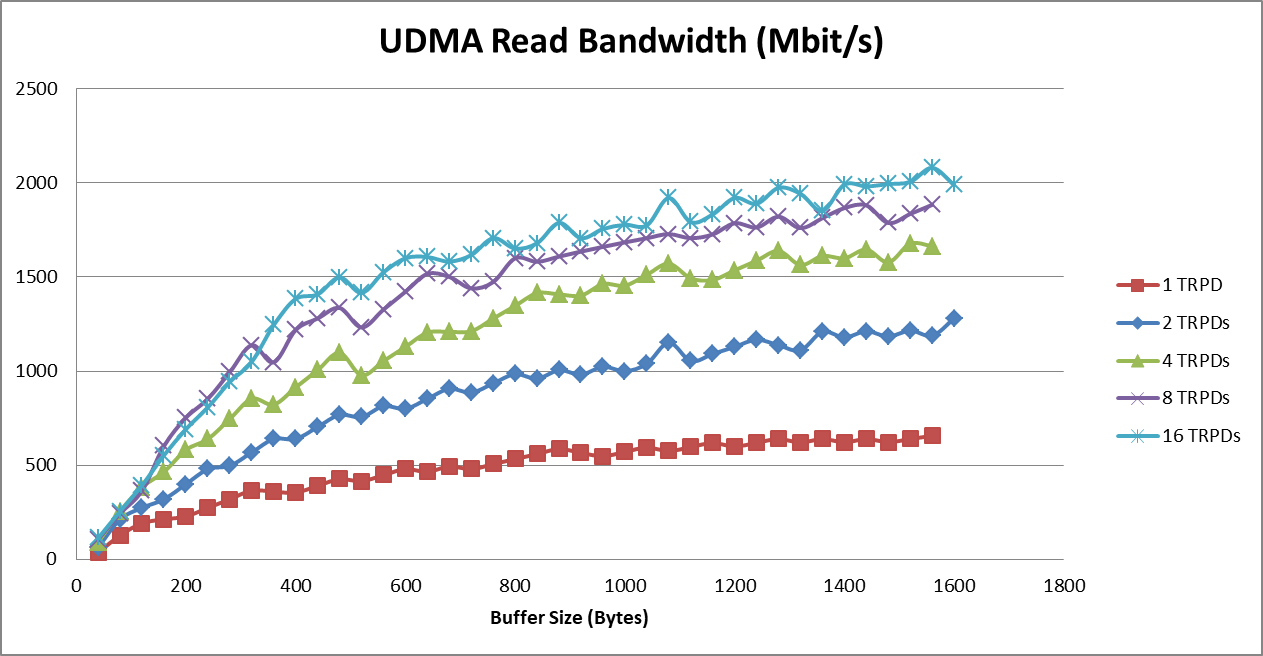

Figure 4-4 shows the PCIE to DDR read performance curve using BCDMA channels. Here, 1 BCDAM channel is being referred to as 1 TRPD. Data shown here range from 40B to 1600B for clear visualization purpose.

Figure 4-4 PCIE Performance Graph

Figure 4-4 PCIE Performance GraphObservation:

Maximum throughput is achieved with four parallel DMA transfers, further adding of channels will work but will not increase throughput.