SPRADG4A January 2024 – April 2024

- 1

- Abstract

- Trademarks

- 1General Texas Instruments High Voltage Evaluation (TI HV EVM) User Safety Guidelines

- 2Introduction

- 3System Description

- 4System Overview

- 5Hardware

-

6Software

- 6.1 Getting Started With Firmware

- 6.2 SysConfig Setup

- 6.3 Incremental Builds

- 7Testing and Results

- 8References

- 9Revision History

6.2.2 ADC Configuration

Four ADC instances have been used in this demonstration to sense all voltages, currents on the HV and LV dc bus side. PSFB_HVBUS_ADC_MODULE, PSFB_LVBUS_ADC_MODULE, PSFB_IHV_FILT_ADC_MODULE, PSFB_ILV_ADC_MODULE are assigned to the signals mentioned in Key Signal Connections. Rest of the required ADC related configurations are done in PSFB_HAL_setupADC() and PSFB_HAL_setupADCSoC() inside main().

The ADC HSEC Board Pin out is different for E1 and E2 versions of the AM263x controlCARD, which is mentioned in Table 6-1.

| HSEC Board | E1 | E2 |

|---|---|---|

| 12 | ADC0_AIN0 | ADC1_AIN0 |

| 14 | ADC0_AIN1 | ADC1_AIN1 |

| 15 | ADC0_AIN2 | ADC0_AIN2 |

| 18 | ADC1_AIN0 | ADC1_AIN2 |

| 20 | ADC1_AIN1 | ADC1_AIN3 |

| 21 | ADC1_AIN2 | ADC0_AIN4 |

| 23 | ADC1_AIN3 | ADC0_AIN5 |

| 28 | ADC2_AIN2 | ADC3_AIN0 |

| 30 | ADC2_AIN3 | ADC3_AIN1 |

| 31 | ADC3_AIN0 | ADC2_AIN0 |

| 33 | ADC3_AIN1 | ADC2_AIN1 |

| 34 | ADC3_AIN2 | ADC3_AIN2 |

| 37 | ADC4_AIN0 | ADC2_AIN2 |

| 39 | ADC4_AIN3 | ADC2_AIN3 |

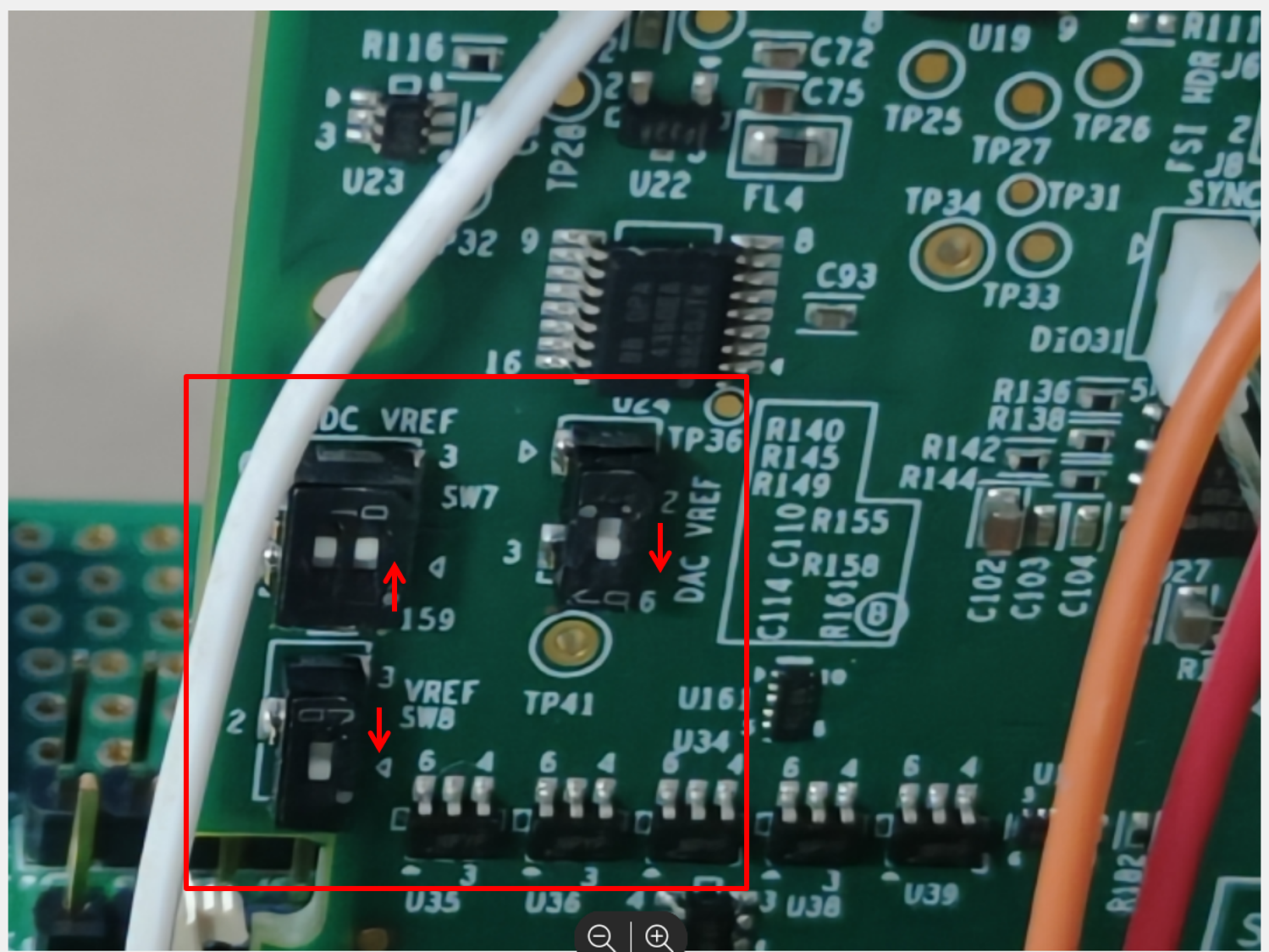

Set the ADC DAC reference voltage switches according to application requirements by checking in the respective board schematics document in the section - ADC and DAC Interfaces.

Figure 6-4 ADC and DAC Reference Switches

in the AM263x controlCARD

Figure 6-4 ADC and DAC Reference Switches

in the AM263x controlCARD