SPRADG4A January 2024 – April 2024

- 1

- Abstract

- Trademarks

- 1General Texas Instruments High Voltage Evaluation (TI HV EVM) User Safety Guidelines

- 2Introduction

- 3System Description

- 4System Overview

- 5Hardware

-

6Software

- 6.1 Getting Started With Firmware

- 6.2 SysConfig Setup

- 6.3 Incremental Builds

- 7Testing and Results

- 8References

- 9Revision History

5.1 Hardware Overview

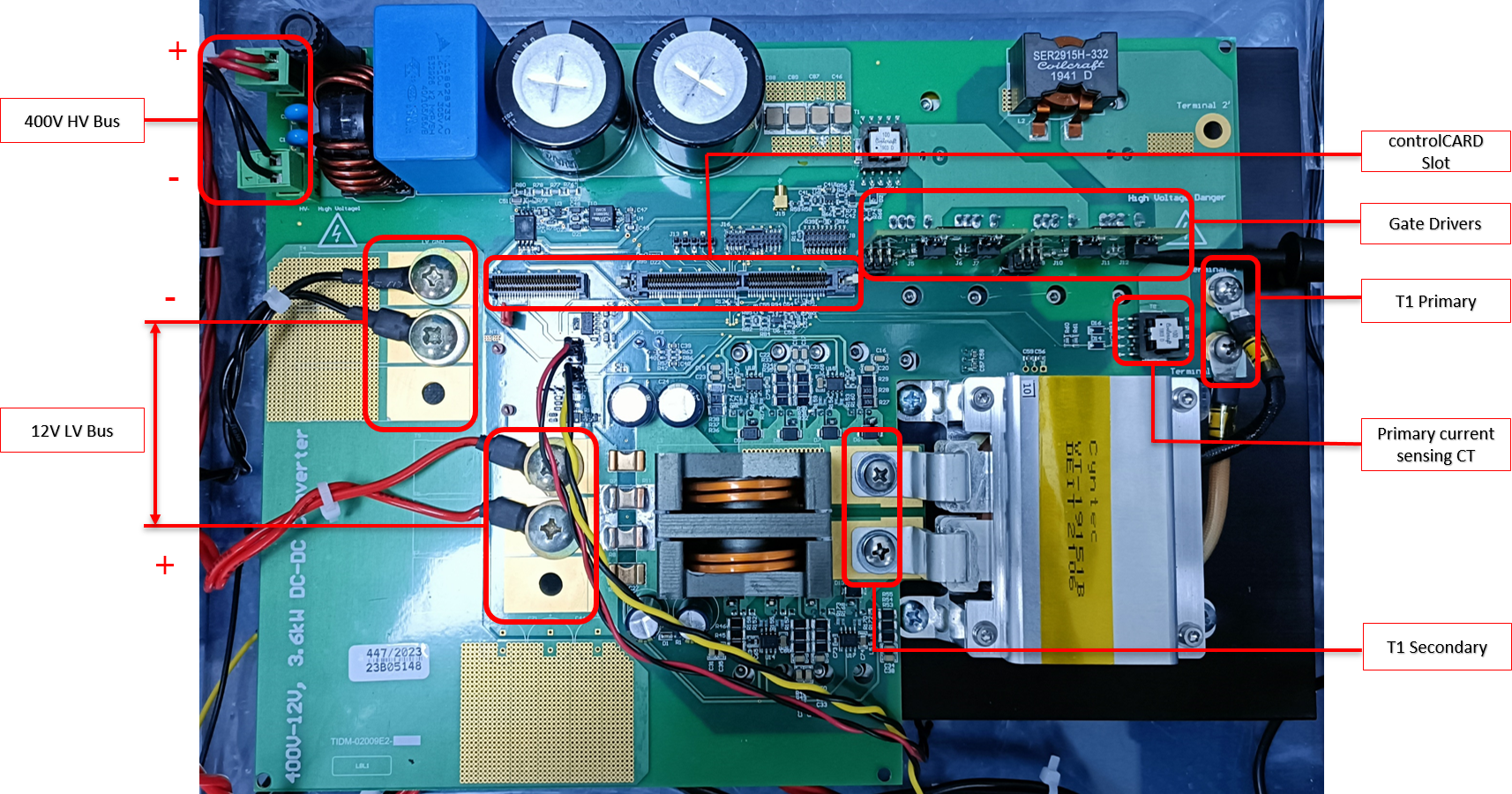

TIDM-02009 PSFB Converter Hardware shows key hardware components. This hardware uses the kit of Bidirectional 400V/12V DC/DC converter reference design as the base board and with some modification for peak current mode control.

Figure 5-1 TIDM-02009 PSFB Converter Hardware

Figure 5-1 TIDM-02009 PSFB Converter HardwareThe key signal connections between the controlCARD and the base board are listed in the Key Signal Connections. The HSEC pin number is based on the E2 version of the AM263x controlCARD (TMDSCNCD263).

| Signal Name | Description | Connection to ControlCARD | HSEC Pin Number |

|---|---|---|---|

| ePWM-4A | PWM drive for full-bridge switch Q1 | EPWM4_A | 57 |

| ePWM-4B | PWM drive for full-bridge switch Q4 | EPWM4_B | 59 |

| ePWM-3A | PWM drive for full-bridge switch Q2 | EPWM3_A | 54 |

| ePWM-3B | PWM drive for full-bridge switch Q3 | EPWM3_B | 56 |

| ePWM-5A | PWM drive for sync rectifier/push-pull switch Q5 | EPWM5_A | 61 |

| ePWM-5B | PWM drive for sync-rectifier/push-pull switch Q6 | EPWM5_B | 63 |

| VLV-FB | Low voltage bus – voltage feedback | ADC3_AIN2 | 34 |

| ILV-FILT | Heavily filtered low voltage current feedback | ADC1_AIN2 | 18 |

| VHV-FB | High voltage bus – voltage feedback | ADC3_AIN1 | 30 |

| IHV-FILT | Heavily filtered transformer high voltage winding current | ADC4_AIN0 /ADC_CAL0 | 25 |

While running the hardware, pin #1 and #2 of J19 in the base board must be shorted with a jumper. 12V power supply must be applied in between pin #9 and#7 of J17 connector only if gating pulses for the Q5, Q6 are to be enabled.