SPRUIS4E March 2022 – January 2024

- 1

- Jacinto7 J721E/DRA829/TDA4VM Evaluation Module (EVM)

- Trademarks

- 1Introduction

- 2J721E EVM Overview

- 3EVM User Setup/Configuration

-

4J721E EVM Hardware Architecture

- 4.1 J721E EVM Hardware Top level Diagram

- 4.2 J721E EVM Interface Mapping

- 4.3 I2C Address Mapping

- 4.4 GPIO Mapping

- 4.5 Power Supply

- 4.6 Reset

- 4.7 Clock

- 4.8 Memory Interfaces

- 4.9 MCU Ethernet Interface

- 4.10 QSGMII Ethernet Interface

- 4.11 PCIe Interface

- 4.12 USB Interface

- 4.13 CAN Interface

- 4.14 FPD Interface (Audio Deserializer)

- 4.15 FPD Panel Interface (DSI Video Serializer)

- 4.16 Display Serial Interface (DSI) FPC

- 4.17 Audio Interface

- 4.18 Display Port Interface

- 4.19 MLB Interface

- 4.20 I3C Interface

- 4.21 ADC Interface

- 4.22 RTC Interface

- 4.23 Apple Authentication Header

- 4.24 EVM Expansion Connectors

- 4.25 ENET Expansion Connector

- 4.26 CSI Expansion Connector

- 5Revision History

4.5 Power Supply

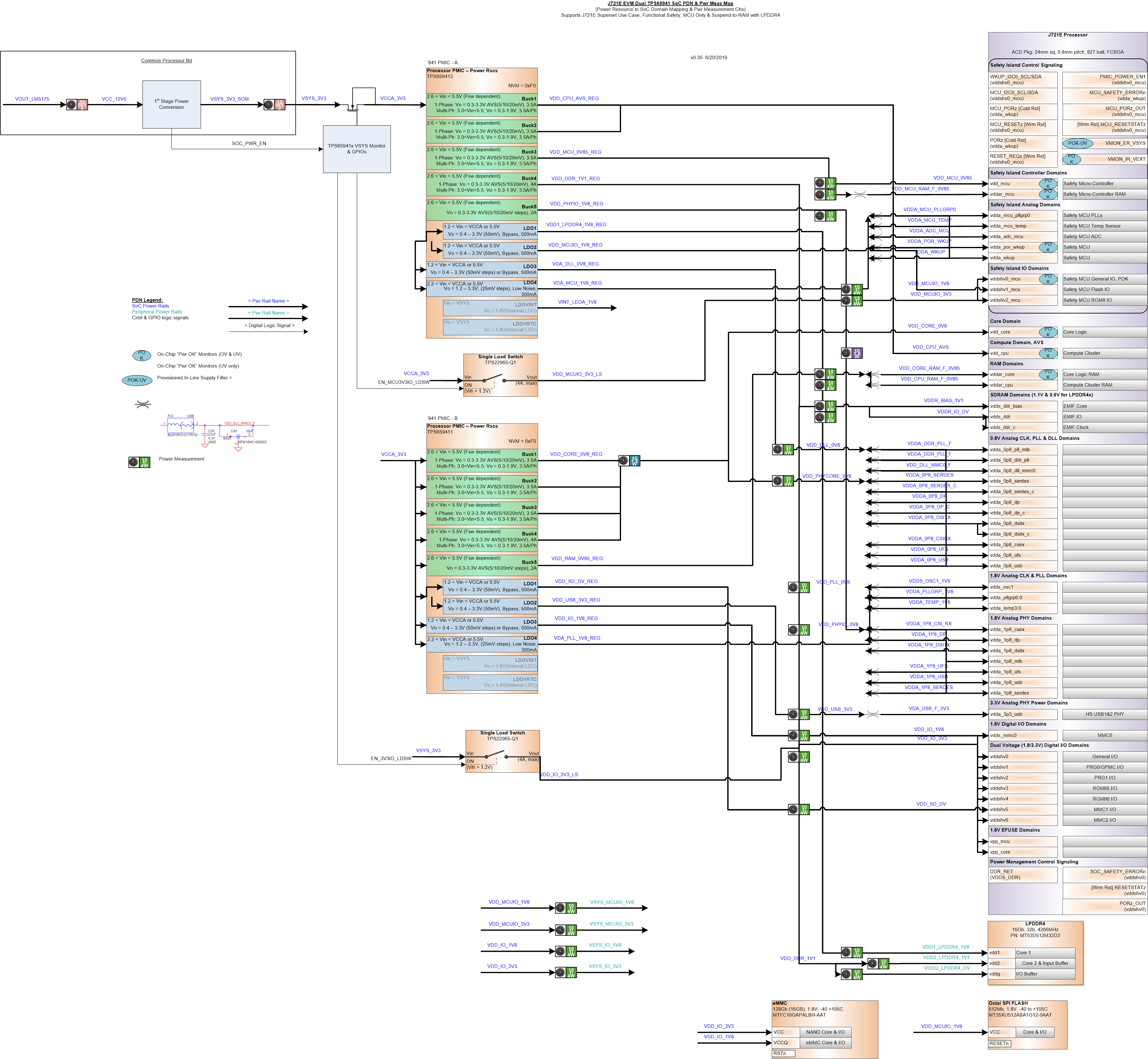

Figure 4-3 shows the SoM’s power distribution system. The Power to the SoM is derived from the Dual Buck converter 12 V to 5.0 V / 3.3 V on the Common Processor Board. The J721E processor is powered from a dual TPS6594x PMIC solution, which is optimized for the J721E to support a wide variety of use cases.

Dual load switch TPS22976-Q1 provides the switching option for the LPDDR4 I/O power supply (1.1 V / 0.6 V).

Figure 4-3 J721E SOM Power Distribution Block Diagram

Figure 4-3 J721E SOM Power Distribution Block Diagram