TIDT226 April 2021

4.1 Start-up Sequence

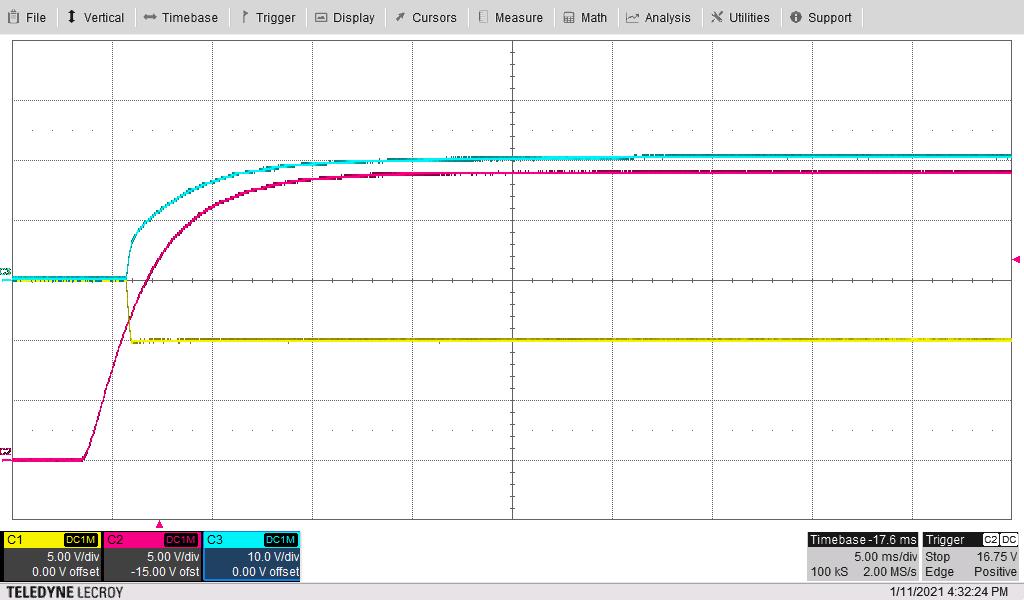

The following waveform shows the output voltage start-up waveform (20 V in Blue and –4 V in Yellow) after the application of 24-V input (Red) with each output loaded to 0 mA.

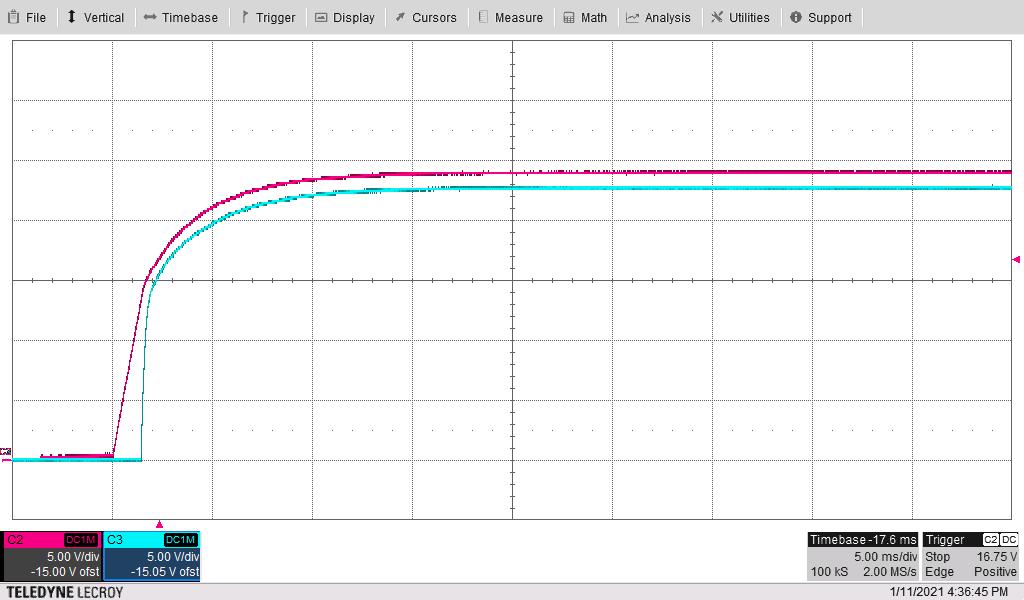

The following waveform shows the output voltage start-up waveform (+20 V in Blue and –4 V in Yellow) after the application of 24-V input (Red) with each output loaded to 100 mA.

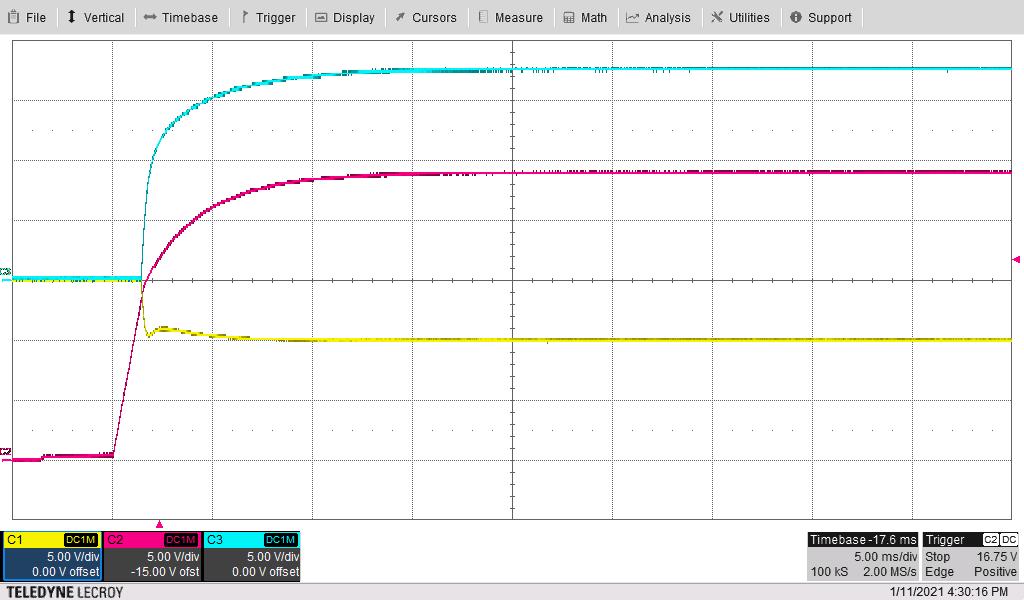

The following waveform shows the total rectified secondary output voltage start-up waveform (Blue) after the application of 24-V input (Red) with each output loaded to 0 mA.

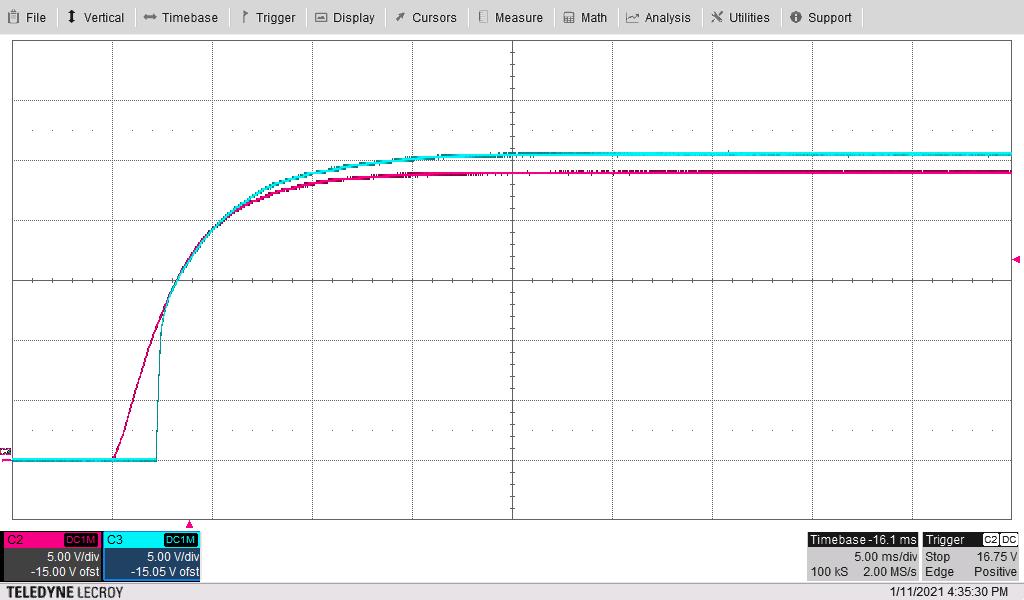

The following waveform shows the total rectified secondary output voltage start-up waveform (Blue) after the application of 24-V input (Red) with each output loaded to 100 mA.