KOKT046 February 2024 UCC12051-Q1

역사적으로 차량용 전자 장치는 시동을 거는 데 사용되는 12V 납산 배터리로 전원을 공급받아왔습니다. 발전기가 작동 중이고 배터리 케이블이 분리되었을 때 발생할 수 있는 최대 42V의 서지에서도 전압이 60VDC미만의 안전 추가 저전압(SELV) 범위에서 유지됩니다. 따라서 차량용 회로에서 전기 충격 위험을 피하기 위해 PCB(인쇄 회로 보드) 트레이스의 간격에 대해 걱정할 필요가 없었습니다.

전기 자동차(EV) 모터가 작동하려면 더 높은 전압(400V 또는 800V)이 필요하기 때문에 이제 차량용 애플리케이션에서 감전 위험이 걱정됩니다. AC 주전원에 연결된 회로와 유틸리티 전원으로 구동되는 SELV 회로 사이의 경계에 적용되는 것과 동일한 엄격한 간격이 이제 전기차의 고전압 배터리에 연결된 회로와 인포테인먼트 및 차체 전자 장치(주로 조명)와 같은 12V 시스템에서 구동되는 SELV 회로 사이의 경계에도 적용됩니다.

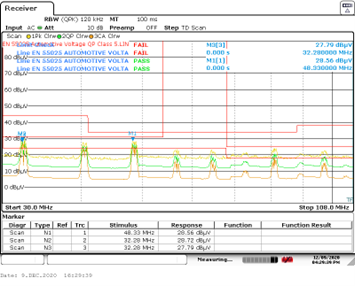

CISPR 25 고장

고전압 EV 배터리를 통해 작동하는 트랙션 인버터에서 고전력 반도체 스위치를 구동하는 데 필요한 많은 바이어스 전원 공급 장치는 저전압 12V 시스템에서 전원을 공급받습니다. 문제는 이러한 절연 전원 공급 장치가 많은 공통 모드 잡음을 12V 자동차 배터리 라인으로 다시 펌핑하여 108MHz까지 확장되는 자동차 CISPR(국제 전파 간섭 위원회) 25 전도성 방출 제한을 위반한다는 점입니다. 이 잡음은 주로 바이어스 공급의 절연 변압기의 1차 권선과 2차 권선 사이에 정전식으로 커플링되는 메인 스위칭 파형에 의해 발생합니다. 1차 접지와 2차 접지 사이에 서지 전압 정격이 높은 바이패스 커패시터(Y-커패시터)가 작은 루프를 생성하여 이 공통 모드 잡음을 대부분 억제하고 배터리 라인의 공통 모드 필터링이 이 잡음을 더욱 줄여 CISPR 25 제한을 통과할 수 있도록 합니다.

차량용 회로의 간격 요구 사항

고전압 전기차 배터리와 대부분의 기존 차량용 회로에 사용되는 저전압 12V 배터리 시스템 사이의 간격을 강화하기 위해 일반적으로 8mm의 간격을 목표로 합니다. 이는 400VRMS, 오염도 2 및 재료 그룹 III 또는 800VRMS 오염도 2는 동일하지만 재료 그룹 I에 적용됩니다. 간격 요구 사항에 대한 자세한 내용은 국제전기기술위원회(IEC) 60664-1 표준인 "저전압 공급 시스템 내 장비의 절연 조정 1부": 원칙, 요구 사항 및 테스트" 를 참조하십시오.

다중 계층 PCB의 연면 및 클리어런스 요구 사항 충족

IEC의 엄격한 간격 요구 사항은 오염된 공기에 노출된 표면의 고전압 고장(연면거리)과 공기 자체의 고장 또는 아크(클리어런스)로 인해 발생합니다. 변압기나 집적 회로(IC)와 같은 1차-2차 장벽을 연결하는 부품 내부와 공기 또는 수분 노출이 없는 다층 PCB의 내부 레이어를 연결하는 구성 요소 내에서, 장벽이 수 킬로볼트 고전위 테스트를 견딜 수 있는 한 간격 요구 사항이 훨씬 적습니다. 강화 장벽 애플리케이션에 사용되는 IC의 일반적인 테스트 레벨은 5kV로, 4개 이상의 레이어가 있는 PCB가 내부 레이어에 1차 및 2차 접지를 인터리브할 수 있습니다. 내부 레이어 내에는 간격 요구 사항이 있지만 공기에 노출된 레이어에 대한 요구 사항보다 크게 줄어듭니다. 일부 애플리케이션의 경우 800V 배터리 시스템에서는 1mm 간격이면 충분할 수 있습니다.

절연 DC/DC 컨버터를 사용한 데모

UCC12051-Q1 절연 DC/DC 컨버터의 CISPR 25 클래스 5 제한 대비 방출 성능을 입증하기 위해 두 개의 보드를 제작했습니다. 이 컨버터는 일반적인 배터리 라인 전자기 간섭 필터를 사용하여 100mA로 로드되는 5V 입력 및 5V 출력용으로 설계되었습니다. 한 보드(미공개)는 4개의 레이어 모두에서 1차측과 2차측 간 간격이 8mm였고, 한 보드(차량용 CISPR 25, 클래스 5 방출, 레퍼런스 디자인용 절연 5V 바이어스 공급 장치)는 2개의 내부 레이어에서 1차측과 2차측 접지를 인터리빙할 수 있으며 1차측과 2차측 접지 간 간격이 1mm였습니다. 1차 접지부터 2차 접지까지의 추가 유효 커패시턴스는 약 11pF였습니다. UCC12051-Q1 내부의 절연 컨버터는 CISPR 25 문제의 첫 번째 주파수가 32MHz에서 네 번째 고조파가 되도록 8MHz에서 스위칭합니다.

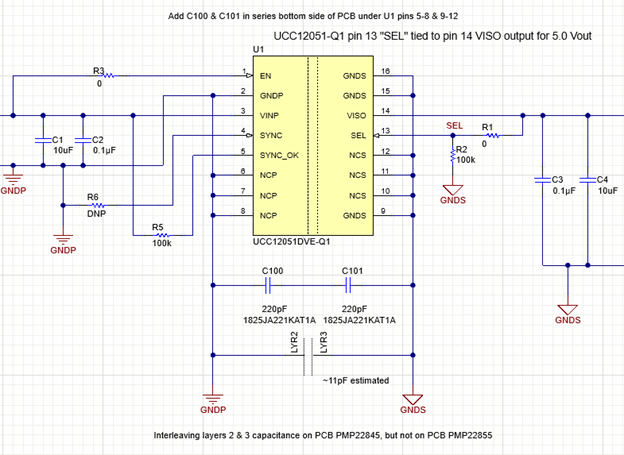

그림 1은 1차 접지에서 2차 접지까지 커패시터가 있는 IC 절연 컨버터를 보여주는 절연된 5V 레퍼런스 설계 회로도의 스니펫으로, 컨버터의 절연 변압기에 의해 생성되는 고주파 잡음을 포함합니다. 미출시 보드는 PCB 레이어 인터리빙이 없다는 것을 제외하고 절연 5V 레퍼런스 설계와 동일합니다.

그림 1 바이패스 커패시터 C100과 C101 및 인터리빙 내부 레이어 커패시턴스를 보여주는 절연 5V 레퍼런스 설계에서 DC/DC 컨버터의 1차 및 2차 인터페이스. 출처: 텍사스 인스트루먼트

그림 1 바이패스 커패시터 C100과 C101 및 인터리빙 내부 레이어 커패시턴스를 보여주는 절연 5V 레퍼런스 설계에서 DC/DC 컨버터의 1차 및 2차 인터페이스. 출처: 텍사스 인스트루먼트안전을 위한 이중화가 필요하고 1차부터 2차까지 전체 간격을 유지해야 하기 때문에 1차 및 2차 접지를 직렬로 배치해 2개의 Y 커패시터(C100과 C101)를 배치했습니다. 따라서 유효 커패시턴스는 각 커패시터의 값의 절반입니다. 경우에 따라 필요한 간격을 유지하기 위해 3개의 병렬 커패시터(330pF 커패시터)가 필요합니다.

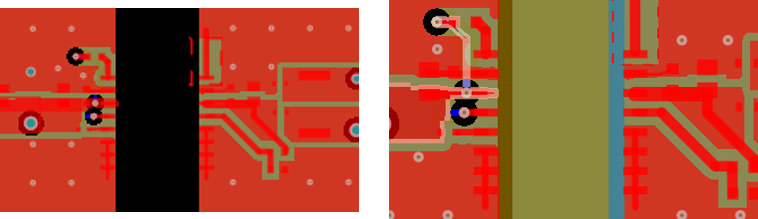

그림 2에서 왼쪽 이미지는 모든 레이어에 대해 8mm 간격으로 릴리스되지 않은 보드입니다. 오른쪽 이미지는 8mm의 간격과 내부 레이어가 1mm 간격인 절연 5V 레퍼런스 설계이며, 1차 접지면과 2차 접지면이 겹치는 것을 허용합니다.

그림 2 모든 레이어의 8mm 간격(왼쪽)과 상단 및 하단 레이어에서만 8mm 간격(오른쪽): 상단 레이어는 빨간색이고, 레이어 2는 어두운 녹색, 레이어 3은 밝은 파랑, 레이어 4는 황갈색, 레이어 2와 3의 겹치는 부분은 밝은 녹색, 어떤 레이어의 구리도 검정색이 아닙니다. 출처: 텍사스 인스트루먼트

그림 2 모든 레이어의 8mm 간격(왼쪽)과 상단 및 하단 레이어에서만 8mm 간격(오른쪽): 상단 레이어는 빨간색이고, 레이어 2는 어두운 녹색, 레이어 3은 밝은 파랑, 레이어 4는 황갈색, 레이어 2와 3의 겹치는 부분은 밝은 녹색, 어떤 레이어의 구리도 검정색이 아닙니다. 출처: 텍사스 인스트루먼트방사 방출량과 CISPR 25 비교

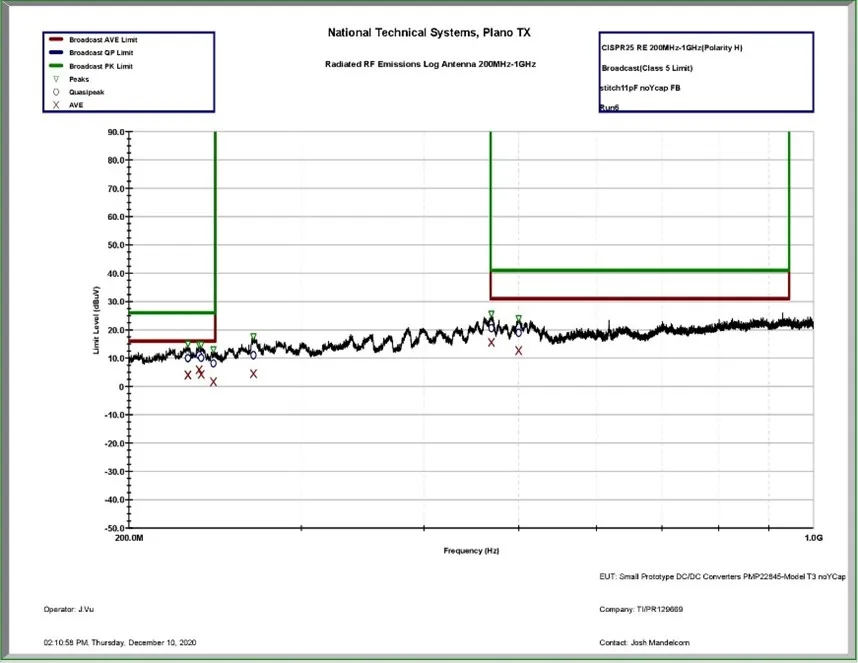

절연 5V 레퍼런스 설계를 통해 1차와 2차 접지 사이에 11pF의 커패시턴스가 추가되어 200MHz 이상의 방사 방출에만 도움이 될 것으로 예상했습니다. 그리고 실제로 인터리빙 레이어는 바이패스 커패시터 C100과 C101(그림 3)이 없어도 200MHz를 초과하는 모든 주파수에 대해 방사 방출이 CISPR 25 클래스 5를 통과할 수 있도록했습니다. 인터리빙 레이어가 없어도 동일한 주파수 범위를 통과하기 위해 1차와 2차 접지 사이에 추가 Y 커패시터가 필요했습니다. 배출 테스트 설정에 대한 테스트 보고서를 참조하십시오.

그림 3 추가 Y 커패시터 없이 200MHz보다 높은 CISPR 25 클래스 5의 방사 방출 비교. 이 특정 스캔은 절연된 5V 레퍼런스 설계 테스트 보고서에 없습니다. 보드는 10dB 이상의 여유로 한계를 통과했습니다. 출처: 텍사스 인스트루먼트

그림 3 추가 Y 커패시터 없이 200MHz보다 높은 CISPR 25 클래스 5의 방사 방출 비교. 이 특정 스캔은 절연된 5V 레퍼런스 설계 테스트 보고서에 없습니다. 보드는 10dB 이상의 여유로 한계를 통과했습니다. 출처: 텍사스 인스트루먼트놀라운 사실은 엄격한 전도 방출 제한을 사용하여 30 ~ 108MHz 범위의 필터링(C101 및 C102)이 크게 향상된다는 것이었습니다. 1차 접지와 2차 접지 사이에 110pF의 유효 추가 커패시턴스를 사용하여 인터리빙은 전체 30~108MHz 범위에서 약 4~8dB까지 전도 잡음을 감소시켰습니다. 이 주파수 범위에서 인터리빙은 4dB의 실패를 4dB의 여유를 두고 통과로 변환했습니다.

전도성 배출과 CISPR 25 비교

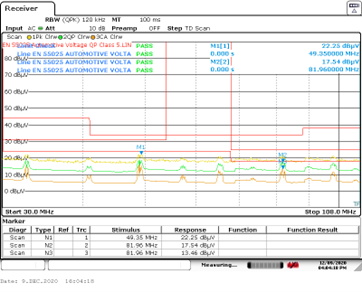

그림 4 및 그림 5은 이 두 보드의 전도 방출 스캔을 보여 주며, 유일한 차이점은 내부 레이어 인터리빙입니다. 두 스캔 모두 동일한 라인 임피던스 안정화 네트워크(LISN)에 있었습니다. 동일한 공통 모드 배터리 라인 필터링과 5V 출력에서 100mA의 부하가 있었습니다.

그림 4 절연 5V 레퍼런스 설계(인터리빙 레이어 포함) 전도성 방출 대비 CISPR 25 클래스 5, 30~108MHz: 4.5dB 마진으로 통과했으며, 최악의 경우 82MHz에서 "CISPR 평균" 검출이 발생했습니다. 출처: 텍사스 인스트루먼트

그림 4 절연 5V 레퍼런스 설계(인터리빙 레이어 포함) 전도성 방출 대비 CISPR 25 클래스 5, 30~108MHz: 4.5dB 마진으로 통과했으며, 최악의 경우 82MHz에서 "CISPR 평균" 검출이 발생했습니다. 출처: 텍사스 인스트루먼트 그림 5 미출시 보드(인터리빙 레이어 없음) 전도성 방출 대비 CISPR 25 클래스 5, 30~108MHz: 3.8dB의 마진으로 실패했으며, 최악의 경우 32MHz에서 CISPR 평균 검출이 발생했습니다. 출처: 텍사스 인스트루먼트

그림 5 미출시 보드(인터리빙 레이어 없음) 전도성 방출 대비 CISPR 25 클래스 5, 30~108MHz: 3.8dB의 마진으로 실패했으며, 최악의 경우 32MHz에서 CISPR 평균 검출이 발생했습니다. 출처: 텍사스 인스트루먼트약 11pF의 커패시턴스를 가진 인터리빙 레이어는 Y-커패시터의 유효 커패시턴스 110pF에 11pF를 추가하는 것보다 필터링에 훨씬 더 많이 기여하여 필터링을 약 1dB 개선할 수 있습니다. 내부 레이어 접지면은 브리징 Y-커패시터의 유효 인덕턴스를 줄이고 이러한 고주파 고조파를 더 잘 션트할 수 있도록 합니다.

이러한 필터링 개선은 인접 접지면의 이점을 더해, 출력 잡음을 제한하고, 비절연 애플리케이션에서 방출을 제어하거나 반도체의 응력과 오류를 줄이는 것이 목표인지 여부와 관계없이 커패시터 필터링의 성능을 향상시킵니다.

관련 콘텐츠

추가 리소스

- PCB 연면거리 계산기를 사용하여 강화된 절연 이중 결과를 확인하세요.

- 텍사스 인스트루먼트에서 자세히 보기: