SBAS569B May 2013 – February 2019 ADS8860

PRODUCTION DATA.

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

- 9 Detailed Description

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

11.2 Power Saving

The device has an auto power-down feature that powers down the internal circuitry at the end of every conversion. Referring to Figure 67, the input signal is acquired on the sampling capacitors when the device is in a power-down state (tacq); at the same time, the result for the previous conversion is available for reading. The device powers up on the start of the next conversion. During conversion phase (tconv), the device also consumes current from the reference source (connected to the REF pin).

Figure 67. Power Scaling With Throughput

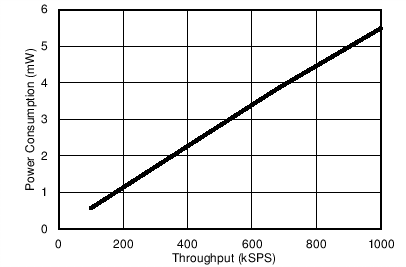

Figure 67. Power Scaling With Throughput The conversion time, tconv, is independent of the SCLK frequency. When operating the device at speeds lower than the maximum rated throughput, the conversion time, tconv, does not change; the device spends more time in power-down state. Therefore, as shown in Figure 68, the device power consumption from the AVDD supply and the external reference source is directly proportional to the speed of operation. Extremely low AVDD power-down current (50 nA, typical) and extremely low external reference leakage current (250 nA, typical), make this device ideal for very low throughput applications (such as pulsed measurements).

Figure 68. Power Scaling With Throughput

Figure 68. Power Scaling With Throughput