SLLU380 March 2024 THVD4411

2.2 Board Setup and Operation

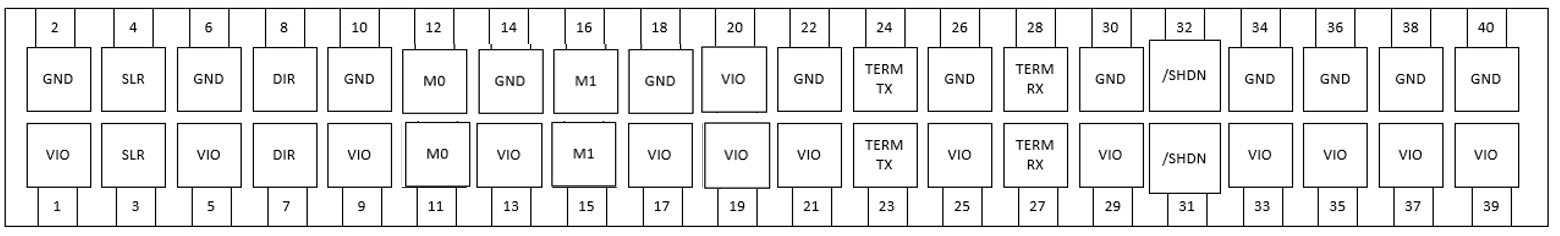

After the power supply of the THVD4411EVM has been configured, set up the board for operation. Before any operation of the board can occur, the operational mode and control pins must be configured. The map to the J15 header pins is shown below.

Figure 2-1 J15 Pinout

Figure 2-1 J15 PinoutAssume that the board is oriented with J1 in the top left of the EVM. The numbered boxes correspond to the pin number for J15 as indicated in the schematic.

To select a configuration option, find the signal of interest on J15, according to Figure 4-1. If a low value is wanted, then shunt the top row header pin connected to the signal of interest to the pin on the left. If a high value is wanted, then shunt the bottom row header pin connected to the signal of interest to the pin on the left. Next, the mode of operation must be determined. The operational mode is controlled by the M0 and M1 connected to U1 via J15-11/12 and J15-15/16, respectively.

| M1 (J15-15; J5-16) | M0 (J15-11; J5-12) | Mode | Comment |

|---|---|---|---|

| 0 | 0 | Reserved | Unused |

| 0 | 1 | RS-232 | 1T1R mode; L2 is logic input for RS232 driver; L1 is logic output. |

| 1 | 0 | Half Duplex RS-485 | L1 is logic input, L2 is logic output; RS-485 on R1 and R2. |

| 1 | 1 | RS-485 Full Duplex | L1 is logic input, L2 is logic output; RS-485 TX is R1 and R2 while RX is R3 and R4. |

After the mode has been selected, the other features and control signals can be configured or connected to a signal source for the DIR and /SHDN signals.

| Signal | Signal Jumper and Pin ID | Associated GND Pin | Logic ‘0’ Operation | Associated VIO Pin | Logic ‘1’ Operation |

|---|---|---|---|---|---|

|

SLR |

J15-3; J15-4 |

J15-2 |

RS485: 20Mbps RS232: 1Mbps |

J15-1 |

RS485: 500kbps RS232: 250kbps |

|

DIR |

J15-7; J15-8 |

J15-6 |

RS485: RX mode |

J15-5 |

RS485: TX mode |

|

TERM_TX |

J15-23; J15-24 |

J15-22 |

RS485 TX: unterminated |

J15-21 |

RS485 TX: terminated with 120Ω |

|

TERM_RX |

J15-27; J15-28 |

J15-26 |

RS485 RX: unterminated |

J15-25 |

RS485 RX: terminated with 120Ω |

|

/SHDN |

J15-31; J15-32 |

J15-30 |

Device in shutdown mode |

J15-29 |

Device operational |

The mode pins along with the TERM_TX and TERM_RX pins must be configured before communication starts as opposed to changing during communication for proper operation.

All the various modes of the THVD4411 share the use of the logic pins (denoted with the prefix “L”) and the bus pins (denoted with the prefix “R”).

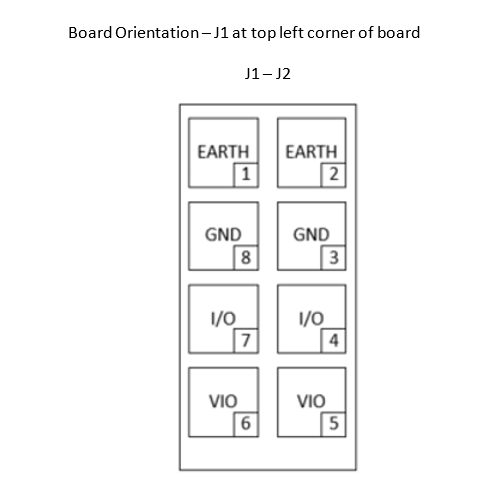

Logic pins are for use when interfacing the THVD4411 with a controller. The logic pins are supplied and bounded by the VIO voltage, meaning that these pins can accept GND to VIO input voltages and can output GND to VIO voltages. All logic pins L1 – L2 are accessible through 4x2 headers J5-J6 that populate the left side of the board when the board is oriented with J1 in the top left corner. Figure 4-2 shows the headers pinouts.

Figure 2-2 U1:LX Header Pinout

Figure 2-2 U1:LX Header PinoutThe function of each individual L pin depends on the mode in which the THVD4411 is being operated in.

Bus pins are the higher voltage tolerant pins for use with RS-485 or RS-232 depending on chosen operation mode. The bus pins are accessible in a few different ways depending on mode of use. Both RS-232 and RS-485 modes have all “R” pin signals routed to an 4x2 header J14. If every row of header J14 is shunted, then all signals R1-R4 are available on the D-SUB connector J18. If headers J12 and J13 are shunted, then R1 and R2 signals are available on terminal block J17. If headers J10 and J11 are shunted, then R3 and R4 signals are available on terminal block J16. A brief summary is given in Table 4-1.

| U1 Pin | Output Option 1 | Output Option 2 | Output Option 3 | Output Option 4 |

|---|---|---|---|---|

|

R1 |

J11, column 1 |

J7 if J11 is shunted |

N/A |

N/A |

|

R2 |

J9, column 1 |

J7 if J9 is shunted |

J14; Row 2, Column 1 |

J10 if J14 Row 2 is Shunted |

|

R3 |

J13, column 1 |

J8 if J13 is shunted |

J14; Row 3, Column 1 |

J10 if J14 Row 3 is Shunted |

|

R4 |

J12, column 1 |

J8 if J12 is shunted |

J16 (if J11 is Shunted) |

J18 (if J14 row 4 is shunted) |

How these pins are connected depends on the chosen operation mode and personal preference of the end user.

RS-232 Operation

With an understanding of the general architecture of the device and EVM, a more thorough look at the RS-232 modes of operation is important. When entering the mode 01 for M1 and M0, respectively, the device enters RS-232 mode.

| Mode | L1 | L2 | R1 | R2 | R3 | R4 |

|---|---|---|---|---|---|---|

| 01 | Console side input | Console side output | Unused | RS-232 bus output | RS-232 bus input | Unused |

This is commonly referred to as a 1T1R setup as there is one transmitter and one receiver. At an individual transceiver level, the type of RS-232 signal being transmitter or received is not important to the transceiver as the PHY layer characteristics are the same, regardless of RS-232 signal type. However, the specific configuration is generally used with the following RS-232 signals: TX and RX. While this configuration of signals is not strictly required, most 1T1R RS-232 applications use these signals and require this configuration and if J10 (the DSUB connector) is used the pinout of the connector mimics the standard placement of the aforementioned RS-232 cables

| U1 Pin | Standard RS-232 Circuit Mnemonic | J18 Pin |

|---|---|---|

| R2 | TX | 3 |

| R3 | RX | 2 |

RS-485 Operation

With RS-232 operational modes covered, this section describes the RS-485 operation modes. There are two different operational modes of the RS-485 portion of the transceiver: half duplex and full duplex.

Half duplex operation is a very common implementation of RS-485 and entered when the mode is 10 for M1 and M0 respectively. In half duplex mode, the receive and transmit bus facing pins (denoted R# on the THVD4411) are shared by the transceiver, allowing for asynchronous bi-directional communication on two wires with the trade-off being that the bus can only have 1 driver at a time and a device cannot receive and transmit data simultaneously.

| Mode | L1 | L2 | R1 | R2 | R3 | R4 |

|---|---|---|---|---|---|---|

| 10 | Console side input | Console side output | Inverting bus facing pin | Non-inverting bus facing pin | Unused | Unused |

The termination resistor shown is disabled by default. In half-duplex mode, TERM_RX is a don’t care value and the integrated termination is only controlled by TERM_TX. Driver input is connected to L1 and the RS-485 console side output is L2.

The next mode of operation is full duplex operation, which is mode 11 for M1 and M0 respectively. This mode of operation separates the driver and receiver of the RS-485 transceiver, which leads to a 4-signal wire interface.

| Mode | L1 | L2 | R1 | R2 | R3 | R4 |

|---|---|---|---|---|---|---|

|

10 |

Console side input |

Console side output |

Inverting bus facing driver |

Non-inverting bus facing driver |

Non-inverting bus facing receiver |

Inverting bus facing receiver |

The termination resistor shown is disabled by default. In full-duplex mode, TERM_TX and TERM_RX control both the RX and TX path integrated termination resistors.