SLVSEO1A August 2021 – May 2022 ADC08DJ5200RF

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Thermal Information

- 6.5 Electrical Characteristics: DC Specifications

- 6.6 Electrical Characteristics: Power Consumption

- 6.7 Electrical Characteristics: AC Specifications (Dual-Channel Mode)

- 6.8 Electrical Characteristics: AC Specifications (Single-Channel Mode)

- 6.9 Timing Requirements

- 6.10 Switching Characteristics

- 6.11 Typical Characteristics

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3

Feature Description

- 7.3.1 Device Comparison

- 7.3.2 Analog Inputs

- 7.3.3 ADC Core

- 7.3.4 Temperature Monitoring Diode

- 7.3.5 Timestamp

- 7.3.6 Clocking

- 7.3.7 Programmable FIR Filter (PFIR)

- 7.3.8

JESD204C Interface

- 7.3.8.1 Transport Layer

- 7.3.8.2 Scrambler

- 7.3.8.3 Link Layer

- 7.3.8.4 8B/10B Link Layer

- 7.3.8.5

64B/66B Link Layer

- 7.3.8.5.1 64B/66B Encoding

- 7.3.8.5.2 Multiblocks, Extended Multiblocks and the Local Extended Multiblock Clock (LEMC)

- 7.3.8.5.3 Block, Multiblock and Extended Multiblock Alignment using Sync Header

- 7.3.8.5.4 Initial Lane Alignment

- 7.3.8.5.5 Block, Multiblock and Extended Multiblock Alignment Monitoring

- 7.3.8.6 Physical Layer

- 7.3.8.7 JESD204C Enable

- 7.3.8.8 Multi-Device Synchronization and Deterministic Latency

- 7.3.8.9 Operation in Subclass 0 Systems

- 7.3.9 Alarm Monitoring

- 7.4

Device Functional Modes

- 7.4.1 Dual-Channel Mode

- 7.4.2 Single-Channel Mode (DES Mode)

- 7.4.3 Dual-Input Single-Channel Mode (DUAL DES Mode)

- 7.4.4 JESD204C Modes

- 7.4.5 Power-Down Modes

- 7.4.6 Test Modes

- 7.4.7 Calibration Modes and Trimming

- 7.4.8 Offset Calibration

- 7.4.9 Trimming

- 7.5 Programming

- 7.6 SPI Register Map

- 8 Application Information Disclaimer

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

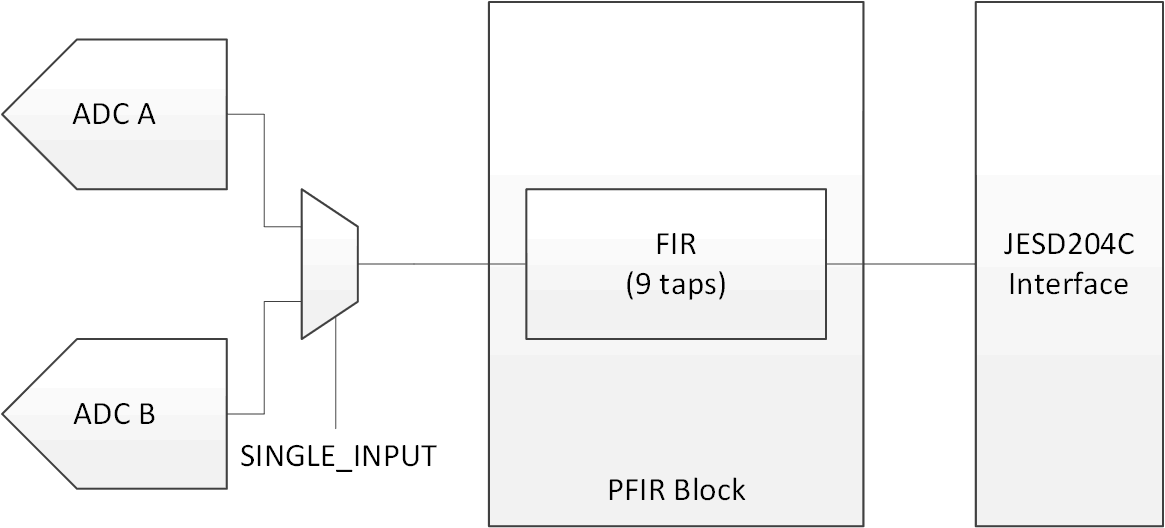

7.3.7.2 Single Channel Equalization

When the ADC is operating in single channel mode (based on the JMODE setting) then the PFIR filter can be set in single channel equalization mode. This mode allows frequency equalization of the ADC. The filter consists of 9 coefficients that can be independently set. The center tap of the filter has a resolution of 18 bits and the LSB has a weight of 2-16. The non-center taps have a resolution of 12-bits with programmable LSB weight of 2-10, 2-11, 2-12, 2-13, 2-14, 2-15 or 2-16. All non-center taps have the same LSB weight. The block diagram for single channel equalization is shown in Figure 7-5.

Figure 7-5 Single Channel Equalization PFIR Block Diagram

Figure 7-5 Single Channel Equalization PFIR Block Diagram